ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 19.06.2021

Просмотров: 139

Скачиваний: 1

В последней из рассматриваемых статических стратегий при первом выполнении любой команды условного перехода делается предсказание, что переход обязательно будет. Предсказания на последующее выполнение команды зависят от правильности начального предсказания. Стратегию можно считать статической только частично, поскольку она однозначно определяет исход команды лишь при первом ее выполнении. Точность прогноза в соответствии с данной стратегией выше, чем у всех предшествующих. Однако, при больших объемах программ вариант практически нереализуем из-за того, что нужно отслеживать слишком много команд условного перехода.

Динамическое предсказание переходов

В динамических стратегиях решение о наиболее вероятном исходе команды УП принимается в ходе вычислений, исходя из информации о предшествующих переходах (истории переходов), собираемой в процессе выполнения программы. В целом, динамические стратегии по сравнению со статическими обеспечивают более высокую точность предсказания.

Идея динамического предсказания переходов предполагает накопление информации об исходе предшествующих команд УП. История переходов фиксируется в форме таблицы, каждый элемент которой состоит из т битов. Нужный элемент таблицы указывается с помощью k-разрядной двоичной комбинации – шаблона (pattern). Этим объясняется общепринятое название таблицы предыстории переходов – таблица истории для шаблонов (PHT, Pattern History Table).

Для описания динамических схем предсказания переходов используются модели на основе автоматов Мура, при этом содержимое элементов РНТ трактуется как информация, отображающая текущее состояние автомата.

В большинстве известных процессоров используются двухразрядные автоматы Мура, на основе счетчиков, работающих с насыщением (m= 2). Логика предсказания переходов применительно к двухразрядным счетчикам известна как алгоритм Смита. Алгоритм предполагает четыре состояния счетчика:

00 — перехода не будет (сильное предсказание);

01 — перехода не будет (слабое предсказание);

-

— переход будет (слабое предсказание);

-

— переход будет (сильное предсказание).

Логику предсказания можно описать диаграммой состояний двухразрядного автомата A3 (рис. 5).

Рис. 5. Модель автомата Мура на счетчиках с насыщением

После определения способов учета истории переходов и логики предсказания необходимо остановиться на особенностях использования таблицы, в частности на том, какая информация выступает в качестве шаблона для доступа к РНТ и какого рода история фиксируется в элементах таблицы. Именно различия в способах использования РНТ определяют ту или иную стратегию предсказания. В качестве шаблонов для доступа к РНТ могут быть взяты:

адрес команды условного перехода;

регистр глобальной истории;

регистр локальной истории;

комбинация предшествующих вариантов.

Схема, где для доступа к РНТ выбран адрес команды условного перехода (содержимое счетчика команд), позволяет учитывать поведение каждой конкретной команды УП. При многократном выполнении большинства команд условного перехода наблюдается повторяемость исхода: переход либо, как правило, происходит, либо, как правило, не происходит (имеет место бимодальное распределение исходов). Индексация РНТ с помощью адреса команды УП дает возможность отделить первые от вторых и, соответственно, повысить точность предсказания. Каждой команде условного перехода в РНТ соответствует свой счетчик. Когда команда завершается переходом, содержимое счетчика увеличивается на единицу, а в противном случае – уменьшается на единицу (естественно, с соблюдением логики счета с насыщением). В качестве шаблона для поиска в РНТ служат младшие k-разрядов содержимого счетчика команд (рис. 6).

Рис. 6. Использование счетчика команд для формирования бита

предсказания перехода

При k-разрядном индексе таблица может содержать 2k элементов. Схема обеспечивает достаточно высокий процент правильных предсказаний для тех команд УП, которые в ходе вычислений выполняются многократно, например предназначены для управления циклом. В то же время в любой программе имеется достаточно много команд перехода, выполняемых лишь однократно или малое число раз. Исход для таких команд в значительной мере зависит от поведения предшествующих им команд УП, связь которых с рассматриваемой командой не столь очевидна. Иными словами, между исходами команд условного перехода в программе существует известная взаимосвязь, учет которой дает возможность повысить долю правильных предсказаний. Эта идея реализуется схемой с регистром глобальной истории.

Регистр глобальной истории (GHR, Global History Register) представляет собой l-разрядный сдвиговый регистр (рис. 7).

Рис. 7. Использование регистра глобальной истории для формирования бита предсказания перехода

После выполнения очередной команды условного перехода содержимое регистра сдвигается на один разряд, а в освободившуюся позицию заносится единица (если исходом команды был переход) или ноль (если перехода не было). Следовательно, кодовая комбинация в GHR (РГИ) отражает историю выполнения последних l команд условного перехода. Под индексирование массива предикторов (элементов механизма предсказания) выделяются k младших разряда GHR (чаще всего l = k). Каждой k-разрядной комбинации исходов последовательно выполнявшихся команд УП в массиве дескрипторов соответствует свой счетчик. Таким образом, счетчик РНТ определяется тем, какая комбинация исходов имела место в k предшествовавших командах перехода. Содержимое счетчика используется для предсказания исхода текущей команды перехода и впоследствии модифицируется по результату фактического выполнения команды.

Регистр локальной истории (LHR, Local History Register) по логике работы аналогичен регистру глобальной истории, но предназначен для фиксации последовательных исходов одной и той же команды УП. В схемах предсказания с LHR присутствует так называемая таблица локальной истории, представляющая собой массив регистров локальной истории (рис. 8).

Рис. 8. Использование регистров локальной истории для формирования бита предсказания перехода

Как и в схеме с адресом команды перехода, каждый счетчик в РНТ фиксирует историю исхода только одной команды УП, но базируясь на более детальных знаниях, отражающих к тому же и последовательность исходов.

Действие команды условного перехода зависит не только от результатов предшествующих выполнений данной команды, но и от исхода других команд перехода. Учет обоих факторов позволяет повысить точность предсказаний. С этой целью в ряде динамических методов предсказания шаблон для доступа к РНТ формируется путем объединения адреса команды перехода и содержимого GHR (либо LHR), при этом используется одна из двух операций: конкатенация (сцепление) и сложение по модулю 2 («исключающее ИЛИ»).

При конкатенации k-разрядный шаблон для обращения к РНТ образуется посредством взятия q младших битов из одного источника, к которым пристыковываются k—q младших разрядов, взятых из второго источника (рис. 9(а)).

а)

б)

Рис. 9. Комбинированные схемы формирования бита

предсказания перехода

Эффективность предсказания на основе подобного шаблона зависит от соотношения количества разрядов (q и k-q), выбранных от каждого из двух источников. Здесь многое определяется и характером программы.

Вариант со сложением по модулю 2 предполагает побитовое применение операции «Исключающее ИЛИ» к обоим источникам (рис. 9 (б)). В качестве шаблона используются k младших разрядов результата. Сформированный шаблон содержит больше полезной информации для предсказания, чем каждый из источников по отдельности.

Суперконвейерные процессоры

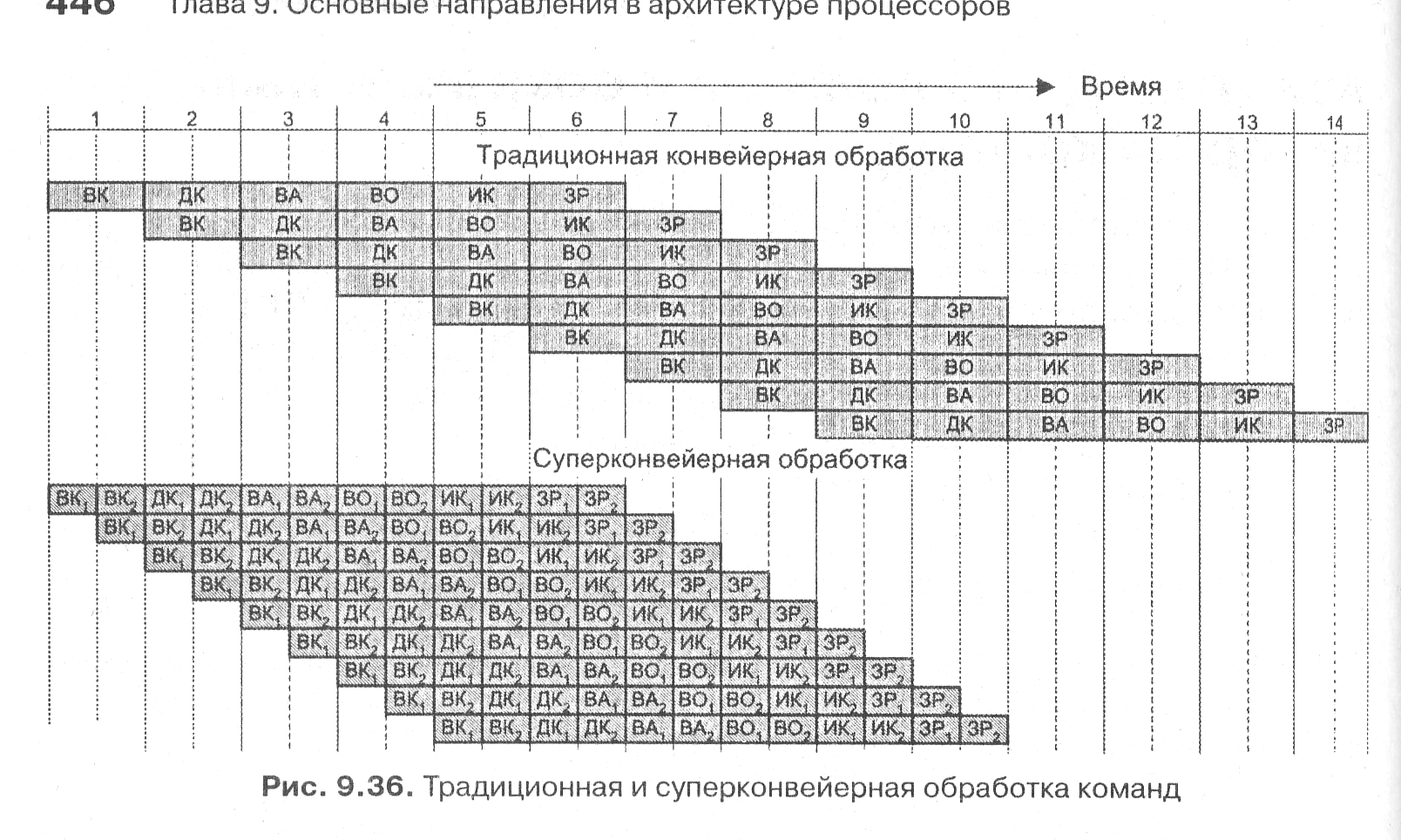

Эффективность конвейера находится в прямой зависимости от того, с какой частотой на его вход подаются объекты обработки. Добиться n-кратного увеличения темпа работы конвейера можно двумя путями:

разбиением каждой ступени конвейера на п «подступеней» при одновременном повышении тактовой частоты внутри конвейера также в п раз;

включением в состав процессора п конвейеров, работающих с перекрытием.

Первый из этих подходов получил название суперконвейеризация (рис. 10).

Каждая из шести ступеней стандартного конвейера разбита на две более простые подступени, обозначенные индексами 1 и 2. Выполнение операции в подступенях занимает половину тактового периода. Тактирование операций внутри конвейера производится с частотой, вдвое превышающей частоту «внешнего» тактирования конвейера, благодаря чему на каждой ступени конвейера можно в пределах одного «внешнего» тактового периода выполнить две команды.

Рис. 14. Принцип работы сурепконвейера

В сущности, суперконвейеризация сводится к увеличению количества ступеней конвейера, как за счет добавления новых ступеней, так и путем дробления имеющихся ступеней на несколько простых подступеней. Главное требование — возможность реализации операции в каждой подступени наиболее простыми техническими средствами, а значит, с минимальными затратами времени. Вторым, не менее важным, условием является одинаковость задержки во всех подступенях.

Критерием для причисления процессора к суперконвейерным служит число ступеней в конвейере команд. К суперконвейерным относят процессоры, где таких ступеней больше шести (табл.1).

Таблица 1. Длина конвейера команд в популярных микропроцессорах

-

Тип микропроцессора

Количество ступеней в конвейере команд

MIPS R4400

8

Ultra SPARC I

9

Pentium III

10

Itanium

10

Ultra SPARC III

14

Pentium 4

20

Выигрыш, достигаемый за счет суперконвейеризации, на практике может оказаться лишь умозрительным. Удлинение конвейера ведет не только к усугублению проблем, характерных для любого конвейера, но и возникновению дополнительных сложностей. В длинном конвейере возрастает вероятность конфликтов. Дороже встает ошибка предсказания перехода – приходится очищать большее число ступеней конвейера, на что требуется больше времени. Усложняется логика взаимодействия ступеней конвейера. Тем не менее, создателям ВМ удается успешно справляться с большинством из перечисленных проблем, свидетельством чего служит неуклонное возрастание числа ступеней в конвейерах команд современных процессоров.

2. Суперскалярные процессоры.

Один из наиболее эффективных подходов архитектурных решений повышения производительности ВМ заключается во введении в вычислительный процесс различных уровней параллелизма. Конвейер команд — типичный пример такого подхода. Тем же целям служат и арифметические конвейеры, где конвейеризации подвергается процесс выполнения арифметических операций. Дополнительный уровень параллелизма реализуется в векторных и матричных процессорах, но только при обработке многокомпонентных операндов типа векторов и массивов. Здесь высокое быстродействие достигается за счет одновременной обработки всех компонентов вектора или массива, однако подобные операнды характерны лишь для достаточно узкого круга решаемых задач. Основной объем вычислительной нагрузки обычно приходится на скалярные вычисления, то есть на обработку одиночных операндов, таких, например, как целые числа. Для подобных вычислений дополнительный параллелизм реализуется значительно сложнее, но тем не менее возможен и примером могут служить суперскалярные процессоры.

Суперскалярным (этот термин впервые был использован в 1987 году) называется центральный процессор (ЦП), который одновременно выполняет более чем одну скалярную команду. Это достигается за счет включения в состав ЦП нескольких самостоятельных функциональных (исполнительных) блоков, каждый из которых отвечает за свой класс операций и может присутствовать в процессоре в нескольких экземплярах. Так, в микропроцессоре Pentium III блоки целочисленной арифметики и операций с плавающей точкой дублированы, а в микропроцессорах Pentium 4 и Athlon — троированы. Структура типичного суперскалярного процессора показана на рис. 11.

Рис. 11. Структура суперскалярного процессора

Процессор включает в себя шесть блоков:

выборки команд (извлекает команды из основной памяти через кэш-память команд. Этот блок хранит несколько значений счетчика команд и обрабатывает команды условного перехода);

декодирования команд (расшифровывает код операции, содержащийся в извлеченных из кэш-памяти командах. В некоторых суперскалярных процессорах, например в микропроцессорах фирмы Intel, блоки выборки и декодирования совмещены);

диспетчеризации команд;

распределения команд по функциональным блокам;

блок исполнения;

блок обновления состояния.

Блоки диспетчеризации и распределения взаимодействуют между собой и в совокупности играют в суперскалярном процессоре роль контроллера трафика. Оба блока хранят очереди декодированных команд. Очередь блока распределения рассредоточивается по несколько самостоятельным буферам — накопителям команд или схемам резервирования (reservation station), — предназначенным для хранения команд, которые уже декодированы, но еще не выполнены. Каждый накопитель команд связан со своим функциональным блоком (ФБ), поэтому число накопителей обычно равно числу ФБ, но если в процессоре используется несколько однотипных ФБ, то им придается общий накопитель. По отношению к блоку диспетчеризации накопители команд выступают в роли виртуальных функциональных устройств.

Блок исполнения состоит из набора функциональных блоков. Примерами ФБ могут служить целочисленные операционные блоки, блоки умножения и сложения с плавающей запятой, блок доступа к памяти. Когда исполнение команды завершается, ее результат записывается и анализируется блоком обновления состояния, который обеспечивает учет полученного результата теми командами в очередях распределения, где этот результат выступает в качестве одного из операндов.

Как было отмечено ранее, суперскалярность предполагает параллельную работу максимального числа исполнительных блоков, что возможно лишь при одновременном выполнении нескольких скалярных команд. Последнее условие хорошо сочетается с конвейерной обработкой, при этом желательно, чтобы в суперскалярном процессоре было несколько конвейеров, например два или три.

Подобный подход реализован в микропроцессоре Intel Pentium, где имеются два конвейера (рис.12).

Рис. 12. Организация параллельных конвейеров

Суперскалярный конвейер, обеспечивает в каждом тактовом периоде одновременную обработку двух команд.

Более интегрированный подход к построению суперскалярного конвейера показан на рис. 13.

Рис. 3. Интегрированный параллельный конвейер

Здесь блок выборки (ВК) извлекает из памяти более одной команды и передает их через ступени декодирования команды и вычисления адресов операндов в блок выборки операндов (ВО). Когда операнды становятся доступными, команды распределяются по соответствующим исполнительным блокам. причем операции «Чтение», «Запись» и «Переход» реализуются самостоятельными исполнительными блоками. Подобная форма суперскалярного процессора используется в микропроцессорах фирмы Intel, а форма с тремя конвейерами – в микропроцессоре Athlon фирмы AMD.