Добавлен: 20.10.2018

Просмотров: 2009

Скачиваний: 14

Оглавление

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ SIMPLE COMPUTER .................................. 3

Лабораторная работа 1. Организация современных персональных компьютеров .................... 6

Лабораторная работа 3. Консоль управления моделью Simple Computer. Текстовая часть. ... 8

Лабораторная работа 6. Подсистема прерываний ЭВМ. Сигналы и их обработка. ................. 12

Лабораторная работа 7. Устройство хранения данных на жестких магнитных дисках. ......... 12

ВВЕДЕНИЕ

В рамках выполнения лабораторных работ и курсового проектирования необходимо разрабо-

тать программную модель простейшей вычислительной машины Simple Computer. Архитектура

Simple Computer представлена ниже.

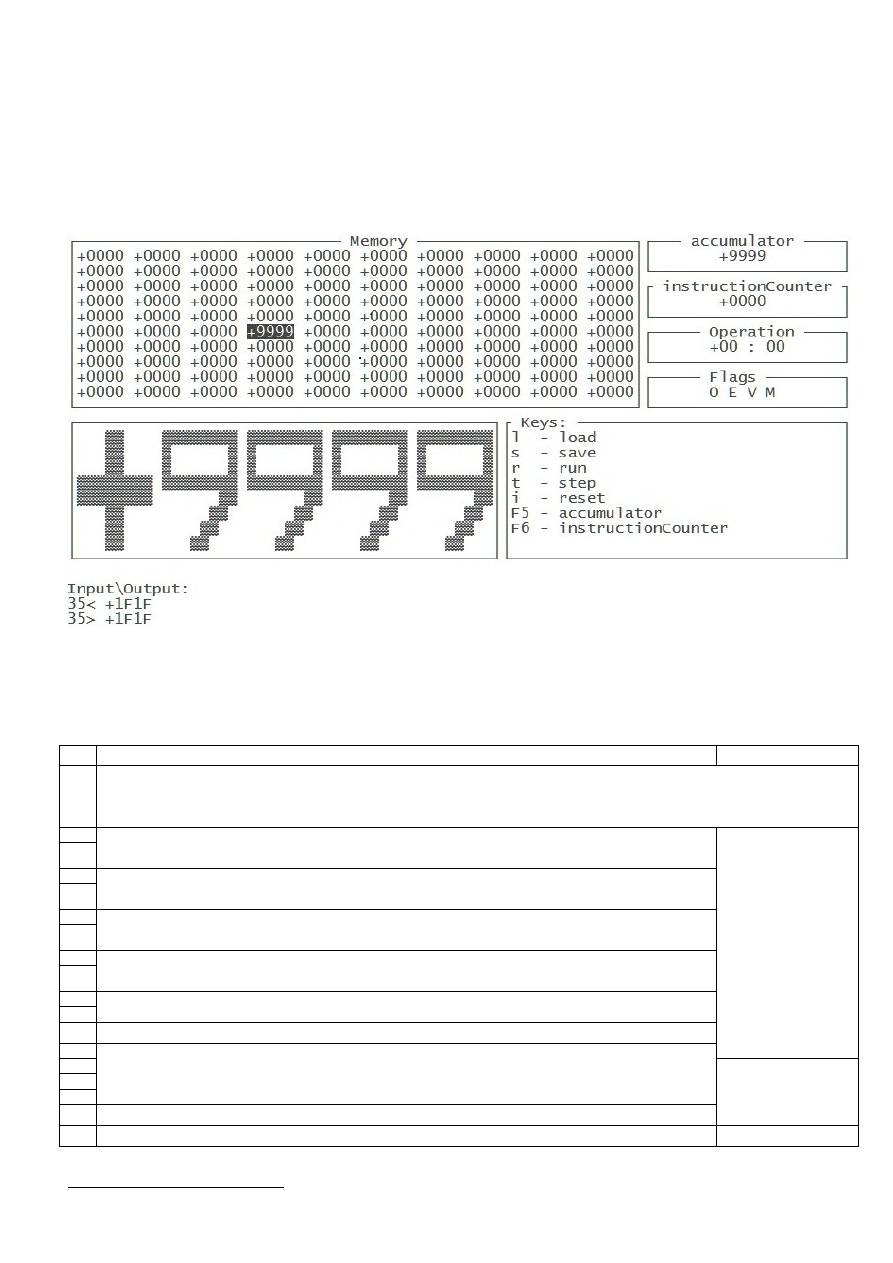

Для управления моделью (определения начальных состояний узлов Simple Computer, запуска

программ на выполнения, отражения хода выполнения программ) требуется создать консоль (см. ри-

сунок 1). Необходимо реализовать трансляторы с языков Simple Assembler и Simple Basic

1

для про-

граммирования Simple Computer.

Рисунок 1 – интерфейс консоли управления моделью Simple Computer

КАЛЕНДАРНЫЙ ПЛАН ВЫПОЛНЕНИЯ ЛАБОРАТОРНЫХ РАБОТ И

КУРСОВОГО ПРОЕКТИРОВАНИЯ

Нед

Лабораторные работы

Курсовая работа

1

Введение в курс. Знакомство со средой разработки в GNU/Linux. Постановка задачи на лабораторные

работы и курсовое проектирование. Лабораторная работа 1. Организация современных персональных

компьютеров

2

Лабораторная работа 2. Разработка библиотеки mySimpleComputer. Оперативная

память, регистр флагов, декодирование операций.

Вы

по

лн

ение

к

ур

со

во

го

про

ек

тир

о

ван

ия

3

4

Лабораторная работа 3. Консоль управления моделью Simple Computer. Текстовая

часть.

5

6

Лабораторная работа 4. Консоль управления моделью Simple Computer. Псевдогра-

фика. «Большие символы».

7

8

Лабораторная работа 5. Консоль управления моделью Simple Computer. Клавиатура.

Обработка нажатия клавиш. Неканонический режим работы терминала

9

10

Лабораторная работа 6. Подсистема прерываний ЭВМ. Сигналы и их обработка.

11

12

Защита рефератов

13

Лабораторная работа 7. Устройство хранения данных на жестких магнитных дисках.

14

Защита курсовой

работы

15

16

17

Сдача долгов

18

Сдача долгов

1

Транслятор с языка Simple Basic разрабатывают студенты, претендующие на отличную оценку по курсовой работы и

«автомат» на экзамене.

АРХИТЕКТУРА ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ SIMPLE COMPUTER

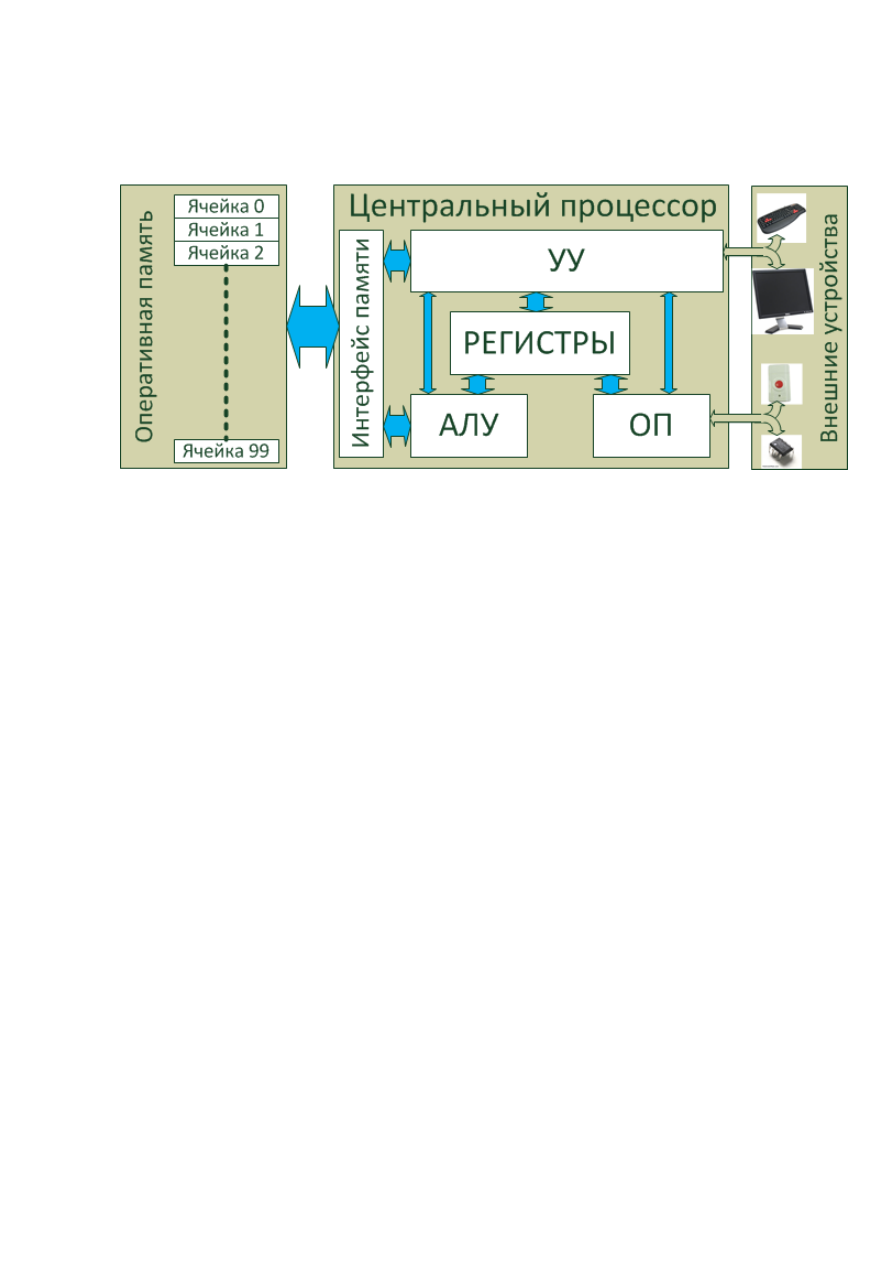

Архитектура Simple Computer представлена на рисунке 2 и включает следующие функциональ-

ные блоки:

оперативную память;

внешние устройства;

центральный процессор.

Рисунок 2 – Архитектура вычислительной машины Simple Computer

Оперативная память

Оперативная память – это часть Simple Computer, где хранятся программа и данные. Память со-

стоит из ячеек (массив), каждая из которых хранит 15 двоичных разрядов. Ячейка – минимальная

единица, к которой можно обращаться при доступе к памяти. Все ячейки последовательно пронуме-

рованы целыми числами. Номер ячейки является еѐ адресом и задается 7-миразрядным числом.

Предполагаем, что Simple Computer оборудован памятью из 100 ячеек (с адресами от 0 до 99

10

).

Внешние устройства

Внешние устройства включают: клавиатуру и монитор, используемые для взаимодействия с

пользователем, системный таймер, задающий такты работы Simple Computer и кнопку «Reset», поз-

воляющую сбросить Simple Computer в исходное состояние.

Центральный процессор

Выполнение программ осуществляется центральным процессором Simple Computer. Процессор

состоит из следующих функциональных блоков:

регистры (аккумулятор, счетчик команд, регистр флагов);

арифметико-логическое устройство (АЛУ);

управляющее устройство (УУ);

обработчик прерываний от внешних устройств (ОП);

интерфейс доступа к оперативной памяти.

Регистры являются внутренней памятью процессора. Центральный процессор Simple Computer

имеет: аккумулятор, используемый для временного хранения данных и результатов операций, счет-

чик команд, указывающий на адрес ячейки памяти, в которой хранится текущая выполняемая ко-

манда и регистр флагов, сигнализирующий об определѐнных событиях. Аккумулятор имеет разряд-

ность 15 бит, счетчика команд – 7 бит. Регистр флагов содержит 5 разрядов: переполнение при вы-

полнении операции, ошибка деления на 0, ошибка выхода за границы памяти, игнорирование такто-

вых импульсов, указана неверная команда.

Арифметико-логическое устройство (англ. arithmetic and logic unit, ALU) — блок процессора, ко-

торый служит для выполнения логических и арифметических преобразований над данными. В каче-

стве данных могут использоваться значения, находящиеся в аккумуляторе, заданные в операнде ко-

манды или хранящиеся в оперативной памяти. Результат выполнения операции сохраняется в акку-

муляторе или может помещаться в оперативную память. В ходе выполнения операций АЛУ устанав-

ливает значения флагов «деление на 0» и «переполнение».

Управляющее устройство (англ. control unit, CU) координирует работу центрального процессора.

По сути, именно это устройство отвечает за выполнение программы, записанной в оперативной па-

мяти. В его функции входит: чтение текущей команды из памяти, еѐ декодирование, передача номе-

ра команды и операнда в АЛУ, определение следующей выполняемой команды и реализации взаи-

модействий с клавиатурой и монитором. Выбор очередной команды из оперативной памяти произ-

водится по сигналу от системного таймера. Если установлен флаг «игнорирование тактовых импуль-

сов», то эти сигналы устройством управления игнорируются. В ходе выполнения операций устрой-

ство управления устанавливает значения флагов «указана неверная команда» и «игнорирование так-

товых импульсов».

Обработчик прерываний реагирует на сигналы от системного таймера и кнопки «Reset». При по-

ступлении сигнала от кнопки «Reset» состояние процессора сбрасывается в начальное (значения всех

регистров обнуляется и устанавливается флаг «игнорирование сигналов от таймера»). При поступ-

лении сигнала от системного таймера, работать начинает устройство управления.

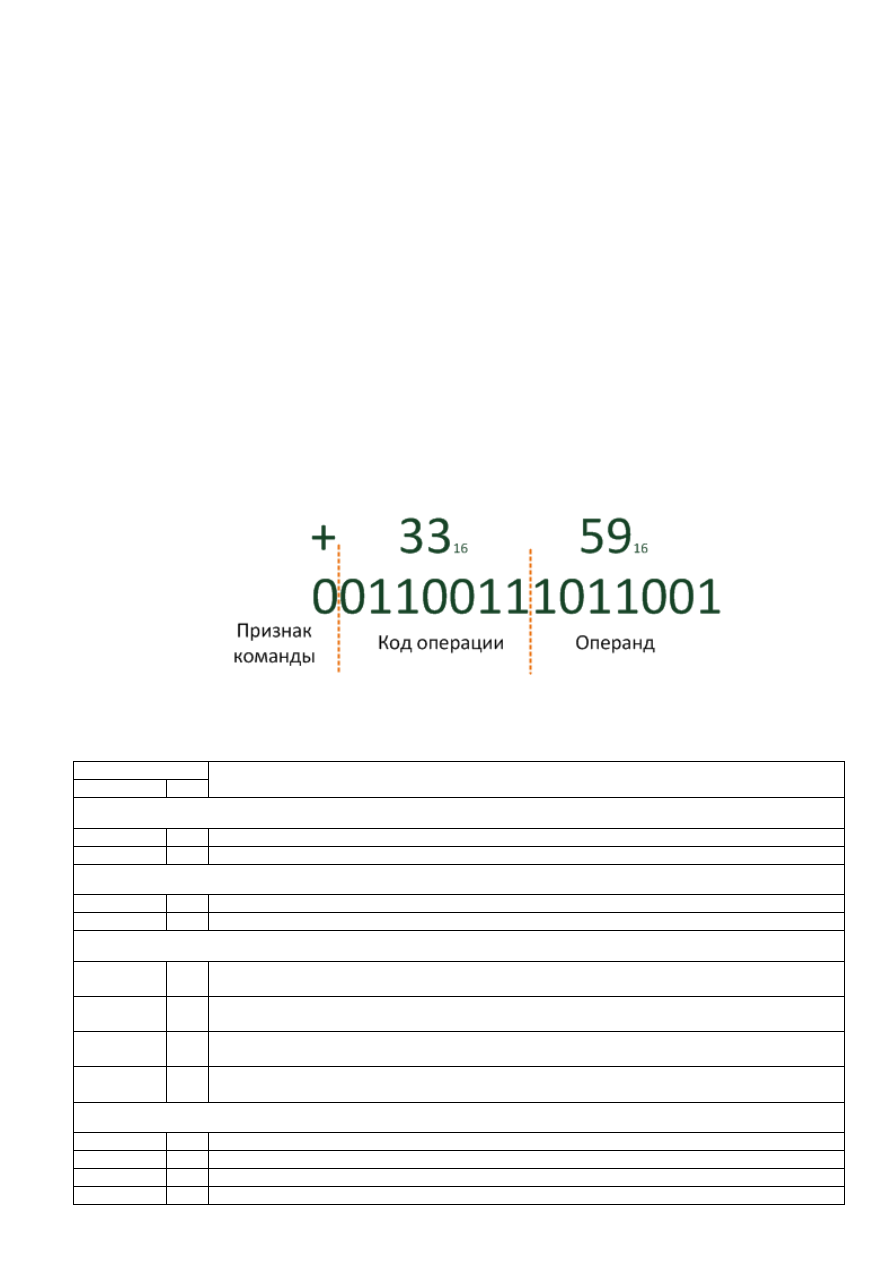

Система команд Simple Computer

Получив текущую команду из оперативной памяти, устройство управления декодирует еѐ с це-

лью определить номер функции, которую надо выполнить и операнд. Формат команды следующий

(см. рисунок 3): старший разряд содержит признак команды (0 – команда), разряды с 8 по 14 опреде-

ляют код операции, младшие 7 разрядов содержат операнд. Коды операций, их назначение и обозна-

чение в Simple Assembler и приведены в таблице 1.

Рисунок 3 – Формат команды центрального процессора Simple Computer

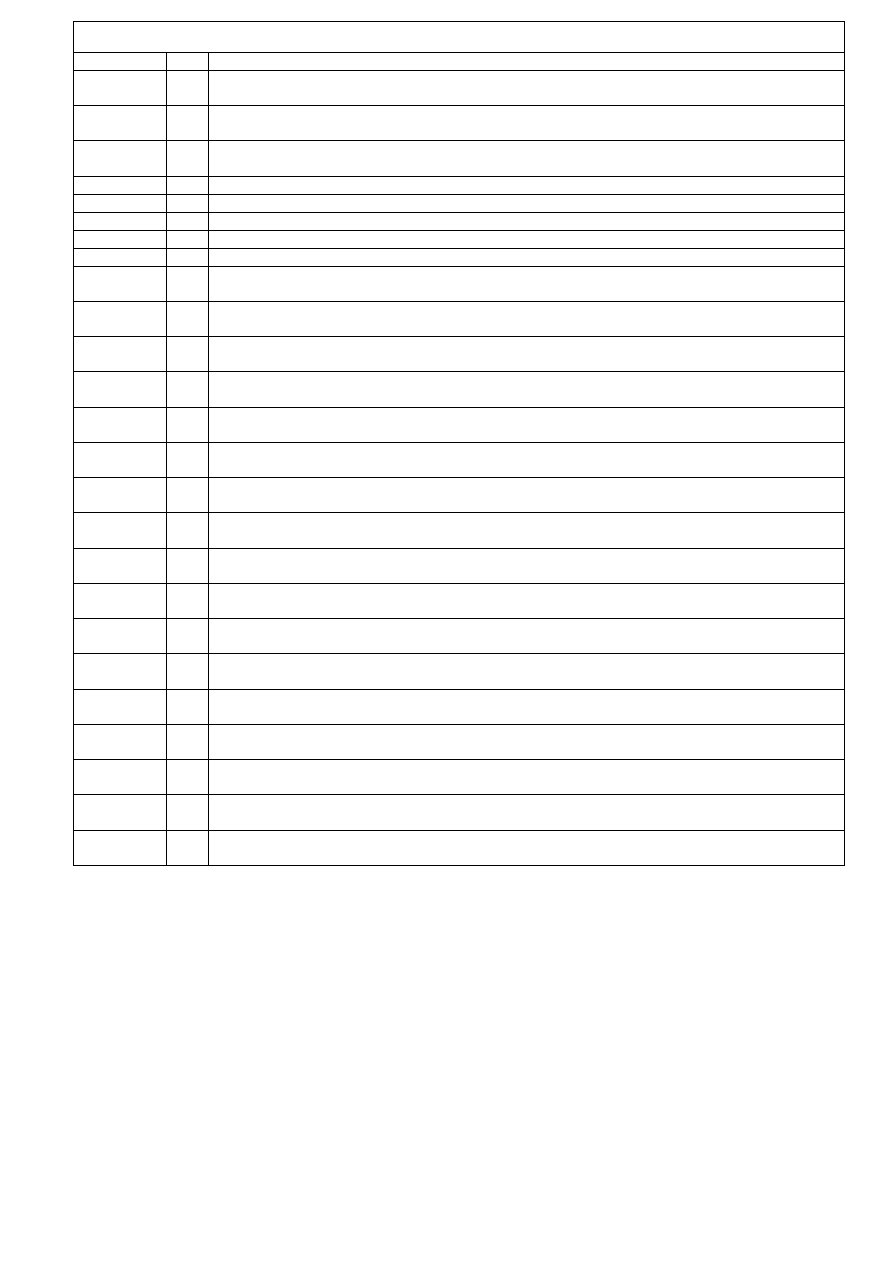

Таблица 1. Команды центрального процессора Simple Computer

Операция

Значение

Обозначение

Код

Операции ввода/вывода

READ

10

Ввод с терминала в указанную ячейку памяти с контролем переполнения

WRITE

11

Вывод на терминал значение указанной ячейки памяти

Операции загрузки/выгрузки в аккумулятор

LOAD

20

Загрузка в аккумулятор значения из указанного адреса памяти

STORE

21

Выгружает значение из аккумулятора по указанному адресу памяти

Арифметические операции

ADD

30

Выполняет сложение слова в аккумуляторе и слова из указанной ячейки памяти

(результат в аккумуляторе)

SUB

31

Вычитает из слова в аккумуляторе слово из указанной ячейки памяти

(результат в аккумуляторе)

DIVIDE

32

Выполняет деление слова в аккумуляторе на слово из указанной ячейки памяти

(результат в аккумуляторе)

MUL

33

Вычисляет произведение слова в аккумуляторе на слово из указанной ячейки памяти

(результат в аккумуляторе)

Операции передачи управления

JUMP

40

Переход к указанному адресу памяти

JNEG

41

Переход к указанному адресу памяти, если в аккумуляторе находится отрицательное число

JZ

42

Переход к указанному адресу памяти, если в аккумуляторе находится ноль

HALT

43

Останов, выполняется при завершении работы программы

Пользовательские функции

NOT

51

Двоичная инверсия слова в аккумуляторе и занесение результата в указанную ячейку памяти

AND

52

Логическая операция И между содержимым аккумулятора и словом по указанному адресу

(результат в аккумуляторе)

OR

53

Логическая операция ИЛИ между содержимым аккумулятора и словом по указанному адресу

(результат в аккумуляторе)

XOR

54

Логическая операция исключающее ИЛИ между содержимым аккумулятора и словом по ука-

занному адресу (результат в аккумуляторе)

JNS

55

Переход к указанному адресу памяти, если в аккумуляторе находится положительное число

JC

56

Переход к указанному адресу памяти, если при сложении произошло переполнение

JNC

57

Переход к указанному адресу памяти, если при сложении не произошло переполнение

JP

58

Переход к указанному адресу памяти, если результат предыдущей операции четный

JNP

59

Переход к указанному адресу памяти, если результат предыдущей операции нечетный

CHL

60

Логический двоичный сдвиг содержимого указанной ячейки памяти влево

(результат в аккумуляторе)

SHR

61

Логический двоичный сдвиг содержимого указанной ячейки памяти вправо

(результат в аккумуляторе)

RCL

62

Циклический двоичный сдвиг содержимого указанной ячейки памяти влево

(результат в аккумуляторе)

RCR

63

Циклический двоичный сдвиг содержимого указанной ячейки памяти вправо

(результат в аккумуляторе)

NEG

64

Получение дополнительного кода содержимого указанной ячейки памяти

(результат в аккумуляторе)

ADDC

65

Сложение содержимого указанной ячейки памяти с ячейкой памяти, адрес которой находится в

аккумуляторе (результат в аккумуляторе)

SUBC

66

Вычитание из содержимого указанной ячейки памяти содержимого ячейки памяти, адрес кото-

рой находится в аккумуляторе (результат в аккумуляторе)

LOGLC

67

Логический двоичный сдвиг содержимого указанного участка памяти влево на количество раз-

рядов указанное в аккумуляторе (результат в аккумуляторе)

LOGRC

68

Логический двоичный сдвиг содержимого указанного участка памяти вправо на количество

разрядов указанное в аккумуляторе (результат в аккумуляторе)

RCCL

69

Циклический двоичный сдвиг содержимого указанного участка памяти влево на количество

разрядов указанное в аккумуляторе (результат в аккумуляторе)

RCCR

70

Циклический двоичный сдвиг содержимого указанного участка памяти вправо на количество

разрядов указанное в аккумуляторе (результат в аккумуляторе)

MOVA

71

Перемещение содержимого указанной ячейки памяти в ячейку, адрес которой указан в аккуму-

ляторе

MOVR

72

Перемещение содержимого ячейки памяти, адрес которой содержится в аккумуляторе в указан-

ную ячейку памяти.

MOVСA

73

Перемещение содержимого указанной ячейки памяти в ячейку памяти, адрес которой находит-

ся в ячейке памяти, на которую указывает значение аккумулятора

MOVСR

74

Перемещение в указанный участок памяти содержимого участка памяти, адрес которого нахо-

дится в участке памяти указанном в аккумуляторе

ADDC

75

Сложение содержимого указанной ячейки памяти с ячейкой памяти, адрес которой находится в

ячейке памяти, указанной в аккумуляторе (результат в аккумуляторе)

SUBC

76

Вычитание из содержимого указанной ячейки памяти содержимого ячейки памяти, адрес кото-

рой находится в ячейке памяти, указанной в аккумуляторе (результат в аккумуляторе)

Выполнение команд центральным процессором Simple Computer

Команды выполняются последовательно. Адрес ячейки памяти, в которой находится текущая

выполняемая команда, задается в регистре «Счетчик команд». Устройство управления запрашивает

содержимое указанной ячейки памяти и декодирует его согласно используемому формату команд.

Получив код операции, устройство управления определяет, является ли эта операция арифметико-

логической. Если да, то выполнение операции передается в АЛУ. В противном случае операция вы-

полняется устройством управления. Процедура выполняется до тех пор, пока флаг «останов» не бу-

дет равен 1.

Консоль управления

Интерфейс консоли управления представлен на рисунке 1. Он содержит следующие области:

―Memory‖ – содержимое оперативной памяти Simple Computer.

―Accumulator‖ – значение, находящееся в аккумуляторе;

―instructionCounter‖ – значение регистра «счетчик команд»;

―Operation‖ – результат декодирования операции;