ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 26.10.2023

Просмотров: 619

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

АРХИТЕКТУРЫ, ХАРАКТЕРИСТИКИ, КЛАССИФИКАЦИЯ ЭВМ

3. ФУНКЦИОНАЛЬНАЯ И СТРУКТУРНАЯ

4. ПРИНЦИПЫ ОРГАНИЗАЦИИ ПОДСИСТЕМЫ ПАМЯТИ ЭВМ И ВС

ОРГАНИЗАЦИЯ СИСТЕМНОГО ИНТЕРФЕЙСА И ВВОДА/ВЫВОДА ИНФОРМАЦИИ

МНОГОПРОЦЕССОРНЫЕ И МНОГОМАШИННЫЕ ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ

tизд =tз + tв.

-

Глубина прерывания – максимальное число программ, которые могут прерывать друг друга. На рис. 2.32 показаны процессы прерыва- ния в системах с различной глубиной прерывания (предполагается, что приоритет каждого последующего запроса выше предыдущего). Если после перехода к прерывающей программе и вплоть до ее окончания прием запросов прекращается, то говорят, что система имеет глубину прерывания, равную 1 (относительная дисциплина обслуживания).

Запросы прерывания

Запросы прерыванияВыполнение прерывающих программ с

n = 1

Выполнение прерывающих

1 2 3

1

2 3

3

t

Относительная

t дисциплина обслуживания

программ с 2

n = 3

1

2

Абсолютная

1 дисциплина

t обслуживания

Рис. 2.32. Процессы прерывания с различной глубиной прерывания и дисциплиной обслуживания

Глубина равна n, если допускается последовательное прерывание до n прерывающих программ (абсолютная дисциплина обслуживания). Глубина прерывания обычно совпадает с числом уровней приоритета в системе прерывания. Система с большим значением глубины преры- вания обеспечивает более быструю реакцию на срочные запросы.

Если запрос окажется не обслуженным к моменту прихода нового запроса от того же источника, то возникает так называемое насыщение системы прерывания. В этом случае предыдущий запрос от данного источника будет машинально утерян, что недопустимо. Существуют специальные методы борьбы с этой ситуацией.

Программно-управляемый приоритет прерывающих программ

Относительная степень важности программ, их частота повторения, относительная степень срочности в ходе вычислительного процесса мо- гут меняться, требуя установления новых

приоритетных отношений. Поэтому во многих случаях приоритет между прерывающими програм- мами не может быть зафиксирован раз и навсегда. Необходимо иметь возможность изменять, по мере необходимости, приоритетные соотно- шения программным путем. Приоритет между прерывающими про- граммами должен быть динамичным, т.е. программно управляемым.

В ЭВМ широко применяется способ маскирования прерываний.

Существуюбт два специальных внешних сигнала среди входных сигналов процессора, при помощи которых можно прервать выполнение текущей программы и тем самым переключить работу центрального процессора. Это сигналы NMI (Non Mascable Interrupt, немаскируемое прерывание) INTR (INTerrupt Request, запрос на прерывание).

Соответственно внешние прерывания подразделяются на два вида: немаскируемые и маскируемые.

Маска прерывания представляет собой двоичный код, разряды которого поставлены в соответствие запросам или классам (уровням) прерывания. Маска загружается командой программы в регистр маски (рис. 2.33).

Запросы прерываний

РгЗП

РгЗП&

&

&

.

.

INTR

Схема выделения незамаски- рованного запроса

с высшим приоритетом

Код приоритет- ного запроса

РгМ

РгМКод маски

Рис. 2.33. Маскирование прерываний

Состояние 1 в данном разряде регистра

маски (РгМ) разрешает, а состояние 0 запрещает (маскирует) прерывание текущей программы от соответствующего запроса в регистре запросов прерываний (РгЗП). Таким образом, программа, изменяя маску в регистре маски, может устанавливать произвольные приоритетные соотношения между про- граммами без перекоммутации линий, по которым поступают запросы прерывания. Каждая прерывающая программа может установить свою маску. При формировании маски 1 устанавливаются в разряды, соответ- ствующие запросам (прерывающим программам) с более высоким, чем у данной программы, приоритетом. Схемы И выделяют поступившие незамаскированные запросы прерывания, из которых специальная схема выделяет наиболее приоритетный запрос, формирует код его номера и вырабатывает основной сигнал прерывания (INTR).

С замаскированным запросом, в зависимости от причины прерыва- ния, поступают двояким образом: или он игнорируется, или запомина- ется, с тем, чтобы осуществить затребованные действия, когда запрет будет снят. Например, если прерывание вызвано окончанием операции в ПУ, то его следует, как правило, запомнить, так как иначе ЭВМ оста- нется неосведомленной о том, что ПУ освободилось.

Возможность прерывания программ – важное архитектурное свой- ство ЭВМ, позволяющее эффективно использовать производительность процессора при наличии нескольких процессов, протекающих парал- лельно во времени, требующих в произвольные моменты времени управ- ления и обслуживания со стороны процессора.

Чтобы ЭВМ могла, не требуя больших усилий от программиста, реализовывать с высоким быстродействием прерывания программ, ма- шине необходимо придать соответствующие аппаратурные и программ- ные средства, совокупность которых получила название системы пре- рывания программ. В качестве аппаратных средств используется кон- троллер

прерывания (блок прерывания).

Основными функциями системы прерывания являются:

-

запоминание состояния прерываемой программы и осуществление перехода к прерывающей программе; -

восстановление состояния прерванной программы и возврат к ней.

При наличии нескольких источников запросов прерывания между ними должны быть установлены приоритетные соотношения, опреде- ляющие, какой из нескольких поступивших запросов подлежит обра- ботке в первую очередь, и устанавливающие: имеет право или нет

данный запрос (прерывающая программа) прерывать ту или иную про- грамму.

Структура аппаратных средств системы прерывания

В процессе эволюции компьютеров на базе Intel, эволюционирова- ла и архитектура обработки прерываний. Изначально контроллер пре- рываний PIC (Programmable Interrupt Controller) состоял из одной микросхемы Intel 8259 c 8-ю входными линиями от устройств и двумя выходными сигнальными линиями к процессору — INT и NMI. Кроме того контроллер прерываний связан с процессором через шину. Кон- троллер вызывает внимание процессора выставлением сигнала INT или NMI, а номер возникшего прерывания передает через шину. Кроме того, через шину процессор может осуществлять управление контроллером. На физическом уровне различают даже несколько шин, через которые связаны контроллер с процессором.

Восемь входных линий контроллера прерываний позволяли назна- чать устройствам 8 разных аппаратных прерываний. Позже этого оказа- лось не достаточно. Чтобы расширить количество входных линий в IRQ два одинаковых контроллера связали каскадно. Выходная сигнальная линия дополнительного контроллера завязывалась на входную линию главного контроллера с номером 2. Таким образом, для устройств в та- кой совместной схеме осталось 15

входных линий.

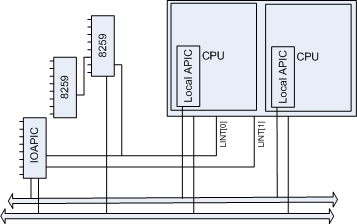

С появлением многоядерных систем потребовались дополнитель- ные контроллеры прерываний. Интелу потребовалось решать две зада- чи. Во-первых, снова появилась нехватка входных линий прерываний. Во-вторых, потребовался механизм межпроцессорной синхронизации в многопроцессорных системах. На смену PIC, Intel разработал APIC.

APIC (Advanced Programmable Interrupt Controller) — улуч- шенный программируемый контроллер прерываний.

Преимущества расширенного контроллера прерываний:

-

возможность реализации межпроцессорных прерываний — сигналов от одного процессора другому; -

поддержка до 256 входов IRQ, в отличие от 1 5 в классической архи- тектуре; -

крайне быстрый доступ к регистрам текущего приоритета прерыва- ния и подтверждения прерывания.

APIC поддерживался в ОС Windows, начиная с Windows NT 4.0. APIC состоит из двух модулей:

-

LOCAL APIC — располагается в ядре процессора, если система мно- гоядерна - в каждом ядре; -

I/O APIC — контроллер, расположенный на системной плате, обыч- но как часть микросхем обрамления.

На примере структуры соединения контроллеров прерывания (рис. 2.34) внутрь каждого ядра процессора поместили контроллер с именем Local APIC, а в дополнение к 2-м контроллерам 8259, добавили IOAPIC. Появилась дополнительная шина APIC, связывающая между собой IOAPIC и LocalAPIC. Появились линии синхронизации процессоров.

Шина APIС

Шина APIСШина синхронизации

Рис. 2.34. Пример структуры соединия контроллеров прерывания

В настоящий момент наблюдается тенденция к отказу от IO APIC, как и проводников IRQ, и переходу на Message Signaled Interrupts.