ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 26.10.2023

Просмотров: 668

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

АРХИТЕКТУРЫ, ХАРАКТЕРИСТИКИ, КЛАССИФИКАЦИЯ ЭВМ

3. ФУНКЦИОНАЛЬНАЯ И СТРУКТУРНАЯ

4. ПРИНЦИПЫ ОРГАНИЗАЦИИ ПОДСИСТЕМЫ ПАМЯТИ ЭВМ И ВС

ОРГАНИЗАЦИЯ СИСТЕМНОГО ИНТЕРФЕЙСА И ВВОДА/ВЫВОДА ИНФОРМАЦИИ

МНОГОПРОЦЕССОРНЫЕ И МНОГОМАШИННЫЕ ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ

ключать неактивные ядра, переводя их в состояние глубокого сна, в кото- ром энергопотребление ядра приближается к нулевой отметке.

Главное преимущество этой технологии состоит в том, что управ- ление питанием отдельных ядер осуществляется целиком внутри про- цессора и не требует усложнения схемы конвертера питания на мате- ринской плате.

Что же касается общих для всех ядер процессорных блоков, таких как контроллеры памяти и интерфейса QPI, то они переходят в энерго-

сберегающие состояния, когда в состоянии сна находятся все процес- сорные ядра.

Наличие в процессоре контроллера, способного независимо управ- лять состоянием процессорных ядер, позволило Intel реализовать и еще одну интересную технологию, получившую название Turbo Boost Technology. Эта технология вводит понятие турбо-режима, в котором отдельные ядра могут работать на частоте, превосходящей номиналь- ную, т.е. разгоняться. Основной принцип Turbo Boost Technology состо- ит в том, что при переходе отдельных ядер в энергосберегающие состо- яния снижается общее энергопотребление и тепловыделение процессо- ра, а это, в свою очередь, позволяет нарастить частоты остальных ядер без риска выйти за установленные рамки TDP.

Фактически прообраз этой технологии уже был реализован в двухъядерных мобильных процессорах поколения Penryn, однако в Nehalem её развитие продвинулось еще дальше. В новых процессорах, если нет риска выйти за границу типичного энергопотребления и тепло- выделения, PCU может повышать частоты процессорных ядер на один шаг выше номинала (133 МГц). Это может происходить, например, при слабо распараллеленной нагрузке, когда часть ядер находится в состоя- нии простоя. Более того, при

соблюдении описанных условий, частота одного из ядер может быть увеличена и на два шага выше номинала (266 МГц).

Следует отметить, что необходимым условием включения турбо- режима вовсе не является переход одного или нескольких ядер в энер- госберегающее состояние. Это всего лишь один из возможных сценари- ев. Так как PCU имеет все средства для получения данных о фактиче- ском состоянии процессорных ядер, турбо-режим может задействовать- ся и в тех случаях, когда все ядра работают, но нагрузка на часть из них невелика.

Большим преимуществом Turbo Boost Technology является ее пол- ная прозрачность для операционной системы. Эта технология реализо- вана исключительно аппаратными средствами и не требует использова- ния никаких программных утилит для своей активации.

Основываясь на ошеломляющем успехе 45 нм производственного процесса с диэлектриками high-k и транзисторами с металлическими за-

творами, корпорация Intel в конце 2009 г. запустила 32 нм производ- ственную технологию, в которой используются диэлектрики high-k и транзисторы с металлическими затворами второго поколения. Эта технология стала основой для новой 32 нм версии микроархитектуры Intel Nehalem. Новые процессоры Intel семейства Westmere стали пер- выми процессорами, созданными по нормам 32 нм техпроцесса. Эти процессоры известны под кодовыми названиями Clarkdale и Arrandale, предназначены для применения соответственно в настольных компью- терах и ноутбуках и входят в модельные линейки Intel Core i3, i5, i7. Процессоры Intel Westmere представляют собой двухъядерные решения. Кроме того, в их конструкции присутствуют два несущих кристалла (рис. 3.10), один из которых, выпускаемый по 32 нм техпроцессу, вклю- чает в себя два вычислительных ядра, разделяемую L3 кэш-память, кон- троллер шины QPI.

творами, корпорация Intel в конце 2009 г. запустила 32 нм производ- ственную технологию, в которой используются диэлектрики high-k и транзисторы с металлическими затворами второго поколения. Эта технология стала основой для новой 32 нм версии микроархитектуры Intel Nehalem. Новые процессоры Intel семейства Westmere стали пер- выми процессорами, созданными по нормам 32 нм техпроцесса. Эти процессоры известны под кодовыми названиями Clarkdale и Arrandale, предназначены для применения соответственно в настольных компью- терах и ноутбуках и входят в модельные линейки Intel Core i3, i5, i7. Процессоры Intel Westmere представляют собой двухъядерные решения. Кроме того, в их конструкции присутствуют два несущих кристалла (рис. 3.10), один из которых, выпускаемый по 32 нм техпроцессу, вклю- чает в себя два вычислительных ядра, разделяемую L3 кэш-память, кон- троллер шины QPI.

DDR3-1333 DDR3-1333

DDR3-1333

DDR3-1333

Рис. 3.10. Структура процессоров Intel семейства Westmere

Второй, более крупный кристалл, изготавливаемый по 45 нм техно- логии, содержит графический процессор GPU, двухканальный контроллер памяти DDR3, контроллер интерфейса PCI Express 2.0 и контроллер шин DMI и FDI (Flexible Display Interface). Взаимодействие между двумя кристаллами происходит по высокоскоростной шине QPI.

Ключевыми особенностями процессоров архитектуры Sandy Bridge

по сравнению с Nehalem являются:

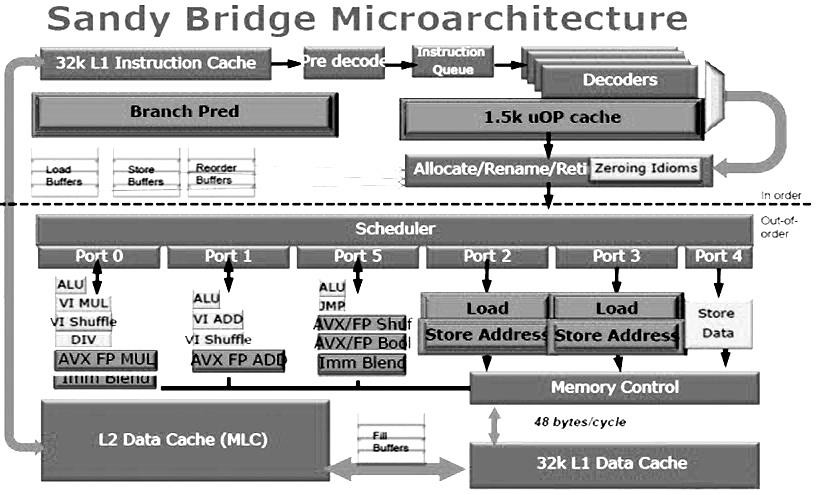

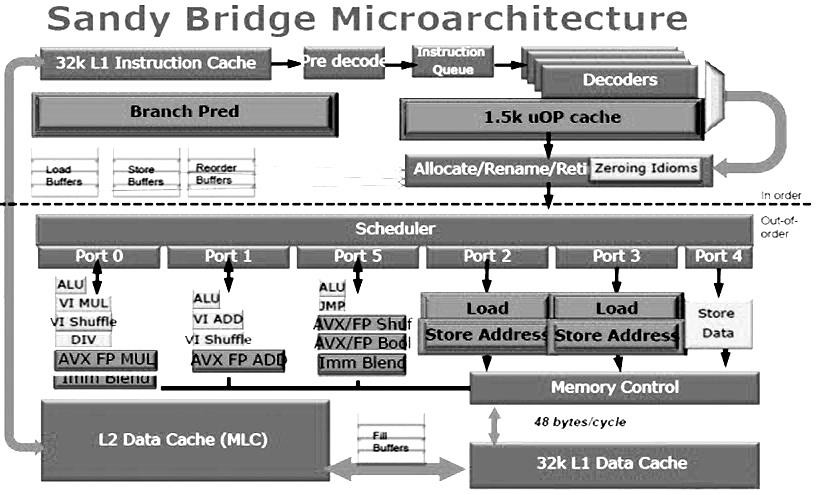

Рис. 3.11. Структура ядра микроархитектуры Sandy Bridge

Более подробно особенности организации процессорного ядра Sandy Bridge рассмотрены в разделе 3.4.6. Рассмотрение проводится в сравении с ядром новой микроархитектуры Intel Haswell.

Вся история модернизации процессорных микроархитектур Intel последних лет неразрывно связана с последовательной интеграцией в единый кристалл всё большего количества модулей и функций, ранее располагавшихся вне процессора: в чипсете, на материнской плате и т.д. Соответственно, по мере увеличения производительности процессора и степени интеграции чипа, требования к пропускной способности внут- ренних межкомпонентных шин росли опережающими темпами.

В микроархитектуре Sandy Bridge для повышения общей произво- дительности системы разработчики решили обратиться к кольцевой то- пологии 256-битной межкомпонентной шины, выполненной на основе новой версии технологии QPI (QuickPath Interconnect), расширенной и доработанной (рис. 3.12).

Кольцевая шина (Ring Interconnect) в версии архитектуры Sandy Bridge для настольных и мобильных систем служит для обмена данны- ми между шестью ключевыми компонентами чипа: четырьмя процес- сорными ядрами x86, графическим ядром, кэш-памятью L3, теперь её называют LLC (Last Level Cache – кеш последнего уровня), и систем- ным агентом. Шина состоит из четырёх 32-байтных колец: шины дан- ных (Data Ring), шины запросов (Request Ring), шины мониторинга со- стояния (Snoop Ring) и шины подтверждения (Acknowledge Ring).

Управление шинами осуществляется с помощью коммуникацион- ного протокола распределённого арбитража, при этом конвейерная об- работка запросов происходит на тактовой частоте процессорных ядер, что придаёт архитектуре дополнительную гибкость при разгоне. Произ- водительность кольцевой шины оценивается на уровне 96 Гбайт в се- кунду на соединение при тактовой частоте 3 ГГц, что фактически в че- тыре раза превышает показатели процессоров Intel предыдущего поко- ления.

Рис. 3.12. Кольцевая шина SandyBridge

Кольцевая топология и организация шин обеспечивает минималь- ную латентность при обработке запросов, максимальную производи- тельность и отличную масштабируемость технологии

Главное преимущество этой технологии состоит в том, что управ- ление питанием отдельных ядер осуществляется целиком внутри про- цессора и не требует усложнения схемы конвертера питания на мате- ринской плате.

Что же касается общих для всех ядер процессорных блоков, таких как контроллеры памяти и интерфейса QPI, то они переходят в энерго-

сберегающие состояния, когда в состоянии сна находятся все процес- сорные ядра.

Технология Turbo Boost

Наличие в процессоре контроллера, способного независимо управ- лять состоянием процессорных ядер, позволило Intel реализовать и еще одну интересную технологию, получившую название Turbo Boost Technology. Эта технология вводит понятие турбо-режима, в котором отдельные ядра могут работать на частоте, превосходящей номиналь- ную, т.е. разгоняться. Основной принцип Turbo Boost Technology состо- ит в том, что при переходе отдельных ядер в энергосберегающие состо- яния снижается общее энергопотребление и тепловыделение процессо- ра, а это, в свою очередь, позволяет нарастить частоты остальных ядер без риска выйти за установленные рамки TDP.

Фактически прообраз этой технологии уже был реализован в двухъядерных мобильных процессорах поколения Penryn, однако в Nehalem её развитие продвинулось еще дальше. В новых процессорах, если нет риска выйти за границу типичного энергопотребления и тепло- выделения, PCU может повышать частоты процессорных ядер на один шаг выше номинала (133 МГц). Это может происходить, например, при слабо распараллеленной нагрузке, когда часть ядер находится в состоя- нии простоя. Более того, при

соблюдении описанных условий, частота одного из ядер может быть увеличена и на два шага выше номинала (266 МГц).

Следует отметить, что необходимым условием включения турбо- режима вовсе не является переход одного или нескольких ядер в энер- госберегающее состояние. Это всего лишь один из возможных сценари- ев. Так как PCU имеет все средства для получения данных о фактиче- ском состоянии процессорных ядер, турбо-режим может задействовать- ся и в тех случаях, когда все ядра работают, но нагрузка на часть из них невелика.

Большим преимуществом Turbo Boost Technology является ее пол- ная прозрачность для операционной системы. Эта технология реализо- вана исключительно аппаратными средствами и не требует использова- ния никаких программных утилит для своей активации.

- 1 ... 50 51 52 53 54 55 56 57 ... 76

Семейство процессоров Intel Westmere

Основываясь на ошеломляющем успехе 45 нм производственного процесса с диэлектриками high-k и транзисторами с металлическими за-

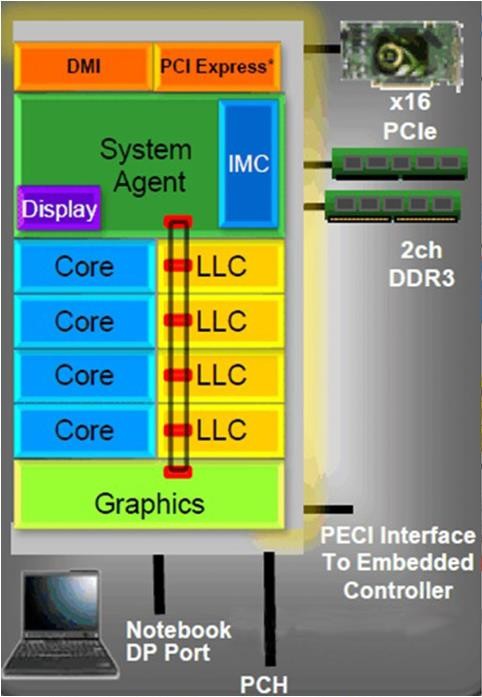

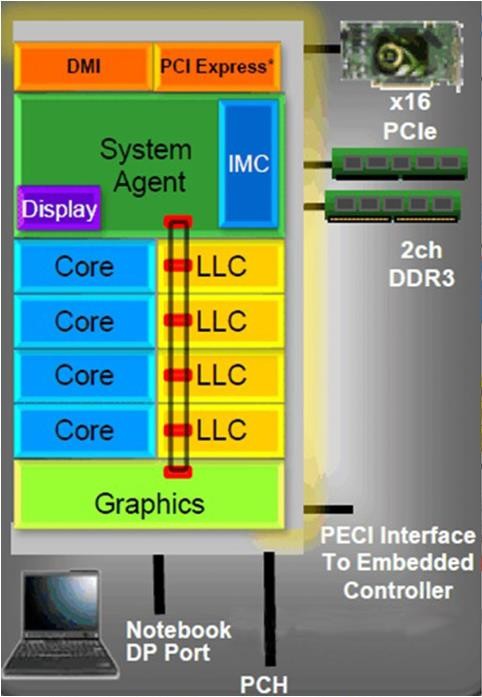

творами, корпорация Intel в конце 2009 г. запустила 32 нм производ- ственную технологию, в которой используются диэлектрики high-k и транзисторы с металлическими затворами второго поколения. Эта технология стала основой для новой 32 нм версии микроархитектуры Intel Nehalem. Новые процессоры Intel семейства Westmere стали пер- выми процессорами, созданными по нормам 32 нм техпроцесса. Эти процессоры известны под кодовыми названиями Clarkdale и Arrandale, предназначены для применения соответственно в настольных компью- терах и ноутбуках и входят в модельные линейки Intel Core i3, i5, i7. Процессоры Intel Westmere представляют собой двухъядерные решения. Кроме того, в их конструкции присутствуют два несущих кристалла (рис. 3.10), один из которых, выпускаемый по 32 нм техпроцессу, вклю- чает в себя два вычислительных ядра, разделяемую L3 кэш-память, кон- троллер шины QPI.

творами, корпорация Intel в конце 2009 г. запустила 32 нм производ- ственную технологию, в которой используются диэлектрики high-k и транзисторы с металлическими затворами второго поколения. Эта технология стала основой для новой 32 нм версии микроархитектуры Intel Nehalem. Новые процессоры Intel семейства Westmere стали пер- выми процессорами, созданными по нормам 32 нм техпроцесса. Эти процессоры известны под кодовыми названиями Clarkdale и Arrandale, предназначены для применения соответственно в настольных компью- терах и ноутбуках и входят в модельные линейки Intel Core i3, i5, i7. Процессоры Intel Westmere представляют собой двухъядерные решения. Кроме того, в их конструкции присутствуют два несущих кристалла (рис. 3.10), один из которых, выпускаемый по 32 нм техпроцессу, вклю- чает в себя два вычислительных ядра, разделяемую L3 кэш-память, кон- троллер шины QPI.DDR3-1333 DDR3-1333

DDR3-1333

DDR3-1333

Рис. 3.10. Структура процессоров Intel семейства Westmere

Второй, более крупный кристалл, изготавливаемый по 45 нм техно- логии, содержит графический процессор GPU, двухканальный контроллер памяти DDR3, контроллер интерфейса PCI Express 2.0 и контроллер шин DMI и FDI (Flexible Display Interface). Взаимодействие между двумя кристаллами происходит по высокоскоростной шине QPI.

-

Микроархитектура Sandy Bridge

Ключевыми особенностями процессоров архитектуры Sandy Bridge

по сравнению с Nehalem являются:

-

Усовершенствованное вычислительное ядро (рис. 3.11).

Рис. 3.11. Структура ядра микроархитектуры Sandy Bridge

-

Монолитная конструкция – процессор состоит из одного полупро- водникового кристалла, изготовленного по 32 нм технологии техпро- цесса. -

Новый набор инструкций Intel Advanced Vector Extensions (AVX) для ускорения обработки вещественных чисел. -

Оптимизированная технология Intel Turbo Boost. -

Заметно увеличившаяся энергоэффективность. -

Производительность интегрированного в процессор графического яд- ра значительно увеличена. -

Новая кольцевая шина Ring Interconnect. -

Наличие нового функционального узла процессора – системного агента. -

Усовершенствованный интегрированный контроллер памяти.

Более подробно особенности организации процессорного ядра Sandy Bridge рассмотрены в разделе 3.4.6. Рассмотрение проводится в сравении с ядром новой микроархитектуры Intel Haswell.

Кольцевая шина

Вся история модернизации процессорных микроархитектур Intel последних лет неразрывно связана с последовательной интеграцией в единый кристалл всё большего количества модулей и функций, ранее располагавшихся вне процессора: в чипсете, на материнской плате и т.д. Соответственно, по мере увеличения производительности процессора и степени интеграции чипа, требования к пропускной способности внут- ренних межкомпонентных шин росли опережающими темпами.

В микроархитектуре Sandy Bridge для повышения общей произво- дительности системы разработчики решили обратиться к кольцевой то- пологии 256-битной межкомпонентной шины, выполненной на основе новой версии технологии QPI (QuickPath Interconnect), расширенной и доработанной (рис. 3.12).

Кольцевая шина (Ring Interconnect) в версии архитектуры Sandy Bridge для настольных и мобильных систем служит для обмена данны- ми между шестью ключевыми компонентами чипа: четырьмя процес- сорными ядрами x86, графическим ядром, кэш-памятью L3, теперь её называют LLC (Last Level Cache – кеш последнего уровня), и систем- ным агентом. Шина состоит из четырёх 32-байтных колец: шины дан- ных (Data Ring), шины запросов (Request Ring), шины мониторинга со- стояния (Snoop Ring) и шины подтверждения (Acknowledge Ring).

Управление шинами осуществляется с помощью коммуникацион- ного протокола распределённого арбитража, при этом конвейерная об- работка запросов происходит на тактовой частоте процессорных ядер, что придаёт архитектуре дополнительную гибкость при разгоне. Произ- водительность кольцевой шины оценивается на уровне 96 Гбайт в се- кунду на соединение при тактовой частоте 3 ГГц, что фактически в че- тыре раза превышает показатели процессоров Intel предыдущего поко- ления.

Рис. 3.12. Кольцевая шина SandyBridge

Кольцевая топология и организация шин обеспечивает минималь- ную латентность при обработке запросов, максимальную производи- тельность и отличную масштабируемость технологии