ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 26.10.2023

Просмотров: 635

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

АРХИТЕКТУРЫ, ХАРАКТЕРИСТИКИ, КЛАССИФИКАЦИЯ ЭВМ

3. ФУНКЦИОНАЛЬНАЯ И СТРУКТУРНАЯ

4. ПРИНЦИПЫ ОРГАНИЗАЦИИ ПОДСИСТЕМЫ ПАМЯТИ ЭВМ И ВС

ОРГАНИЗАЦИЯ СИСТЕМНОГО ИНТЕРФЕЙСА И ВВОДА/ВЫВОДА ИНФОРМАЦИИ

МНОГОПРОЦЕССОРНЫЕ И МНОГОМАШИННЫЕ ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ

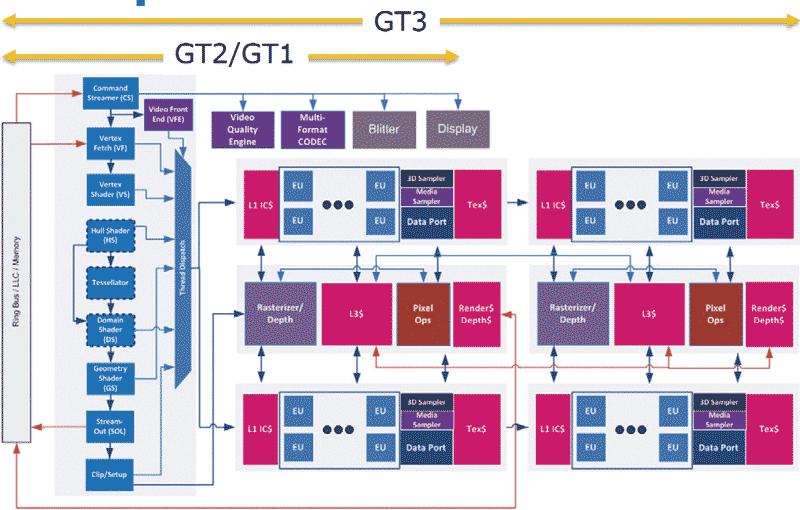

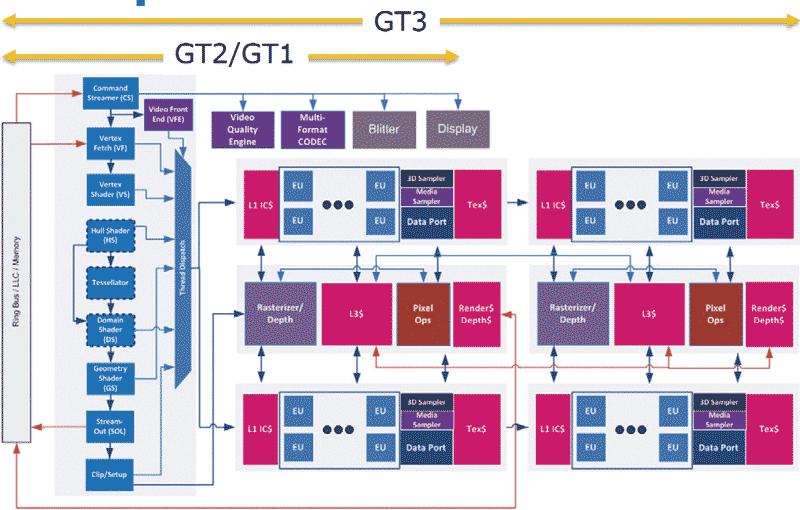

своего предшественника по уровню производительности. Кроме того, ядро GT3 имеет более высокую производительность благодаря интегра- ции памяти EDRAM (в ядре GT3e) в упаковку процессора.

Ядро GT2 содержит 20 исполнительных блоков, 80 вычислитель- ных ядер и два текстурных модуля, а ядро GT1 — только 10 исполни- тельных блоков, 40 вычислительных ядер и один текстурный модуль.

Сами исполнительные блоки имеют по четыре вычислительных яд-

ра.

Еще одно нововведение заключается в том, что при работе с памя-

тью применятся технология Instant Access, которая позволяет вычисли- тельным ядрам процессора и графическому ядру напрямую обращаться к оперативной памяти. В предыдущих версиях графического ядра вы- числительные ядра процессора и графическое ядро тоже работали с об- щей оперативной памятью, но при этом память делилась на две области с динамически изменяемыми размерами. Одна из них отводилась для графического ядра, а другая — для вычислительных ядер процессора.

Рис. 3.17. Структура графического ядра

Технология InstantAccess позволяет драйверу графического ядра ставить указатель на положение определенного участка в области памя- ти графического ядра, к которой вычислительному ядру процессора необходимо напрямую получить доступ. При этом вычислительное ядро процессора будет работать с этой областью памяти напрямую, без со- здания копии, а после выполнения необходимых действий область па- мяти будет возвращена в распоряжение графического ядра.

Семейство новых графических ядер GT1, GT2 и GT3 обладает улучшенными возможностями по кодированию-декодированию видео-

данных. Поддерживается аппаратное декодирование форматов H.264/MPEG-4 AVC, VC-1, MPEG-2, MPEG-2 HD, Motion JPEG, DivX с

разрешением вплоть до 4096×2304 пикселов. Заявляется, что графиче- ское ядро способно одновременно декодировать несколько видеопото- ков 1080p и воспроизводить видео 2160p без подтормаживания и про- пуска кадров.

Появился и специальный блок улучшения качества видео, который называется Video Quality Engine и отвечает за шумоподавление, цвето- коррекцию, деинтерлейсинг, адаптивное изменение контраста и т.д. Также новые графические ядра будут поддерживать функции стабили- зации изображения, преобразования частоты кадров и расширенной гаммы.

Кроме того, графическое ядро в процессоре Haswell обеспечивает подключение до трех мониторов одновременно.

Шестое поколение многоядерных процессоров Intel Core с рабочим названиемSkylake с полным на то правом можно назвать одним из наиболее масштабируемых и революционных за всю историю архитек- туры Core. В этом заявлении нет ни малейшего преувеличения. Так, масштабируемость подтверждает ассортимент из почти 50 наименова- ний Xeon, Core i3/5/7, Core M3/5/7, Pentium и Celeron с впечатляющим разбросом характеристик: от крохотных (20 х 16,5 мм) чипов в ком- пактной корпусировке BGA1515 с TDP 4,5 Вт до мощных разблокиро- ванных десктопных LGA1151 процессоров вроде Core i7-6700K с габа- ритами 37,5 x 37,5 мм и TDP порядка 91 Вт. То есть, 20-кратная мас- штабируемость по энергопотреблению и 4-кратная по размерам чипа.

Кроме того, процессоры с архитектурой Skylake, выпускаемые с соблюдением норм 14-нм техпроцесса Intel, появятся быстро, и сразу практически для всех сегментов вычислительной техники – от мобиль-

ных устройств до серверов. Это гораздо энергичнее, нежели 22-нм чипы Haswell двухлетней давности, и гораздо масштабнее чем предыдущее поколение с рабочим названием Broadwell, когда, почти "в обход" деск- топных платформ, основной упор был сделан на чипы для ноутбуков и

планшетов.

Что касается тезиса о революционности, он подтверждается дей- ствительно существенным изменением схемотехники и производитель- ности большинства ключевых элементов архитектуры, таких как DDR4/DDR3L, eDRAM, графика HD Intel Graphics 5xx, Iris/Iris Pro и многое другое, чему, соответственно, и посвящён этот материал.

Архитектура процессоров Skylake получила сотни структурных из- менений и улучшений, позволивших повысить производительность при снижении потребления энергии.

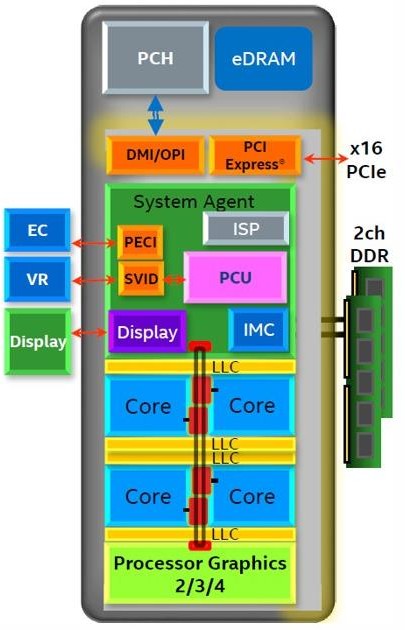

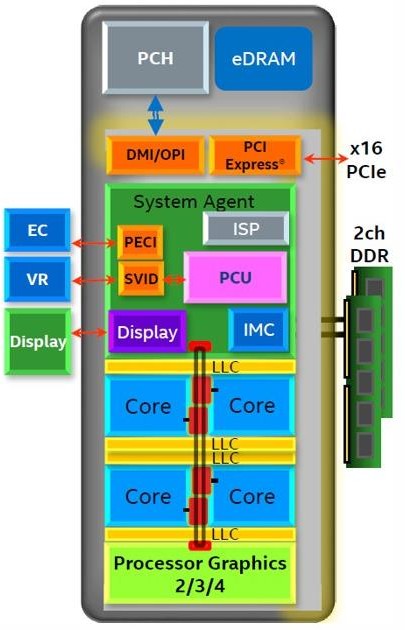

Вычислительные процессорные ядра при этом, хоть и изменились, но остались примерно сравнимыми по структурному строению с преды- дущими поколениями Broadwell и Haswell. Чего нельзя сказать о струк- турном уровне чипа в целом (рис. 3.18), где появился ряд совершенно новых модулей и блоков. Благодаря этому новые чипы Intel Core шесто- го поколения окончательно превратились из классических процессоров в так называемые "системы на чипе" (SoC, System on Chip).

Стандартный набор компонентов процессора Skylake состоит из двух или четырёх вычислительных ядер (CPU), графической подсисте- мы, общей кольцевой коммуникационной шины, блока платформенных контроллеров PCH (Platform Controller Hub, порой до сих пор называе- мого "южным мостом") на многоканальной шине DMI/OPI, интегриро- ванного "расширителя кэша" eDRAM (бывший Crystalwell, опциональ- ный у Haswell), шины PCI Express x16, а также встроенного модуля си- стемных блоков System Agent. В свою очередь, в состав System Agent входят как уже привычные (но значительно переработанные), так и со- вершенно новые блоки, включая доработанный управляющий блок PCU (Package Control Unit) с блоком контроля температуры (PECI, Platform Environment Control Interface) и напряжения (SVID, Serial Voltage Identification), контроллер памяти DDR3L/DDR4, блоки мультимедий- ной обработки и вывода видео, плюс совершенно новый процессор об- работки изображений ISP (Image Signal Processing).

Основным усовершенствованием процессорных x86-ядер Skylake, позволяющим говорить о повышении качества предсказания ветвлений,

загрузки исполнительного конвейера и, как следствие, более частого одновременного декодирования CISC-инструкций и исполнения до ше- сти микроинструкций за каждый такт, стоит назвать значительно рас-

ширенные по сравнению с предыдущими поколениями внутренние бу- феры.

Рис. 3.18. Стандартный набор компонентов процессора

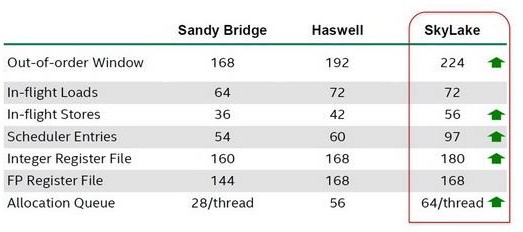

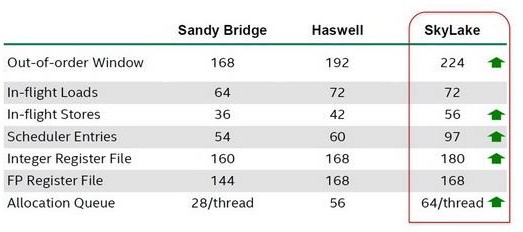

На представленном ниже скриншоте из презентации Intel наглядно виден последовательный рост емкости буферов на примере трёх по- следних поколений архитектуры Core (рис. 3.19).

Рис. 3.19. Последовательный рост ёмкости внутренних буферов процессора

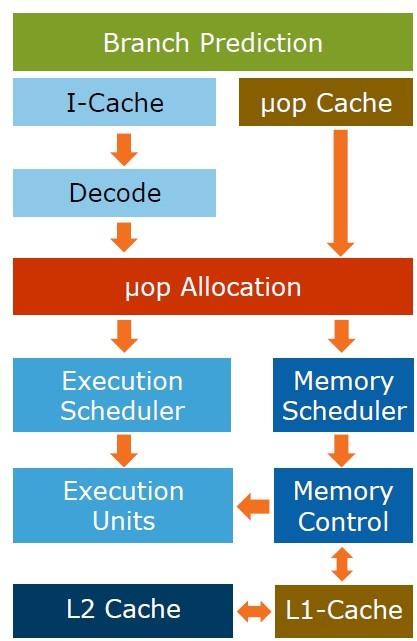

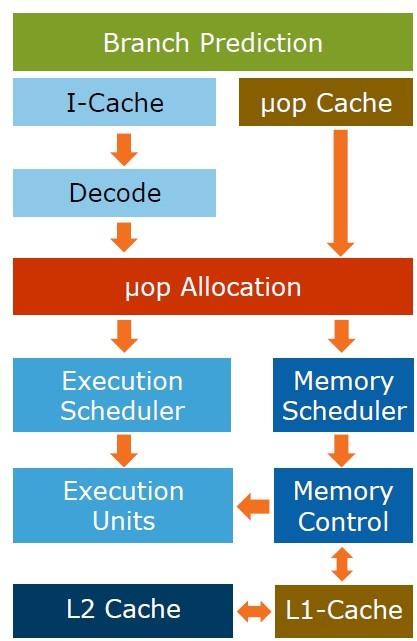

Обработка входящих команд улучшена благодаря ускоренной ра- боте более ёмкого блока предсказания ветвлений, более глубокая буфе- ризация внеочередного исполнения инструкций позволила говорить о более качественном распараллеливании обрабатываемого кода, умень- шении латентности и снижении энергопотребления в моменты простоя (рис. 3.20).

В целом архитектура Skylake обладает более глубокой буферизаци- ей данных, чтения/записи, отложенной (write-back) записи, ускоренной производительностью обработки промахов страниц и кэш-памяти L2. Со времён Sandy Bridge почти в полтора раза (до 224) увеличилось окно внеочередного исполнения инструкций, улучшена работа Hyper- Threading за счёт почти удвоенного до 64 на поток окна очереди распре- деления и сниженного простоя конвейера за счёт оптимизированных ал- горитмов улучшенного блока предсказания ветвления. Также появились новые инструкции для лучшего управления загрузкой кэш-памяти, а скорость работы протокола AES криптографического шифрования в GCM- и CBC-режимах выросла на 17% и 33%, соответственно.

Рис. 3.20. Структура ядра процессора

В архитектуре Skylake появилась поддержка наборов новых инструкций MIC и SGX.

Серьёзным изменениям в архитектуре Skylake подверглась кольцевая шина, кэш-память и структура цепей работы с памятью. Согласно данным Intel, пропускная способность кольцевой шины, обеспечивающей обмен между вычислительными ядрами, графической подсистемой, системным агентом, контроллером памяти и кэш-памятью L3 была удвоена по сравнению с поколением Haswell, при этом число используемых для этого транзисторов увеличилось лишь на 50%, а уровень энергопотребления для многих режимов остался на прежнем уровне.

Удвоенная производительность кольцевой шины позволила удвоить скорость работы кэш-памяти L3 при обработке промахов, что вместе с появлением поддержки DDR4 и особенностями работы eDRAM даёт надежду на значительный прирост производительности в некоторых приложениях. Помимо этого улучшенная работа с памятью также сказалась на обеспечении стабильной работы процессора обработки изображений (ISP) и поддержке видеовыхода на три дисплея с разрешением до 4K.

В архитектуре Skylake реализована новая, полностью когерентная структура встроенной DRAM (eDRAM), или Memory Side Cache, способная кэшировать любые данные, включая варианты "некэшируемой памяти", без необходимости очистки для поддержания когерентности, и доступной для использования устройствами ввода- вывода и формирования выходного видеосигнала. Помимо этого графическая подсистема для достижения оптимальной производительности может выбрать режим кэширования определённых данных только в eDRAM без использования кэш-памяти L3.

В

Ядро GT2 содержит 20 исполнительных блоков, 80 вычислитель- ных ядер и два текстурных модуля, а ядро GT1 — только 10 исполни- тельных блоков, 40 вычислительных ядер и один текстурный модуль.

Сами исполнительные блоки имеют по четыре вычислительных яд-

ра.

Еще одно нововведение заключается в том, что при работе с памя-

тью применятся технология Instant Access, которая позволяет вычисли- тельным ядрам процессора и графическому ядру напрямую обращаться к оперативной памяти. В предыдущих версиях графического ядра вы- числительные ядра процессора и графическое ядро тоже работали с об- щей оперативной памятью, но при этом память делилась на две области с динамически изменяемыми размерами. Одна из них отводилась для графического ядра, а другая — для вычислительных ядер процессора.

Рис. 3.17. Структура графического ядра

Технология InstantAccess позволяет драйверу графического ядра ставить указатель на положение определенного участка в области памя- ти графического ядра, к которой вычислительному ядру процессора необходимо напрямую получить доступ. При этом вычислительное ядро процессора будет работать с этой областью памяти напрямую, без со- здания копии, а после выполнения необходимых действий область па- мяти будет возвращена в распоряжение графического ядра.

Семейство новых графических ядер GT1, GT2 и GT3 обладает улучшенными возможностями по кодированию-декодированию видео-

данных. Поддерживается аппаратное декодирование форматов H.264/MPEG-4 AVC, VC-1, MPEG-2, MPEG-2 HD, Motion JPEG, DivX с

разрешением вплоть до 4096×2304 пикселов. Заявляется, что графиче- ское ядро способно одновременно декодировать несколько видеопото- ков 1080p и воспроизводить видео 2160p без подтормаживания и про- пуска кадров.

Появился и специальный блок улучшения качества видео, который называется Video Quality Engine и отвечает за шумоподавление, цвето- коррекцию, деинтерлейсинг, адаптивное изменение контраста и т.д. Также новые графические ядра будут поддерживать функции стабили- зации изображения, преобразования частоты кадров и расширенной гаммы.

Кроме того, графическое ядро в процессоре Haswell обеспечивает подключение до трех мониторов одновременно.

-

Микроархитектура Skylake

Шестое поколение многоядерных процессоров Intel Core с рабочим названиемSkylake с полным на то правом можно назвать одним из наиболее масштабируемых и революционных за всю историю архитек- туры Core. В этом заявлении нет ни малейшего преувеличения. Так, масштабируемость подтверждает ассортимент из почти 50 наименова- ний Xeon, Core i3/5/7, Core M3/5/7, Pentium и Celeron с впечатляющим разбросом характеристик: от крохотных (20 х 16,5 мм) чипов в ком- пактной корпусировке BGA1515 с TDP 4,5 Вт до мощных разблокиро- ванных десктопных LGA1151 процессоров вроде Core i7-6700K с габа- ритами 37,5 x 37,5 мм и TDP порядка 91 Вт. То есть, 20-кратная мас- штабируемость по энергопотреблению и 4-кратная по размерам чипа.

Кроме того, процессоры с архитектурой Skylake, выпускаемые с соблюдением норм 14-нм техпроцесса Intel, появятся быстро, и сразу практически для всех сегментов вычислительной техники – от мобиль-

ных устройств до серверов. Это гораздо энергичнее, нежели 22-нм чипы Haswell двухлетней давности, и гораздо масштабнее чем предыдущее поколение с рабочим названием Broadwell, когда, почти "в обход" деск- топных платформ, основной упор был сделан на чипы для ноутбуков и

планшетов.

Что касается тезиса о революционности, он подтверждается дей- ствительно существенным изменением схемотехники и производитель- ности большинства ключевых элементов архитектуры, таких как DDR4/DDR3L, eDRAM, графика HD Intel Graphics 5xx, Iris/Iris Pro и многое другое, чему, соответственно, и посвящён этот материал.

Архитектура процессоров Skylake получила сотни структурных из- менений и улучшений, позволивших повысить производительность при снижении потребления энергии.

Вычислительные процессорные ядра при этом, хоть и изменились, но остались примерно сравнимыми по структурному строению с преды- дущими поколениями Broadwell и Haswell. Чего нельзя сказать о струк- турном уровне чипа в целом (рис. 3.18), где появился ряд совершенно новых модулей и блоков. Благодаря этому новые чипы Intel Core шесто- го поколения окончательно превратились из классических процессоров в так называемые "системы на чипе" (SoC, System on Chip).

Стандартный набор компонентов процессора Skylake состоит из двух или четырёх вычислительных ядер (CPU), графической подсисте- мы, общей кольцевой коммуникационной шины, блока платформенных контроллеров PCH (Platform Controller Hub, порой до сих пор называе- мого "южным мостом") на многоканальной шине DMI/OPI, интегриро- ванного "расширителя кэша" eDRAM (бывший Crystalwell, опциональ- ный у Haswell), шины PCI Express x16, а также встроенного модуля си- стемных блоков System Agent. В свою очередь, в состав System Agent входят как уже привычные (но значительно переработанные), так и со- вершенно новые блоки, включая доработанный управляющий блок PCU (Package Control Unit) с блоком контроля температуры (PECI, Platform Environment Control Interface) и напряжения (SVID, Serial Voltage Identification), контроллер памяти DDR3L/DDR4, блоки мультимедий- ной обработки и вывода видео, плюс совершенно новый процессор об- работки изображений ISP (Image Signal Processing).

Основным усовершенствованием процессорных x86-ядер Skylake, позволяющим говорить о повышении качества предсказания ветвлений,

загрузки исполнительного конвейера и, как следствие, более частого одновременного декодирования CISC-инструкций и исполнения до ше- сти микроинструкций за каждый такт, стоит назвать значительно рас-

ширенные по сравнению с предыдущими поколениями внутренние бу- феры.

Рис. 3.18. Стандартный набор компонентов процессора

На представленном ниже скриншоте из презентации Intel наглядно виден последовательный рост емкости буферов на примере трёх по- следних поколений архитектуры Core (рис. 3.19).

Рис. 3.19. Последовательный рост ёмкости внутренних буферов процессора

Обработка входящих команд улучшена благодаря ускоренной ра- боте более ёмкого блока предсказания ветвлений, более глубокая буфе- ризация внеочередного исполнения инструкций позволила говорить о более качественном распараллеливании обрабатываемого кода, умень- шении латентности и снижении энергопотребления в моменты простоя (рис. 3.20).

В целом архитектура Skylake обладает более глубокой буферизаци- ей данных, чтения/записи, отложенной (write-back) записи, ускоренной производительностью обработки промахов страниц и кэш-памяти L2. Со времён Sandy Bridge почти в полтора раза (до 224) увеличилось окно внеочередного исполнения инструкций, улучшена работа Hyper- Threading за счёт почти удвоенного до 64 на поток окна очереди распре- деления и сниженного простоя конвейера за счёт оптимизированных ал- горитмов улучшенного блока предсказания ветвления. Также появились новые инструкции для лучшего управления загрузкой кэш-памяти, а скорость работы протокола AES криптографического шифрования в GCM- и CBC-режимах выросла на 17% и 33%, соответственно.

Рис. 3.20. Структура ядра процессора

В архитектуре Skylake появилась поддержка наборов новых инструкций MIC и SGX.

Серьёзным изменениям в архитектуре Skylake подверглась кольцевая шина, кэш-память и структура цепей работы с памятью. Согласно данным Intel, пропускная способность кольцевой шины, обеспечивающей обмен между вычислительными ядрами, графической подсистемой, системным агентом, контроллером памяти и кэш-памятью L3 была удвоена по сравнению с поколением Haswell, при этом число используемых для этого транзисторов увеличилось лишь на 50%, а уровень энергопотребления для многих режимов остался на прежнем уровне.

Удвоенная производительность кольцевой шины позволила удвоить скорость работы кэш-памяти L3 при обработке промахов, что вместе с появлением поддержки DDR4 и особенностями работы eDRAM даёт надежду на значительный прирост производительности в некоторых приложениях. Помимо этого улучшенная работа с памятью также сказалась на обеспечении стабильной работы процессора обработки изображений (ISP) и поддержке видеовыхода на три дисплея с разрешением до 4K.

В архитектуре Skylake реализована новая, полностью когерентная структура встроенной DRAM (eDRAM), или Memory Side Cache, способная кэшировать любые данные, включая варианты "некэшируемой памяти", без необходимости очистки для поддержания когерентности, и доступной для использования устройствами ввода- вывода и формирования выходного видеосигнала. Помимо этого графическая подсистема для достижения оптимальной производительности может выбрать режим кэширования определённых данных только в eDRAM без использования кэш-памяти L3.

В