ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 26.10.2023

Просмотров: 633

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

АРХИТЕКТУРЫ, ХАРАКТЕРИСТИКИ, КЛАССИФИКАЦИЯ ЭВМ

3. ФУНКЦИОНАЛЬНАЯ И СТРУКТУРНАЯ

4. ПРИНЦИПЫ ОРГАНИЗАЦИИ ПОДСИСТЕМЫ ПАМЯТИ ЭВМ И ВС

ОРГАНИЗАЦИЯ СИСТЕМНОГО ИНТЕРФЕЙСА И ВВОДА/ВЫВОДА ИНФОРМАЦИИ

МНОГОПРОЦЕССОРНЫЕ И МНОГОМАШИННЫЕ ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ

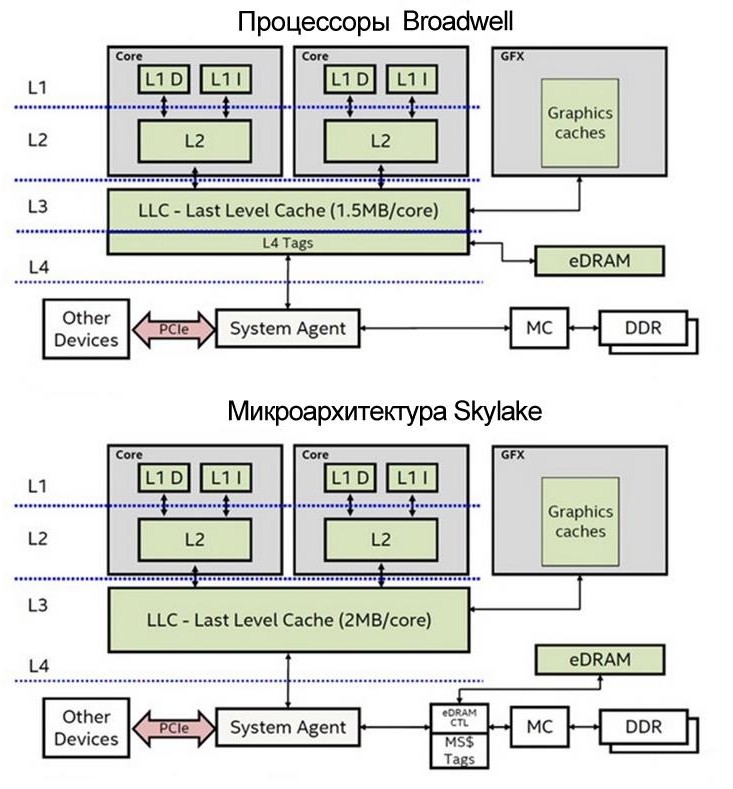

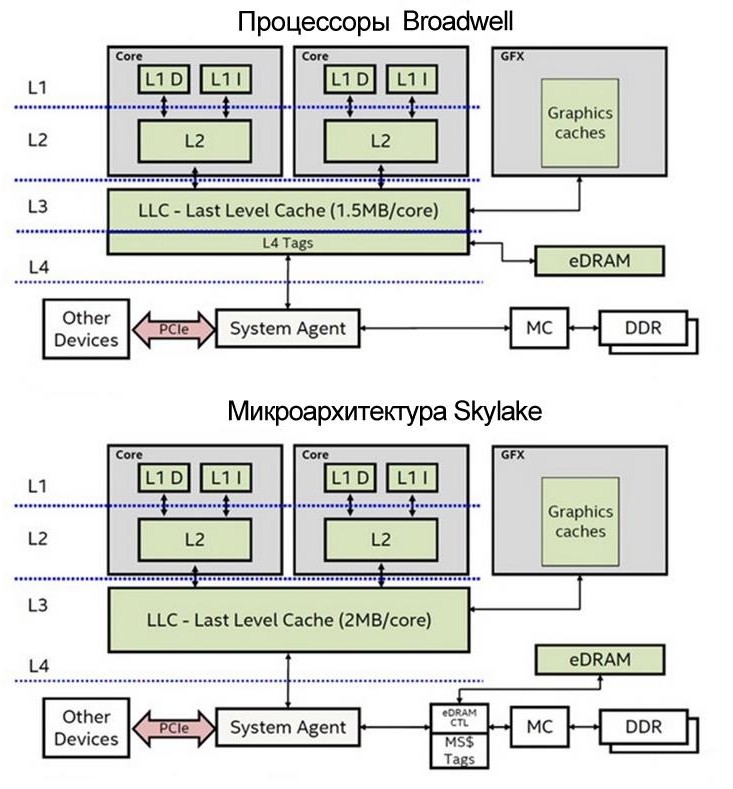

отличие от предыдущей архитектуры, где примерно четверть кэш-памяти L3 использовалась для доступа к eDRAM, и при этом eDRAM не имела возможности прямого взаимодействия с остальной системой, в архитектуре Skylake контроллер eDRAM переместился в модуль системного агента, освободив таким образом порядка 512 Кбайт ёмкости кэша L3 и одновременно с этим облегчив доступ другим компонентам ядра к данным в eDRAM. Отныне Memory Side Cache может взаимодействовать с основной системной памятью напрямую, обеспечивая таким образом обновление экрана без необходимости вывода остальных компонентов процессора из ждущего режима.

Рис. 3.21. Конфигурация процессора с eDRAM

К сожалению, как и в случае с архитектурой Haswell, в Intel так и не озвучили планов использования eDRAM в составе обычных LGA- процессоров на базе Skylake для настольных систем. Не исключено, что на этой стадии развития процессорной микроархитектуры Intel плюсы Memory Side Cache будут реализованы только в чипах для мобильных, встраиваемых и компактных систем.

Полупроводниковая логика и программная прошивка управляюще- го блока PCU в архитектуре Skylake подверглась значительным дора- боткам для достижения более динамичных режимов с высокими уров- нями производительности и агрессивными алгоритмами энергосбере-

жения, в том числе, в плане сбора внутренней статистики, внешней и внутренней телеметрии (iMon, Psys) и более тесного взаимодействия со старшими в иерархии системами управления (OS, BIOS).

Самое заметное и, пожалуй, существенное изменение в архитекту- ре Skylake связано с новым интегрированным контроллером оператив- ной памяти: он по-прежнему 2-канальный, однако теперь поддерживает

динамическую память как предыдущего стандарта DDR3L, так и нового поколения DDR4. Прежде полноценный контроллер DDR4 был на во- оружении только серверных чипов Xeon и выполненных на основе их дизайна топовых геймерских LGA 2011 чипах Intel Core i7, но фактиче- ски именно начиная со Skylake память DDR4 начинает своё широко- масштабное наступление на рынок настольных и мобильных систем.

Модуль аппаратной обработки мультимедийного контента и фи- нального рендеринга видеопотока в архитектуре Skylake также значи- тельно доработан и улучшен. В частности, аппаратный кодек HEVC/H265 нового поколения обладает повышенной производительно- стью с одновременным уменьшением энергопотребления; есть отдель- ный аппаратный кодек AVC с очень низким энергопотреблением; обес- печивается вывод изображения на три независимых 4K-дисплея со сни- женным на 40%-60% потреблением энергии даже в самом тяжёлом ре- жиме воспроизведения 4K-видео.

В дополнение, архитектура Skylake также поддерживает инициати- ву Intel по отказу от проводных подключений для беспроводной переда- чи мультимедийного контента с помощью технологий Intel WiDi или Pro WiDi с компьютеров на телевизоры, мониторы или проекторы.

Впервые в составе архитектуры для массовых процессоров Skylake (а не специализированных SoC) появился так называемый встроенный процессор обработки изображений – ISP (Image Signal Processing), что особенно актуально для смартфонов, планшетов и ноутбуков. В частно- сти, ISP обладает встроенным интерфейсом CSI (Camera Sensor Interface) с поддержкой до четырех внешних цифровых камер/сенсоров с разрешением до 13 Мп, правда, с одновременным обслуживанием только двух из них. Аппаратная обвязка CSI поддерживает расширен- ный список технологий для полноценной обработки фото и видео, включая распознавание и запоминание лиц, групповые снимки, много- поточный захват, съёмку с расширенным динамическим диапазоном (HDR), съёмку при слабом освещении, серийную съёмку и многое дру-

гое.

Роль графических ядер, встроенных в процессоры, с каждым годом увеличивается. И это связано не столько с ростом их 3D-

производительности, столько с тем, что встроенные GPU берут на себя всё новые функции, такие как параллельные вычисления или кодирова- ние и декодирование мультимедийного контента. Исключением не ста- ло и графическое ядро Skylake. Intel относит его к следующему, девято- му поколению, и это значит, что в нём таится немало сюрпризов. Одна- ко начать стоит с того, что GPU, реализованный в Skylake, как и его предшественники, сохранил традиционный модульный дизайн. Таким образом, мы вновь имеем дело с целым семейством решений разного класса: на базе имеющихся строительных блоков нового поколения Intel может собирать кардинально различающиеся по уровню производи- тельности GPU. Подобная масштабируемость сама по себе новинкой не является, но в Skylake возросла не только максимальная производитель- ность, но и число доступных вариантов графического ядра.

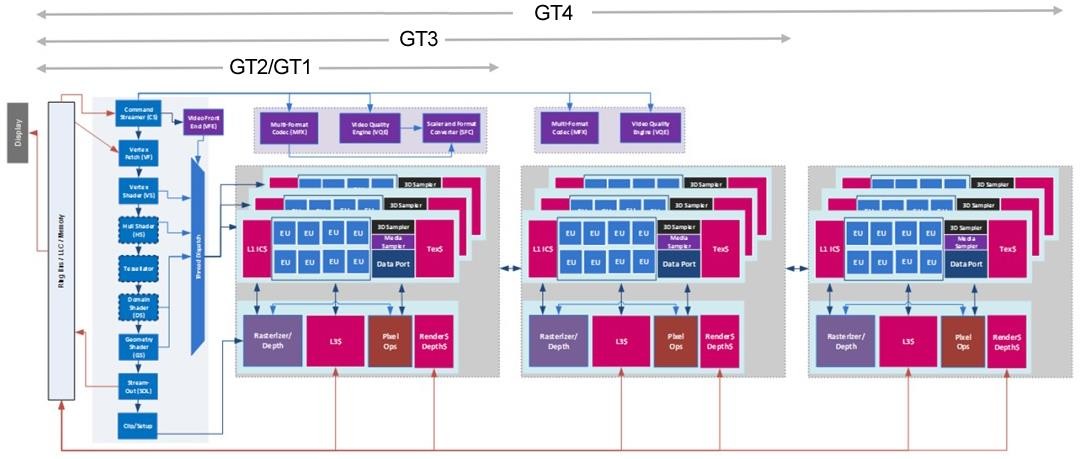

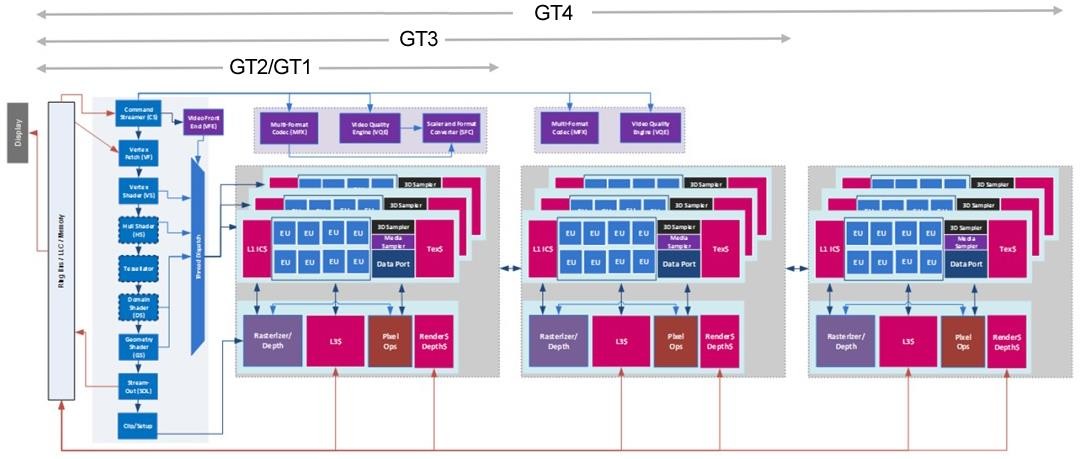

Итак, графическое ядро Skylake может быть построено на базе од- ного или нескольких модулей, каждый из которых обычно включает в себя по три секции. Секции объединяют по восемь исполнительных устройств, на которые ложится основная часть обработки графических данных, а также содержат базовые блоки для работы с памятью и тек- стурные семплеры. Помимо исполнительных устройств, сгруппирован- ных в модули, графическое ядро содержит и внемодульную часть, отве- чающую за фиксированные геометрические преобразования и отдель- ные мультимедийные функции.

На самом верхнем уровне иерархии графическое ядро Skylake очень похоже на ядро, реализованное в Broadwell. Однако если углу- биться в подробности, то нетрудно найти и заметные изменения.

Во-первых, внемодульная часть вынесена теперь в отдельный энер- гетический домен, что позволяет задавать ей частоту и отправлять её в сон отдельно от исполнительных устройств. Это значит, что, например,

при работе с технологией Quick Sync, которая реализуется как раз сила- ми внемодульных блоков, основная часть GPU может быть отключена от линий питания в целях снижения энергопотребления. Кроме того, не- зависимое управление частотой внемодульной части позволяет лучше подстраивать её производительность под конкретные нужды модулей графического ядра.

Во-вторых, в то время как графическое ядро Broadwell могло осно- вываться лишь на одном или двух модулях, получая в своё распоряже- ние 24 или 48 исполнительных устройств (для энергоэффективных и бюджетных процессоров мог использоваться один модуль с отключен- ными секциями, что давало меньшее, чем 24, число исполнительных устройств), в Skylake может применяться от одного до трёх модулей.

Благодаря этому в дополнение к привычным конфигурациям GT1/GT2/GT3 в семействе процессоров Skylake будет доступно ещё бо- лее мощное ядро GT4 (рис. 3.22), которое получит 72 исполнительных устройства.

Однако пиковая производительность самих исполнительных устройств в Skylake не изменилась – каждое такое устройство может выполнять до 16 32-битных операций за такт. При этом оно способно исполнять 7 вычислительных потоков одновременно и имеет 128 32- байтовых регистров общего назначения.

В-третьих, варианты ядра GT3 и GT4 могут быть дополнительно усилены eDRAM-буфером объёмом 64 или 128 Мбайт соответственно, что даёт модификации GT3e и GT4e. Процессоры Broadwell комплекто- вались лишь одним вариантом eDRAM – объёмом 128 Мбайт. В Skylake же этот дополнительный буфер не только изменил алгоритм работы, став «кешем на стороне памяти», но и приобрёл некоторую гибкость конфигурации. Однако его исполнение останется старым – он будет представлен отдельным 22-нм кристаллом, монтируемым на процессор- ную плату по соседству с основным чипом.

В 1969 году в связи с необходимостью в высокопроизводительной вычислительной технике для оснащения в нашей стране стратегических систем специального назначения возникла идея разработки многопро- цессорных вычислительных комплексов (МВК) семейства «Эльбрус». Основоположником идеи был Лебедев С.А., а главным конструктором прокта в Институте точной механики и вычислительной техники (ИТМ и ВТ) стал Бурцев В.С.

Разработка МВК «Эльбрус-1» началась в 1973 г., закончена в 1979 г. и сдана госудраственной комисси в 1980 г. Данный вычислительный комплекс был построен на базе TTL-микросхем.

Затем был построен МВК «Эльбрус-2». Годы разработки 1977- 1984, сдан в 1985 г. Данный комплекс в течении нескольких лет исполь- зовался в центральных объектах стратегических систем страны.

Следующим проектом стал МВК «Эльбрус-3». Руководителем про- екта был Бабаян Б.А. Опытный образец данного комплекса был изго- товлен в 1990 году, но в связи с прекращением финансирования отладка образца не была завершена.

Рис. 3.22. Структура графического ядра Skylake

Стало ясно, что будущие поколения вычислительной техники должны базироваться на микропроцессорах. В 1992 г. коллектив разра- ботчиков машин семейства «Эльбрус» выделился в компанию ЗАО

«МЦСТ – Московский центр SPARC-технологий» и совместно с ОАО

«ИНЭУМ имени И.С. Брука» начал вести работы над микропроцессор- ной реализацией разработанной архитектуры.

Основой серии осталась оригинальная архитектура «Эльбрус», а также добавилась открытая архитектура SPARC «Scalable Processor Ar- chitecture» (табл. 3.2).

Таблица 3.2 Разработка линии микропроцессоров «Эльбрус»

Рис. 3.21. Конфигурация процессора с eDRAM

К сожалению, как и в случае с архитектурой Haswell, в Intel так и не озвучили планов использования eDRAM в составе обычных LGA- процессоров на базе Skylake для настольных систем. Не исключено, что на этой стадии развития процессорной микроархитектуры Intel плюсы Memory Side Cache будут реализованы только в чипах для мобильных, встраиваемых и компактных систем.

Полупроводниковая логика и программная прошивка управляюще- го блока PCU в архитектуре Skylake подверглась значительным дора- боткам для достижения более динамичных режимов с высокими уров- нями производительности и агрессивными алгоритмами энергосбере-

жения, в том числе, в плане сбора внутренней статистики, внешней и внутренней телеметрии (iMon, Psys) и более тесного взаимодействия со старшими в иерархии системами управления (OS, BIOS).

Самое заметное и, пожалуй, существенное изменение в архитекту- ре Skylake связано с новым интегрированным контроллером оператив- ной памяти: он по-прежнему 2-канальный, однако теперь поддерживает

динамическую память как предыдущего стандарта DDR3L, так и нового поколения DDR4. Прежде полноценный контроллер DDR4 был на во- оружении только серверных чипов Xeon и выполненных на основе их дизайна топовых геймерских LGA 2011 чипах Intel Core i7, но фактиче- ски именно начиная со Skylake память DDR4 начинает своё широко- масштабное наступление на рынок настольных и мобильных систем.

Модуль аппаратной обработки мультимедийного контента и фи- нального рендеринга видеопотока в архитектуре Skylake также значи- тельно доработан и улучшен. В частности, аппаратный кодек HEVC/H265 нового поколения обладает повышенной производительно- стью с одновременным уменьшением энергопотребления; есть отдель- ный аппаратный кодек AVC с очень низким энергопотреблением; обес- печивается вывод изображения на три независимых 4K-дисплея со сни- женным на 40%-60% потреблением энергии даже в самом тяжёлом ре- жиме воспроизведения 4K-видео.

В дополнение, архитектура Skylake также поддерживает инициати- ву Intel по отказу от проводных подключений для беспроводной переда- чи мультимедийного контента с помощью технологий Intel WiDi или Pro WiDi с компьютеров на телевизоры, мониторы или проекторы.

Впервые в составе архитектуры для массовых процессоров Skylake (а не специализированных SoC) появился так называемый встроенный процессор обработки изображений – ISP (Image Signal Processing), что особенно актуально для смартфонов, планшетов и ноутбуков. В частно- сти, ISP обладает встроенным интерфейсом CSI (Camera Sensor Interface) с поддержкой до четырех внешних цифровых камер/сенсоров с разрешением до 13 Мп, правда, с одновременным обслуживанием только двух из них. Аппаратная обвязка CSI поддерживает расширен- ный список технологий для полноценной обработки фото и видео, включая распознавание и запоминание лиц, групповые снимки, много- поточный захват, съёмку с расширенным динамическим диапазоном (HDR), съёмку при слабом освещении, серийную съёмку и многое дру-

гое.

Роль графических ядер, встроенных в процессоры, с каждым годом увеличивается. И это связано не столько с ростом их 3D-

производительности, столько с тем, что встроенные GPU берут на себя всё новые функции, такие как параллельные вычисления или кодирова- ние и декодирование мультимедийного контента. Исключением не ста- ло и графическое ядро Skylake. Intel относит его к следующему, девято- му поколению, и это значит, что в нём таится немало сюрпризов. Одна- ко начать стоит с того, что GPU, реализованный в Skylake, как и его предшественники, сохранил традиционный модульный дизайн. Таким образом, мы вновь имеем дело с целым семейством решений разного класса: на базе имеющихся строительных блоков нового поколения Intel может собирать кардинально различающиеся по уровню производи- тельности GPU. Подобная масштабируемость сама по себе новинкой не является, но в Skylake возросла не только максимальная производитель- ность, но и число доступных вариантов графического ядра.

Итак, графическое ядро Skylake может быть построено на базе од- ного или нескольких модулей, каждый из которых обычно включает в себя по три секции. Секции объединяют по восемь исполнительных устройств, на которые ложится основная часть обработки графических данных, а также содержат базовые блоки для работы с памятью и тек- стурные семплеры. Помимо исполнительных устройств, сгруппирован- ных в модули, графическое ядро содержит и внемодульную часть, отве- чающую за фиксированные геометрические преобразования и отдель- ные мультимедийные функции.

На самом верхнем уровне иерархии графическое ядро Skylake очень похоже на ядро, реализованное в Broadwell. Однако если углу- биться в подробности, то нетрудно найти и заметные изменения.

Во-первых, внемодульная часть вынесена теперь в отдельный энер- гетический домен, что позволяет задавать ей частоту и отправлять её в сон отдельно от исполнительных устройств. Это значит, что, например,

при работе с технологией Quick Sync, которая реализуется как раз сила- ми внемодульных блоков, основная часть GPU может быть отключена от линий питания в целях снижения энергопотребления. Кроме того, не- зависимое управление частотой внемодульной части позволяет лучше подстраивать её производительность под конкретные нужды модулей графического ядра.

Во-вторых, в то время как графическое ядро Broadwell могло осно- вываться лишь на одном или двух модулях, получая в своё распоряже- ние 24 или 48 исполнительных устройств (для энергоэффективных и бюджетных процессоров мог использоваться один модуль с отключен- ными секциями, что давало меньшее, чем 24, число исполнительных устройств), в Skylake может применяться от одного до трёх модулей.

Благодаря этому в дополнение к привычным конфигурациям GT1/GT2/GT3 в семействе процессоров Skylake будет доступно ещё бо- лее мощное ядро GT4 (рис. 3.22), которое получит 72 исполнительных устройства.

Однако пиковая производительность самих исполнительных устройств в Skylake не изменилась – каждое такое устройство может выполнять до 16 32-битных операций за такт. При этом оно способно исполнять 7 вычислительных потоков одновременно и имеет 128 32- байтовых регистров общего назначения.

В-третьих, варианты ядра GT3 и GT4 могут быть дополнительно усилены eDRAM-буфером объёмом 64 или 128 Мбайт соответственно, что даёт модификации GT3e и GT4e. Процессоры Broadwell комплекто- вались лишь одним вариантом eDRAM – объёмом 128 Мбайт. В Skylake же этот дополнительный буфер не только изменил алгоритм работы, став «кешем на стороне памяти», но и приобрёл некоторую гибкость конфигурации. Однако его исполнение останется старым – он будет представлен отдельным 22-нм кристаллом, монтируемым на процессор- ную плату по соседству с основным чипом.

-

Микропроцессоры семейства «Эльбрус»

В 1969 году в связи с необходимостью в высокопроизводительной вычислительной технике для оснащения в нашей стране стратегических систем специального назначения возникла идея разработки многопро- цессорных вычислительных комплексов (МВК) семейства «Эльбрус». Основоположником идеи был Лебедев С.А., а главным конструктором прокта в Институте точной механики и вычислительной техники (ИТМ и ВТ) стал Бурцев В.С.

Разработка МВК «Эльбрус-1» началась в 1973 г., закончена в 1979 г. и сдана госудраственной комисси в 1980 г. Данный вычислительный комплекс был построен на базе TTL-микросхем.

Затем был построен МВК «Эльбрус-2». Годы разработки 1977- 1984, сдан в 1985 г. Данный комплекс в течении нескольких лет исполь- зовался в центральных объектах стратегических систем страны.

Следующим проектом стал МВК «Эльбрус-3». Руководителем про- екта был Бабаян Б.А. Опытный образец данного комплекса был изго- товлен в 1990 году, но в связи с прекращением финансирования отладка образца не была завершена.

Рис. 3.22. Структура графического ядра Skylake

Стало ясно, что будущие поколения вычислительной техники должны базироваться на микропроцессорах. В 1992 г. коллектив разра- ботчиков машин семейства «Эльбрус» выделился в компанию ЗАО

«МЦСТ – Московский центр SPARC-технологий» и совместно с ОАО

«ИНЭУМ имени И.С. Брука» начал вести работы над микропроцессор- ной реализацией разработанной архитектуры.

Основой серии осталась оригинальная архитектура «Эльбрус», а также добавилась открытая архитектура SPARC «Scalable Processor Ar- chitecture» (табл. 3.2).

Таблица 3.2 Разработка линии микропроцессоров «Эльбрус»

| Микропроцессор | «Эльбрус» | «Эльбрус- 2С» | «Эльбрус- 4С» | «Эльбрус- 8С» |

| Технологическое разрешение, нм | 130 | 90 | 65 | 28 |

| Год выпуска | 2007 | 2010 | 2012 | 2014 |

| Чисто процессорных ядер | 1 | 2 | 4 | 8 |

| Частота, МГц | 300 | 600 | 800 | 1300 |

| Производительность, GFlops | 4,8 | 19,2 | 50 | 250 |

| Мощность, Вт | 6 | 16 | 25 | 60 |