Файл: Пк 1 Синтезирование цифрового устройства q1 если d0 d9 d12.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 11.01.2024

Просмотров: 82

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

разряд числа, записанного в двоичном коде.

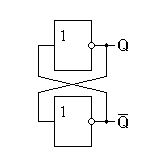

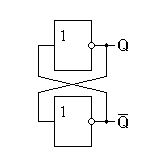

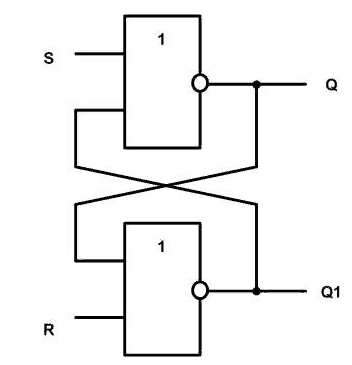

Рисунок 1. Схема простейшего триггера, построенного на логических инверторах

Виды триггеров:

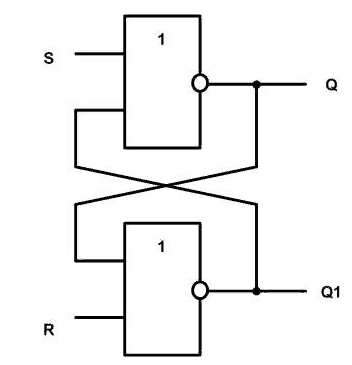

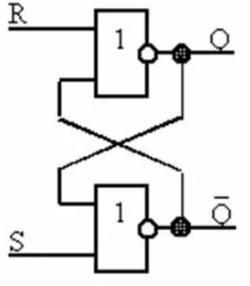

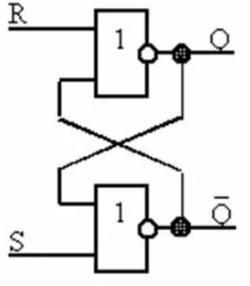

RS-триггер — асинхронный триггер, который сохраняет своё предыдущее состояние при неактивном состоянии обоих входов и изменяет своё состояние при подаче на один из его входов активного уровня. При подаче на оба входа активного уровня состояние триггера вообще говоря неопределённо, но в конкретных реализациях на логических элементах оба выхода принимают состояния либо логического нуля, либо логической 1. В зависимости от конкретной реализации активным входным уровнем может быть как логическая 1, так и логический 0. Так, в RS-триггере выполненном на 2 элементах 2И-НЕ активным входным уровнем является логический 0.

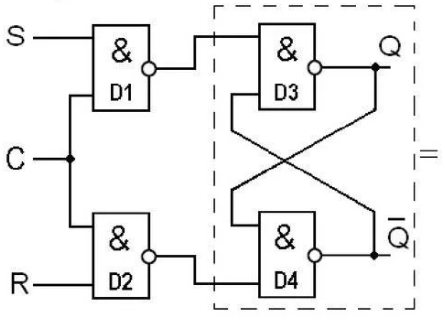

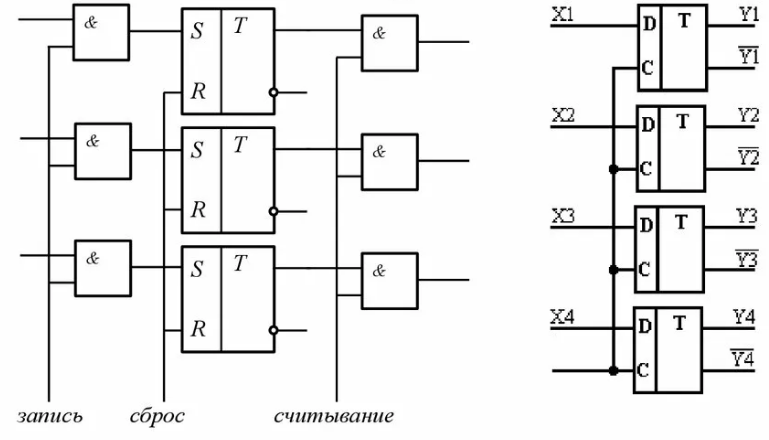

Рисунок 3. Схема простейшего RS триггеров.

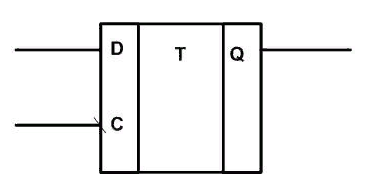

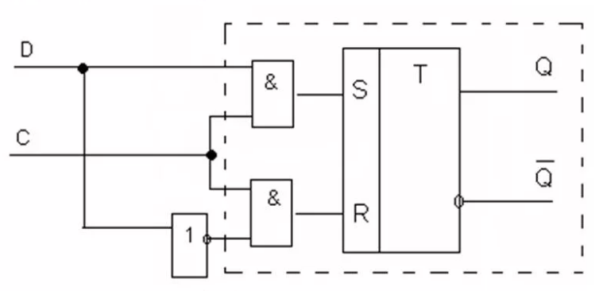

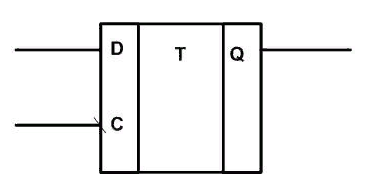

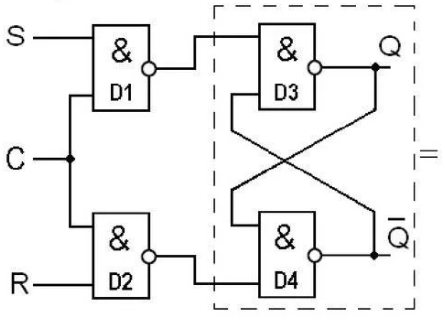

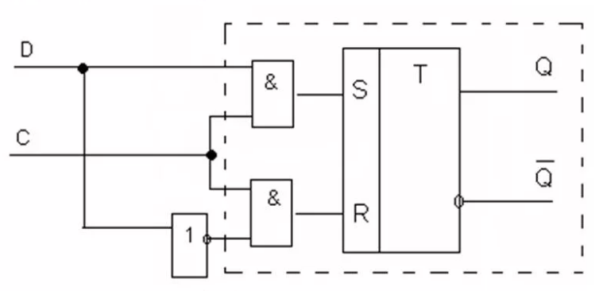

D-триггер — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1, такие триггеры иногда называют "прозрачной защёлкой". В триггерах с динамическим входом С информация записывается со входа D в состояние триггера только в момент перепада напряжения на входе С. Динамический вход изображают на схемах треугольником или наклонной чертой. Если вершина треугольника обращена в сторону микросхемы или косая черта в виде слэша (прямой динамический вход), то триггер срабатывает по фронту импульса, если треугольник повёрнут от изображения микросхемы или косая черта в виде обратного слэша (инверсный динамический вход) — то по спаду импульса.

Рисунок 8. Условно-графическое обозначение D триггера.

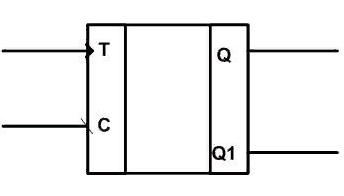

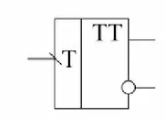

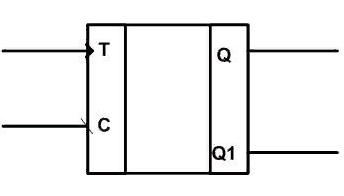

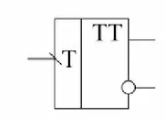

Т-триггер часто называют счётным триггером, так как он является простейшим счётчиком

по модулю 2. Синхронный Т-триггер, при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе.

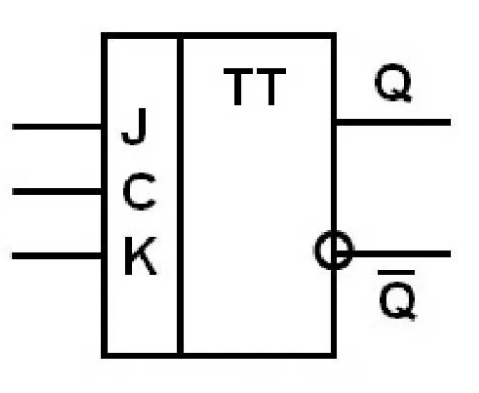

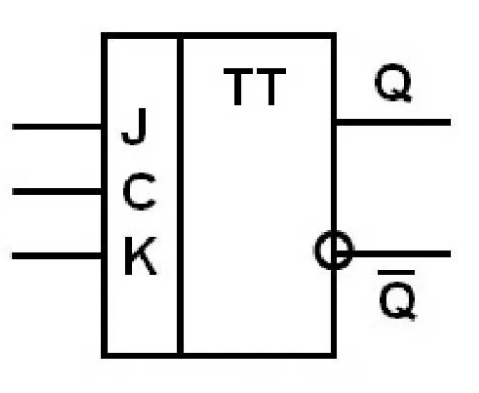

Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К.

В двухступенчатом (Master-Slave, MS) D-триггере инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение Q, то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для деления частоты на 2, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

Рисунок 9. Условно-графическое обозначение Т триггеров.

Счётчик

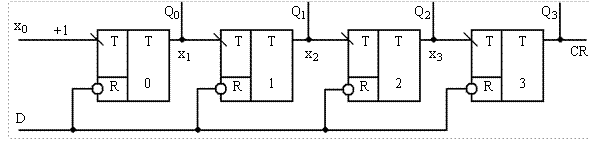

Счётчик — электронное устройство для подсчета количества импульсов, поступающих на его вход, с помощью непрерывного суммирования; или для определения степени накопления какой-либо величины во времени, методом интегрирования значения текущего измерения. Примером простейшего счетчика, считающего до 2 является Т - триггер.

Классификация счетчиков

По коэффициенту (модулю) счета:

По направлению счета:

По способу организации внутренних связей:

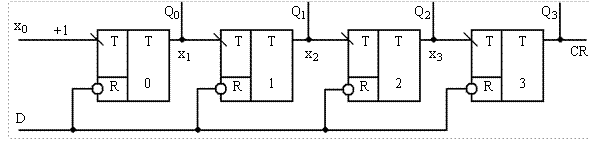

Рисунок. Счётчик

Регистр

Регистр — это последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Классификация регистров.

По функциональным свойствам:

По способу ввода и вывода информации:

По направлению передачи информации:

По количеству разрядов:

Типы регистров

Регистры различают по типу ввода (загрузки, приёма) и вывода (выгрузки, выдачи) информации:

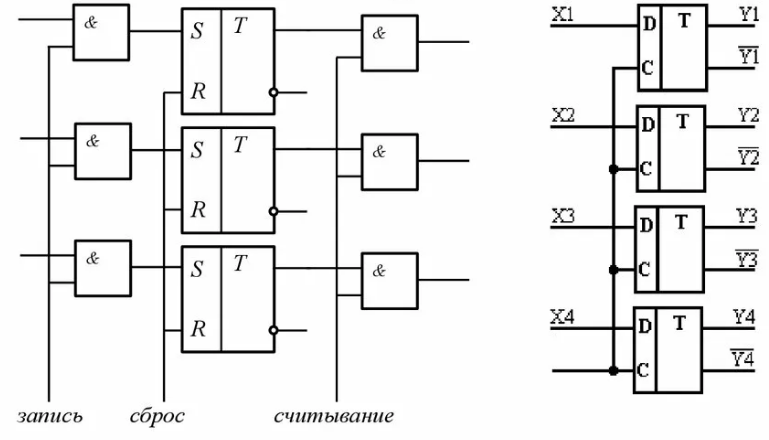

Рисунок. Регистр памяти

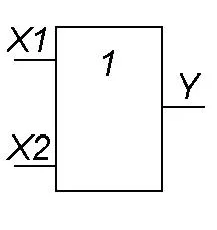

Шифратор

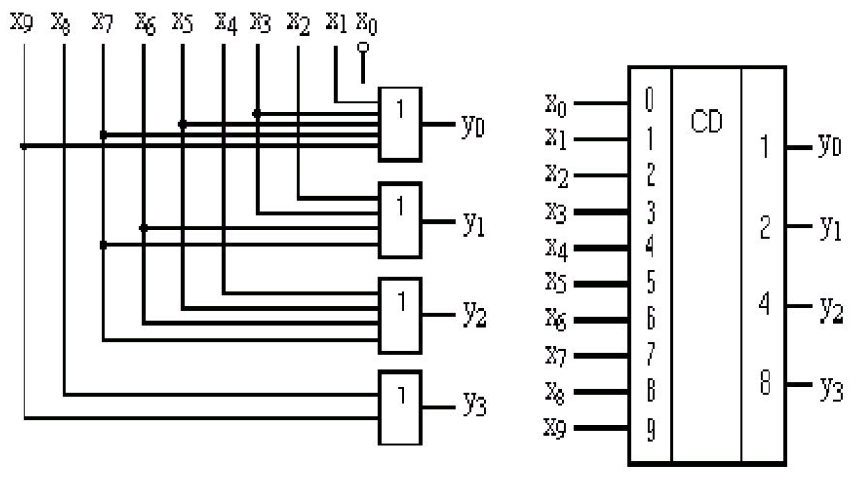

Шифратор— это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду.

Виды шифраторов

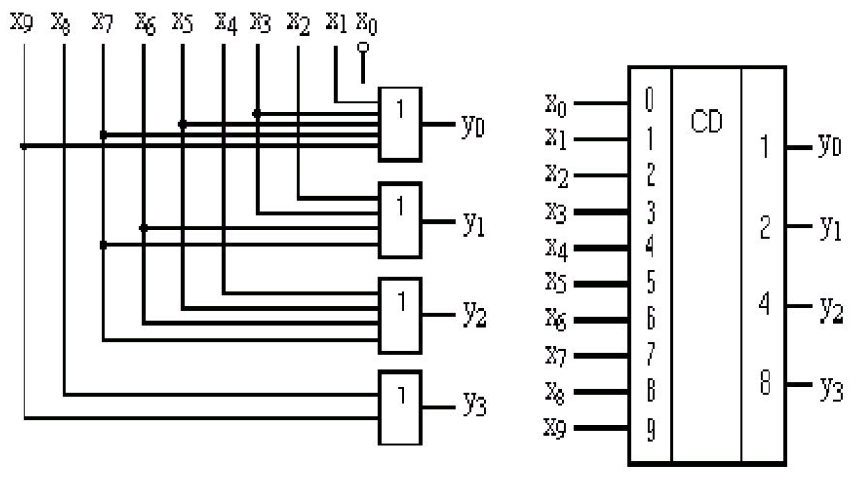

Рисунок. Шифратор

Дешифратор

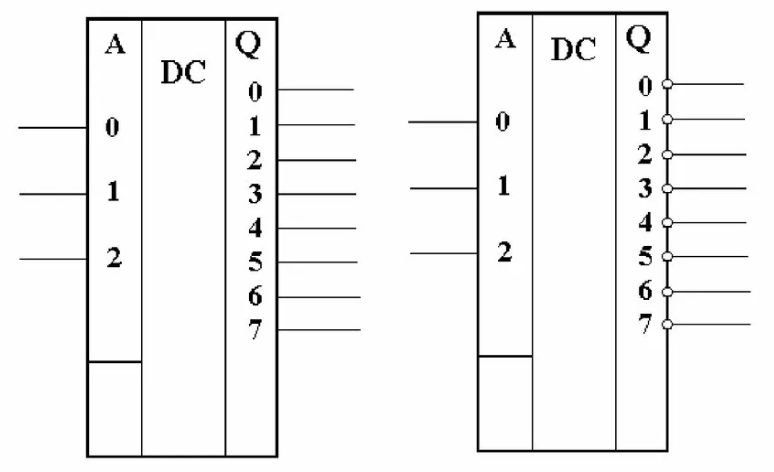

Дешифраторомназывается комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду.

Дешифраторы решают следующие задачи:

Дешифраторы выпускаются в виде отдельных микросхем или используются в составе других микросхем. В настоящее время десятичные или восьмеричные дешифраторы используются в основном как составная часть других микросхем, таких как мультиплексоры, демультиплексоры, ПЗУ или ОЗУ.

Классификация дешифраторов:

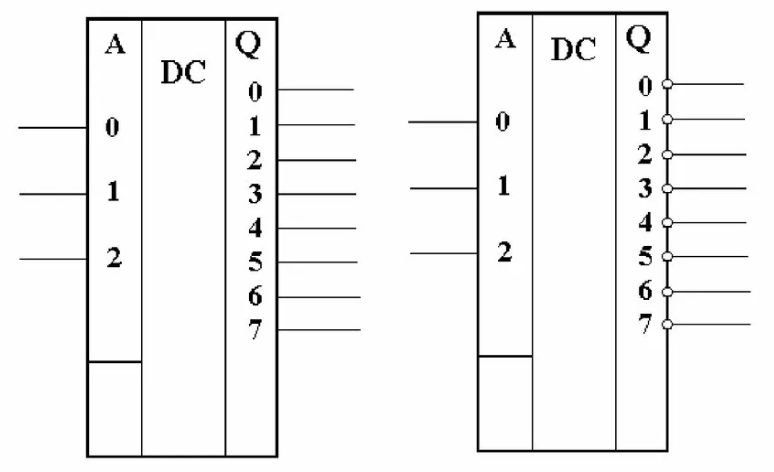

Рисунок. Дешифраторы

ПК 1.3 Моделирование цифровых схем, состоящих из логических вентилей. Описание логики работы цифрового устройства.

Цель работы изучение логических операций и правил их преобразований. Получение навыков практической работы по моделированию цифровых систем, состоящих из логических вентилей.

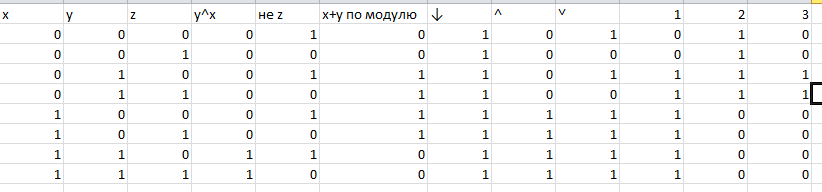

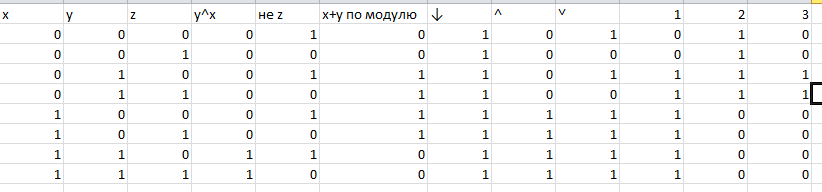

Рисунок 1. Таблица истинности

Рисунок 1. Таблица истинности

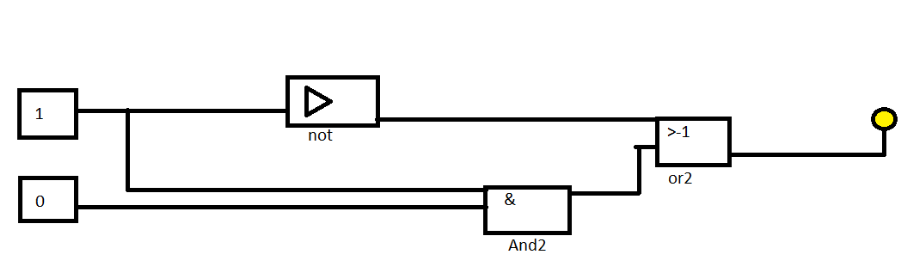

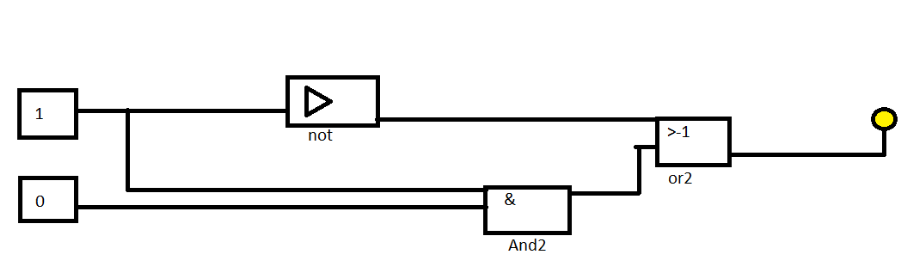

Рисунок 2. Примерная Схема логической функции

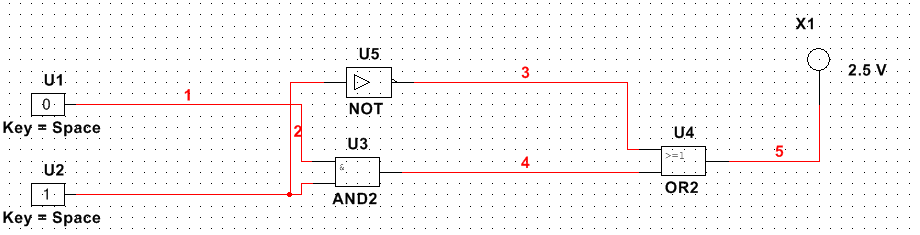

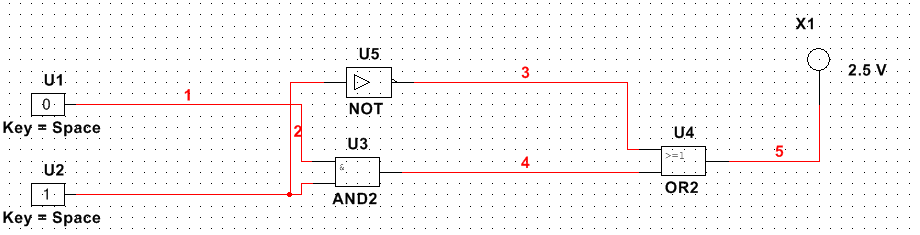

Рисунок 3. Схема логической функции в среде Multisim

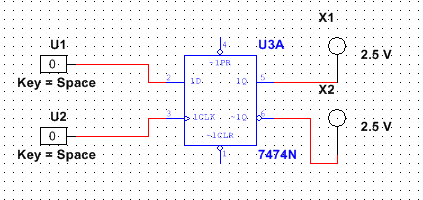

В рамках моделирования была создана схема D-триггера. В данной схеме использовались следующие элементы: конъюнктур, инвертор, лампы (в качестве выходных сигналов). Рисунок

Рисунок . Модель D-триггера в среде Multisim

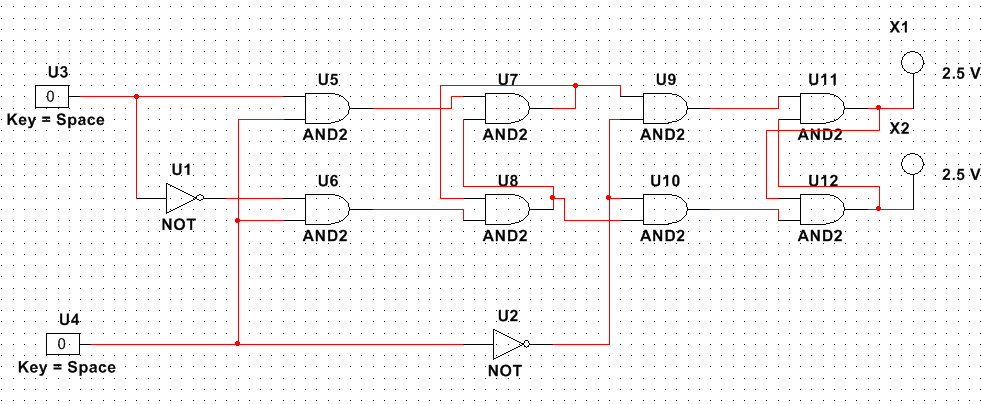

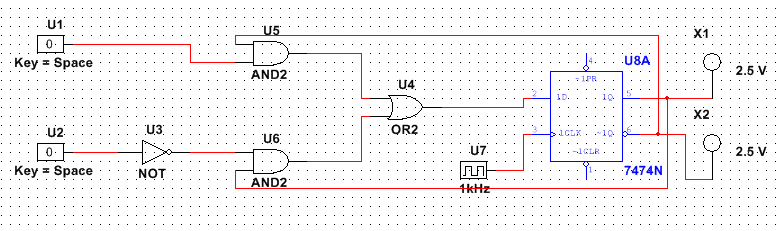

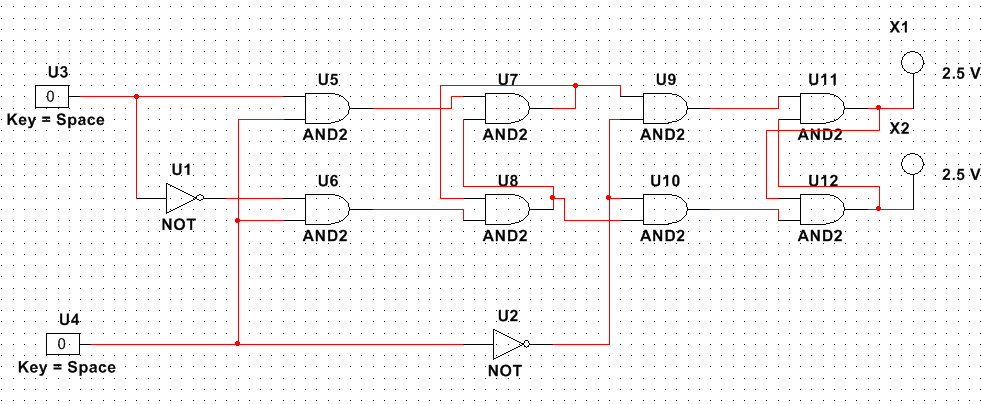

На основе D-триггера была создана схема JK-триггера. В данной схеме использовались следующие элементы: конъюнктур, дизъюнктор, инвертор, D-триггер, лампы (в качестве выходных сигналов). Рисунок

Рисунок . Модель JK-триггера в среде Multisim

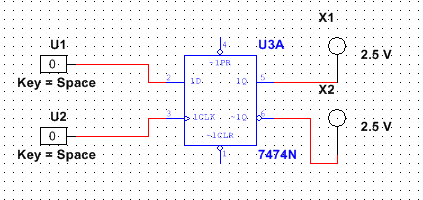

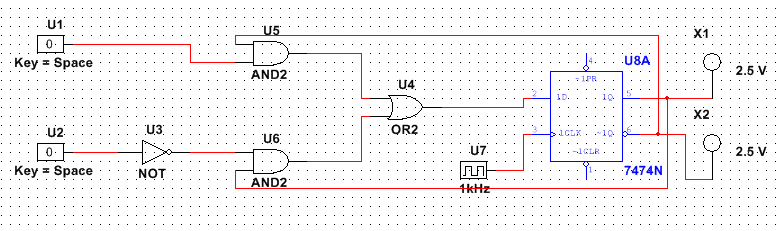

Смоделирована схема T-триггера. В данной схеме использовались следующие элементы: D-триггер, лампы (в качестве выходных сигналов). Рисунок

Рисунок . Модель T-триггера в среде Multisim

ПК 1.5

Асинхронный RS-триггер Синхронный RS-триггер

JK-триггер D-триггер

Т-триггер

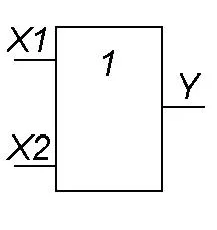

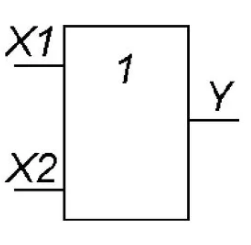

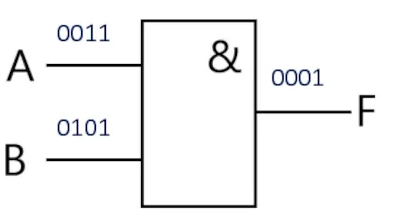

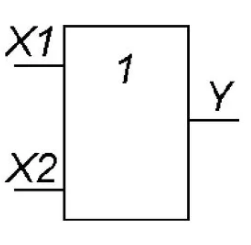

Конъюнктур (элемент «И») Дизъюнктор (Элемент «ИЛИ»

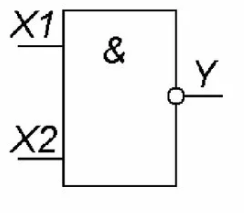

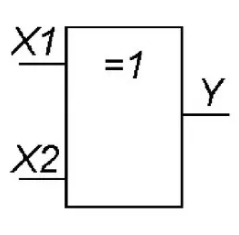

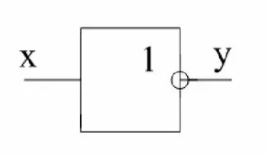

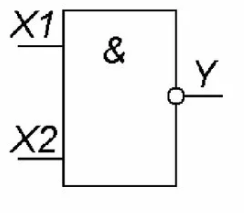

Элемент «И-НЕ» Элемент «ИЛИ-НЕ»

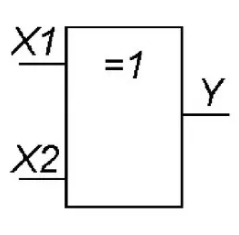

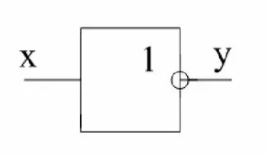

Элемент «исключающее ИЛИ» Элемент «НЕ»

Рисунок 1. Схема простейшего триггера, построенного на логических инверторах

Виды триггеров:

RS-триггер — асинхронный триггер, который сохраняет своё предыдущее состояние при неактивном состоянии обоих входов и изменяет своё состояние при подаче на один из его входов активного уровня. При подаче на оба входа активного уровня состояние триггера вообще говоря неопределённо, но в конкретных реализациях на логических элементах оба выхода принимают состояния либо логического нуля, либо логической 1. В зависимости от конкретной реализации активным входным уровнем может быть как логическая 1, так и логический 0. Так, в RS-триггере выполненном на 2 элементах 2И-НЕ активным входным уровнем является логический 0.

Рисунок 3. Схема простейшего RS триггеров.

D-триггер — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1, такие триггеры иногда называют "прозрачной защёлкой". В триггерах с динамическим входом С информация записывается со входа D в состояние триггера только в момент перепада напряжения на входе С. Динамический вход изображают на схемах треугольником или наклонной чертой. Если вершина треугольника обращена в сторону микросхемы или косая черта в виде слэша (прямой динамический вход), то триггер срабатывает по фронту импульса, если треугольник повёрнут от изображения микросхемы или косая черта в виде обратного слэша (инверсный динамический вход) — то по спаду импульса.

Рисунок 8. Условно-графическое обозначение D триггера.

Т-триггер часто называют счётным триггером, так как он является простейшим счётчиком

по модулю 2. Синхронный Т-триггер, при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе.

Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К.

В двухступенчатом (Master-Slave, MS) D-триггере инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение Q, то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для деления частоты на 2, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

Рисунок 9. Условно-графическое обозначение Т триггеров.

Счётчик

Счётчик — электронное устройство для подсчета количества импульсов, поступающих на его вход, с помощью непрерывного суммирования; или для определения степени накопления какой-либо величины во времени, методом интегрирования значения текущего измерения. Примером простейшего счетчика, считающего до 2 является Т - триггер.

Классификация счетчиков

По коэффициенту (модулю) счета:

-

двоичные (бинарные); -

двоично-десятичные (декадные); -

с произвольным постоянным модулем счета; -

с переменным модулем.

По направлению счета:

-

суммирующие; -

вычитающие; -

реверсивные.

По способу организации внутренних связей:

-

с последовательным переносом; -

с параллельным переносом; -

с комбинированным переносом; -

кольцевые.

Рисунок. Счётчик

Регистр

Регистр — это последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Классификация регистров.

По функциональным свойствам:

-

накопительные регистры (регистры памяти, хранения); -

сдвигающие регистры (регистры сдвига вправо, влево, реверсивные); -

приёмные регистры; -

передающие регистры;

По способу ввода и вывода информации:

-

параллельные регистры (регистры памяти); -

последовательные регистры (регистры сдвига); -

комбинированные регистры (параллельно-последовательные, последовательно-параллельные);

По направлению передачи информации:

-

однонаправленные; -

реверсивные.

По количеству разрядов:

-

трёхразрядные регистры; -

четырёхразрядные регистры; -

пятиразрядные регистры и т.д.

Типы регистров

Регистры различают по типу ввода (загрузки, приёма) и вывода (выгрузки, выдачи) информации:

-

с последовательным вводом и выводом информации; -

с параллельным вводом и выводом информации; -

с параллельным вводом и последовательным выводом. Например: SN74LS165J(N), SN74166J(N), SN74LS166J(N); -

с последовательным вводом и параллельным выводом. Например: SN7416J(N), SN74LS164J(N), SN74LS322J(N), SN74LS673J(N).

Рисунок. Регистр памяти

Шифратор

Шифратор— это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду.

Виды шифраторов

-

двоичный шифратор выполняет логическую функцию преобразования унитарного n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов на выходе появляется двоичный код номера активного входа; -

троичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного кода в троичный. При подаче сигнала на один из n входов на выходе появляется троичный код номера активного входа; -

приоритетный шифратор отличается от шифратора наличием дополнительной логической схемы выделения активного уровня старшего входа для обеспечения условия работоспособности шифратора. Уровни сигналов на остальных входах схемой игнорируются.

Рисунок. Шифратор

Дешифратор

Дешифраторомназывается комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду.

Дешифраторы решают следующие задачи:

-

преобразование двоично-десятичного кода в десятичное число; -

преобразование двоично-десятичного кода в семеричный код, необходимый для индикации десятичного числа.

Дешифраторы выпускаются в виде отдельных микросхем или используются в составе других микросхем. В настоящее время десятичные или восьмеричные дешифраторы используются в основном как составная часть других микросхем, таких как мультиплексоры, демультиплексоры, ПЗУ или ОЗУ.

Классификация дешифраторов:

-

По числу разрядов. -

В зависимости от преобразованных кодов:

-

двоично-десятичный код в семисегментный; -

двоичный код в десятичное число.

-

По принципу действия:

-

линейный (матричный, или одноступенчатый); -

пирамидальный (многоступенчатый).

Рисунок. Дешифраторы

ПК 1.3 Моделирование цифровых схем, состоящих из логических вентилей. Описание логики работы цифрового устройства.

Цель работы изучение логических операций и правил их преобразований. Получение навыков практической работы по моделированию цифровых систем, состоящих из логических вентилей.

-

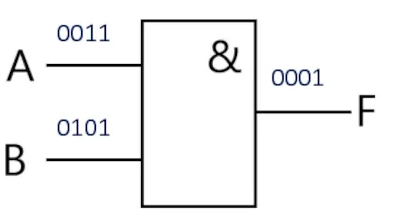

Создание таблицы истинности (в среде Microsoft Excel) для заданной булевой функции (таблицу истинности строить без каких-либо упрощении, пользуясь лишь встроенным функциями И, ИЛИ, НЕ, ЕСЛИ).

Рисунок 1. Таблица истинности

Рисунок 1. Таблица истинности -

Создание примерной схемы логической функции в paint

Рисунок 2. Примерная Схема логической функции

-

Моделирование логической схемы в среде Multisim.

Рисунок 3. Схема логической функции в среде Multisim

В рамках моделирования была создана схема D-триггера. В данной схеме использовались следующие элементы: конъюнктур, инвертор, лампы (в качестве выходных сигналов). Рисунок

Рисунок . Модель D-триггера в среде Multisim

На основе D-триггера была создана схема JK-триггера. В данной схеме использовались следующие элементы: конъюнктур, дизъюнктор, инвертор, D-триггер, лампы (в качестве выходных сигналов). Рисунок

Рисунок . Модель JK-триггера в среде Multisim

Смоделирована схема T-триггера. В данной схеме использовались следующие элементы: D-триггер, лампы (в качестве выходных сигналов). Рисунок

Рисунок . Модель T-триггера в среде Multisim

ПК 1.5

Асинхронный RS-триггер Синхронный RS-триггер

JK-триггер D-триггер

Т-триггер

Конъюнктур (элемент «И») Дизъюнктор (Элемент «ИЛИ»

Элемент «И-НЕ» Элемент «ИЛИ-НЕ»

Элемент «исключающее ИЛИ» Элемент «НЕ»