ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 11.01.2024

Просмотров: 71

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Если мы хотим хранить какую-либо двоичную последовательность цифр, то для каждой цифры следует использовать отдельный триггер. Для того чтобы получить данные о состоянии триггера, у него должна быть, по крайней мере, одна выходная линия, представляющая логическое значение, которое соответствует состоянию триггера. Когда на выходной линии логическая единица, говорят, что триггер установлен, в противном случае говорят, что триггер сброшен. Триггер имеет несколько входных линий. Последующее состояние триггера определяется текущим состоянием триггера и сигналами на входных линиях. Триггер обозначается прямоугольником, разделенным на основное и вспомогательное поля. В первом помещают букву T (триггер), во втором — условные обозначения (метки) входов и логических операций на входе. Логика работы определяется количеством входов и особенностями схемы. В зависимости от влияния, оказываемого на состояние триггера, его входы имеют следующие обозначения:

S (Set-установка) — вход триггера для установки в состояние «1»;

R (Reset-сброс) — вход триггера для установки в состояние «0»;

J (Jump) — вход триггера для установки в состояние «1»

в JКтриггере, а вход К (key) - для установки в состояние 0, т.е. входы J и К аналогичны входам S и R RS-триггера;

K (Kill) — вход триггера для установки в состояние «0»

в JКтриггере;

D (Data input) — информационный вход. На него подается информация, предназначенная для записи в триггер;

T (Toggle-переключатель) — счетный вход (если у триггера только счетный вход, букву не пишут);

C (Clock input) — вход синхронизации.

В отечественных сериях микросхем триггеры имеют наименование ТВ, ТМ и ТР в зависимости от типа триггера. Наиболее распространены три типа:

RS-триггер (обозначается ТР) — самый простой триггер, но редко используемый;

JK-триггер (обозначается ТВ) имеет самое сложное управление, также используется довольно редко;

D-триггер (обозначается ТМ) — наиболее распространенный тип триггера. Простейшим из них является асинхронный RS-триггер (представлен на рисунке 2.3).

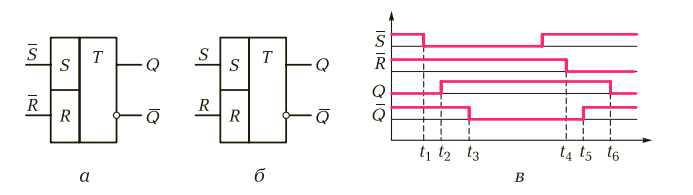

Рисунок 2.3 - Графическое обозначение асинхронного RS-триггера (а — с инверсными входами; б — с прямыми входами) и временная диаграмма (в)

Кроме асинхронного RS-триггера существует синхронный RS-триггер рисунок 2.2. Синхронные триггеры снабжаются дополнительным входом, по которому поступает синхронизирующий (тактирующий) сигнал. При этом изменение состояния триггера происходит (при наличии управляющего сигнала) только в те моменты времени, когда на специальный синхровход триггера поступает тактирующий импульс. Синхронизирующий вход обозначается буквой С.

Входные сигналы, по которым происходит переключение триггера: S и R — информационные и С — синхронизирующие.

Все триггеры с синхронизирующим входом, которые управляются уровнем синхронизирующего сигнала, являются триггерами со статическим управлением.

Схемы RS-триггеров являются одноступенчатыми. Применение одноступенчатых RS-триггеров в качестве самостоятельных запоминающих элементов ограничено.

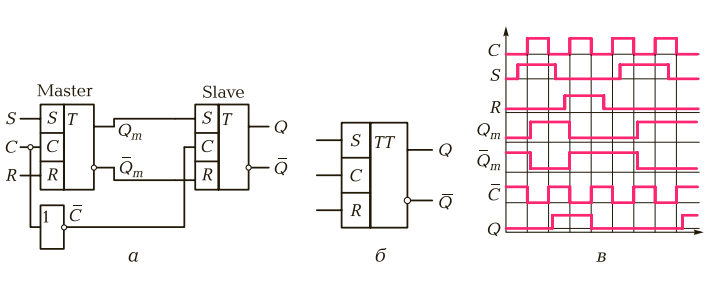

Большей востребованностью пользуются двухступенчатые триггеры (MS-триггеры) (представлен на рисунке 2.4)

Рисунок 2.4 - Структурная схема (а), графическое обозначение (б)

и временная диаграмма (в) MS-триггера

Для построения двухступенчатых триггеров используются одноступенчатые RS-триггеры. Двухступенчатый триггер состоит из двух каскадных секций (ступеней), причем каждая секция содержит по синхронному RS-триггеру. Первая секция, ведущая или М-секция (Master) принимает информацию с входных линий S и R. Состояние выходов ведущей секции подается на вторую секцию, ведомую, или S-секцию (от англ. Slave).

Если в обозначении синхронного RS-триггера с динамическим управлением стрелка на входе C направлена к триггеру, то передача сигналов с информационных входов на выходы происходит по фронту импульса, а если стрелка направлена от обозначения триггера, то передача сигнала осуществляется по спаду импульса.

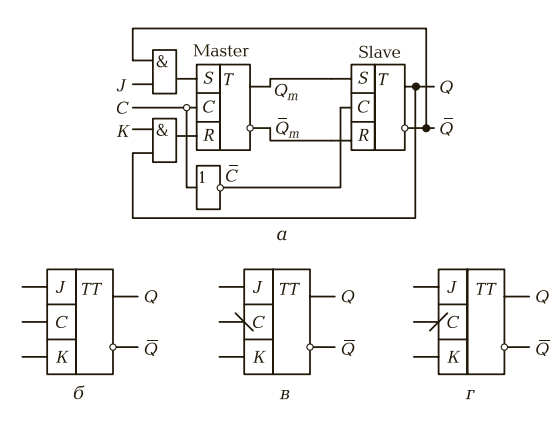

Рисунок 2.5 - JK-триггер со статическим управлением: а — структурная схема; б — графическое обозначение; графическое обозначение

JK-триггера с динамическим управлением: в — по заднему фронту;

г — по переднему фронту.

Для устранения недостатка RS-триггеров (режим неопределенности при R = S = 1) применяются динамические JK-триггеры с более широкими функциональными возможностями. JK-триггер можно синтезировать (построить) на базе MS-триггера.

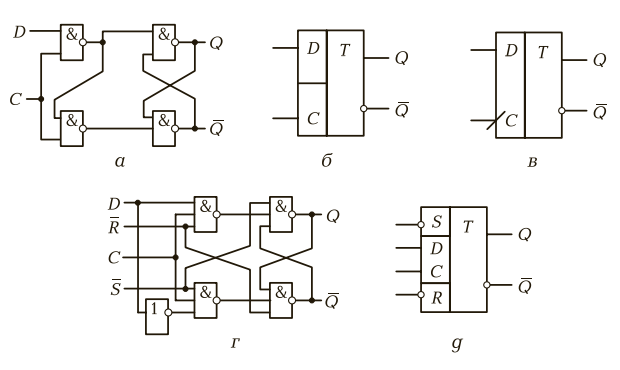

D-триггер (от англ. Delay). Схемное обозначение D-триггера приведено на рисунке 2.6.

Рисунок 2.6 - D-триггер со статическим управлением (а — структурная схема;

б — графическое обозначение); с динамическим управлением (в — графическое обозначение); с асинхронными инверсными входами установки и сброса S и R (г — структурная схема; д — графическое обозначение).

Он обладает двумя устойчивыми состояниями и имеет, как минимум, две входные линии: информационный вход D (Dаtа) и вход управления записью (защелкиванием) L (Load или Latch) — отсюда его второе имя: «защелка». Последний вход часто обозначают символом C(lock). D-триггер называют информационным триггером, а также триггером задержки. D-триггер бывает только синхронным. Для триггера типа D состояние в интервале времени между сигналом на входной линии и следующим состоянием триггера формируется проще, чем для любого другого типа.

Если на вход S подать 0, а на вход R — сигнал 1, то Q = 1 и Q = 0 независимо от сигналов на остальных входах. Триггер устанавливается в единицу. Сигналы D и C не влияют на этот процесс. В силу этого, асинхронные входы (S и R) имеют наивысший приоритет. Так как асинхронные связи симметричны, при S = 1 и R = 0 триггер сбрасывается (Q = 0).

3 ЛИНЕЙНАЯ, СТРАНИЧНАЯ, СЕГМЕНТНАЯ ПАМЯТЬ

Линейная адресация памяти — схема адресации памяти компьютера в Intel-совместимых процессорах, начиная с Intel 80386.

Благодаря введению механизма линейной адресации можно создавать любое (ограниченное только размерами оперативной памяти) количество адресных пространств. Причём каждая страница линейного адресного пространства может находиться по любому (естественно, выравненному по границе 4 КБайт) физическому адресу, а благодаря обработчику #PF — и на любом накопителе [3].

Страничная память — способ организации виртуальной памяти, при котором единицей отображения виртуальных адресов на физические является регион постоянного размера (т. н. страница). Типичный размер 4096 байт, для некоторых архитектур до 128 КБ.

Поддержка такого режима присутствует в большинстве 32битных и 64битных процессоров. Такой режим является классическим для почти всех современных ОС, в том числе Windows и семейства UNIX. Широкое использование такого режима началось с процессора VAX и ОС VMS с конца 70х годов (по некоторым сведениям, первая реализация). В семействе x86 поддержка появилась с поколения 386, оно же первое 32битное поколение.

Сегментная адресация памяти — схема логической адресации памяти компьютера в архитектуре x86. Линейный адрес конкретной ячейки памяти, который в некоторых режимах работы процессора будет совпадать с физическим адресом, делится на две части: сегмент и смещение. Сегментом называется условно выделенная область адресного пространства определённого размера, а смещением — адрес ячейки памяти относительно начала сегмента. Базой сегмента называется линейный адрес (адрес относительно всего объёма памяти), который указывает на начало сегмента в адресном пространстве. В результате получается сегментный (логический) адрес, который соответствует линейному адресу база сегмента+смещение и который выставляется процессором на шину адреса.

Селектором называется число (в x86 — 16-битное), однозначно определяющее сегмент. Селектор загружается в сегментные регистры.

В реальном и защищённом режимах x86-процессора функционирование сегментной адресации отличается [4].

4 БАЗОВЫЕ ЛОГИЧЕСКИЕ ОПЕРАЦИИ И СХЕМЫ

Логическая переменная имеет только два значения ("истина" и "ложь"). В алгебре логики их обозначают как "1" и "0" и называют логической единицей и логическим нулем.

Существуют три основные операции над переменными:

-инверсия (логическое отрицание, функция НЕ);

-дизъюнкция (логическое сложение, функция ИЛИ);

- конъюнкция (логическое умножение, функция И).

Алгебра логики определяется следующей системой аксиом:

x = 0, если х≠1, ō= 1,

x = 1, если х≠0, ī= 0,

1+ 1 = 1, 0 * 0 = 0,

0 + 0 = 0, 1 * 1 = 1,

0 + 1 = 1 + 0 = 1, 1 * 0 = 0 * 1 + 0

Логические выражения связывают значение логической функции со значениями логических переменных. Они могут записываться или в конъюнктивной или дизъюнктивной нормальных формах. В дизъюнктивной форме логические выражения записываются как логическая сумма логических произведений, в конъюнктивной – как логическое произведение

логических сумм. Порядок действий в логических выражениях такой же, как и в обычных алгебраических выражениях. Логические выражения связывают значение логической функции со значениями логических переменных.

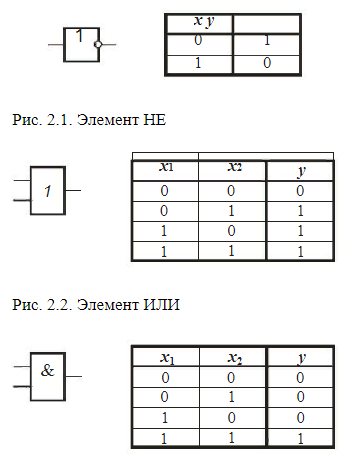

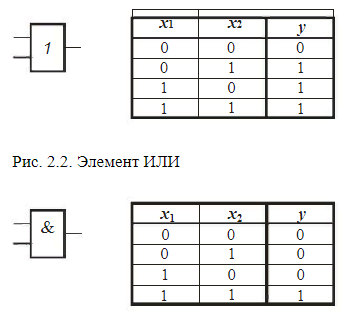

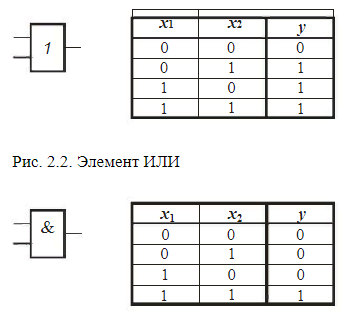

Основные логические функции могут быть реализованы с помощью электронных схем, называемых логическими элементами. Условные графические обозначения элементов и соответствующие им таблицы истинности приведены на рисунке 4.1-4.3.

Рисунок 4.1 - Элемент НЕ

Рисунок 4.2 - Элемент ИЛИ

Рисунок 4.3 - Элемент И

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

-

Земсков А.И., Шрайберг Я.Л. Электронные библиотеки: учебник для вузов. – М: Либерия, 2003 – 351 с. -

Костюк К.Н. Книга в новой медицинской среде. – М.: Директ – Медиа, 2015. – 430 с. -

Линейная, страничная, сегментная память [Электронный ресурс]. –URL: (дата обращения

06. 01.2023). -

Бесперстов Э.А. Исследование логических схем с использованием программного комплекса Multisim: лабораторный практикум. – СПб: БГТУ, 2006.

Перечень сокращений и обозначений:

Cc: (копия, carbon copy) — вторичные получатели письма, которым направляется копия. Они видят и знают о наличии друг друга.

Bcc: (скрытая копия, blind carbon copy) — скрытые получатели письма, чьи адреса не показываются другим получателям.