Файл: Протокол 1 от 28 августа 2020 г. Конспект лекций содержание введение Краткая характеристика дисциплины.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 12.01.2024

Просмотров: 411

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

Для выходов У необходимо составить 7 диаграмм Вейча-Карно по числу сегментов (выходов) индикаторов. Чтобы облегчить заполнение диаграмм заполним вначале шаблон диаграммы.

| | X4 | X   3 3 | | | | | ||||||||||

| | | | | | У1 |  |  | | 1 | | | ||||

| | | | | | | X  1 1 | |  | | | 1 | | | |||

| | | | | | | 1 | 1 | 1 | 0 | | | ||||

| | | | | | | | 0 | 1 | 1  | 1 | | | ||||

| |  |  | X2 | | | | | | |  |  | | | ||

| У2 | | |  | 1 | | У  3 3 |  | | | 1  | У4 |  | |  | 1 | |

| |  | | 1 | | |  | | | 1 |  | | | 1 | ||

| 0 | 1 | 1  | 1 | | | 1 | 1 | 1 | 1 | 1  | 0 | 1  | 0 | |||

| 1 | 0 | 1 | 1 | | | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | |||

| | |  |  | | |    |  | |||||||||

| У5 | | | | 1 | | У6 |  | | | 1 | | У7 |   | |  | 1 |

| | | | | 0 | | | | | | 1 | | | | | | 1 |

| | 0 | 0 | 0 | 0 | |  | 1 | 0 | 0 | 0 | | | 1 | 0 | 1 | 0 |

| | 0 | 1  | 1  | 1 | | | 1  | 1 | 0  | 1 | | | 1 | 1  | 1 | 0 |

Рисунок 18 – Диаграммы Вейча-Карно для семисегментного индикатора

Запишем логические выражения для выходов преобразователя:

Рисунок 19 – Логическая схема кодопреобразователя

2.1.6 СУММАТОРЫ

В любой вычислительной системе самым важным узлом является сумматор. Из всех 4-х арифметических операций (+,-,*,/) менее трудоёмким является сложение, все действия сводятся к нему с помощью специальных кодов (обратного, дополнительного, модифицированного и др.)

Различают сумматоры:

-

комбинационные (построены на логических элементах и не обладают памятью); -

накапливаемые (построенные на триггерах, которые способны запоминать информацию).

В зависимости от схемного решения различают сумматоры:

-

последовательного действия - одно и то же устройство должно сложить сначала цифры самого младшего разряда слагаемых, затем цифры соседнего старшего разряда и т.д.; -

параллельного действия - все разряды двух слагаемых подаются на его входы параллельно.

В зависимости от количества складываемых разрядов различают сумматоры:

-

одноразрядные - предназначены для сложения только одного разряда многоразрядного числа; -

многоразрядные - состоят из одноразрядных и предназначены для сложения многоразрядных чисел.

Сложение многоразрядных чисел осуществляется поразрядно начиная с младшего разряда с учётом возможности формирования сигналов переноса из младшего разряда, которые должны суммироваться с содержимым соседнего старшего разряда.

Рассмотрим одноразрядный сумматор (HS).

Такой сумматор называется неполным (полусумматор) HS имеет 2 входа слагаемых А и В и 2 выхода: выход суммы S и выход переноса P (рисунок 18)

Приведём таблицу истинности HS (таблица 6)

А1

В1

Рисунок 20 - УГО ИМС неполного (HS)

Правила сложения в HS соответствуют правилам двоичного сложения

Таблица 6 - Таблица истинности HS

| Входы | Выходы | ||

| А(Х1) | В(Х2) | S | P |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Запишем то ТН логические функции для выходов HS.

S =

P =

Построим логическую схему HS:

AX1)

-

S 1

BX2)

0 P 0

Рисунок 21 - Логическая схема HS

Рассмотрим многоразрядный сумматор. Такой сумматор называется полным (SM). SM имеет 2 входа слагаемых (Х1, Х2) и один вход переноса Pi (из предыдущего разряда). Для построения полного сумматора SM можно применить 2 полусумматора HS. Для обработки многоразрядных чисел объединяем совместно несколько SM.

Рисунок 22 - УГО ИМС SM

Таблица 7 - ТИ SM

| Входы | Выходы | |||

| А | В | Pi | Si | Pi+1 |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | ||

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | ||

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | ||

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | ||

Запишем логически выражения для выходов:

Si =

Pi+1 =

Рисунок 23 – Логическая схема многоразрядного сумматора SM

2.2 Триггерные устройства

2.2.1 ТРИГГЕРЫ

Триггер – это импульсное устройство, обладающее двумя устойчивыми состояниями («0» и «1»), в которых он может он находиться до тех пор, пока не придёт внешний управляющий сигнал.

Таким образом, триггер предназначен для хранения значения одной логической переменной. Простейший триггер имеет два входа и два выхода (рис. 24). Выходы обозначают Q и /Q. Выход Q называют прямым, a

В качестве элементов, на которых могут строиться триггеры, используются транзисторы, дискретные и логические элементы.

Различают типы триггеров: RS, T, D, JK.

Тип триггера по УГО определяется по названию его входов.

Триггеры могут иметь входы различного типа:

R (от англ. RESET) – раздельный вход установки в состояние 0;

S (от англ. SET) – раздельный вход установки в состояние 1;

К – вход установки универсального триггера в состояние 0;

J – вход установки универсального триггера в состояние 1;

V - вход разрешения;

С - синхронизирующий вход;

D - информационный вход;

Т - счетный вход

и некоторые другие.

Различают:

синхронные триггеры

асинхронные триггеры

В синхронных триггерах используется вход «синхро», который предназначен для управления работой триггера. Он разрешает триггеру установить состояние. Запись информации в таких триггерах осуществляется в момент поступления на синхронизирующий вход «С» импульса синхронизации.

Асинхронные триггеры имеют только информационные входы, и запись информации в них осуществляется в момент поступления этой информации на входы.

Состояние триггера определяется по сигналу, присутствующему на прямом выходе Q:

Q = 1 – «единичное»; Q = 0 – «нулевое».

Для изменения состояния триггера необходимо на его входы подать активные сигналы.

Активный сигнал – это сигнал, который способен изменить состояние триггера.

Пассивный сигнал

– это сигнал, который не изменяет состояния триггера.

а) для прямого входа b) для инверсного входа

Рисунок 24 – Значение активного сигнала для различных типов входа

Рисунок 25 – УГО некоторых типов триггеров

Существуют комбинированные триггеры (универсальные), которые могут работать по принципу любого из триггеров или совмещать в себе несколько триггеров. Состояние таких триггеров будет определяться в зависимости от способа подключения его входов и значения активных сигналов на них.

2.2.2 RS-триггер – это триггер с установочными входами.

Вход S– предназначен для установки триггера в «1» состояние (Q = 1) при подаче на него активного сигнала.

Вход R– предназначен для установки триггера в «0» состояние (Q = 0) при подаче на него активного сигнала.

Рассмотрим два варианта RS-триггера: RS-триггер с прямыми входами и RS-триггер с инверсными входами. Установка триггера в нужное состояние осуществляется подачей уровня логической «1» на соответствующий вход для триггера с прямыми входами и подачей сигналов логического «0» для триггера с инверсными входами.

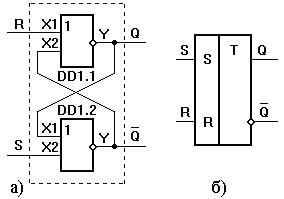

Наибольшее распространение получили RS-триггеры, построенные на логических элементах 2И-НЕ или 2ИЛИ-НЕ. Функциональная схема RS-триггера с прямыми входами на двух логических элементах 2ИЛИ-НЕ и его условное обозначение на принципиальных схемах приведены соответственно на рисунках 26 а,б.

Рисунок 26 – RS-триггер с прямыми входами: а) функциональная схема, б) УГО

Составим таблицу переходов для асинхронного RS-триггера с прямыми входами с учётом предыдущего состояния.

Таблица 8 – Таблица переходов RS-триггера с прямыми входами

| Входы | | | |

| | | ||

| 0 | 0 | 0 | 0  |

| 1 | 1 | ||

| 0 | 1 | 0 | 0  Установка «0» |

| 1 | 0 | ||

| 1 | 0 | 0 | 1  Установка «1» |

| 1 | 1 | ||

| 1 | 1 | 0 | -  Запрещённая комбинация |

| 1 | - | ||