Файл: Протокол 1 от 28 августа 2020 г. Конспект лекций содержание введение Краткая характеристика дисциплины.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 12.01.2024

Просмотров: 406

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

В принципе работы RS-триггера есть особенность: на его входы нельзя подавать два активных сигнала.

Для прямых входов:

Для инверсных:

Рисунок 27 – Граф функционирования

Такая комбинация называется запрещённой. Её не следует подавать на входы, так как в этом случае состояние триггера не будет точно определено (

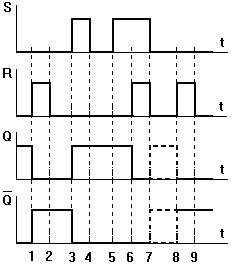

Рисунок 28 – Временная диаграмма работы RS-триггера с прямыми входами

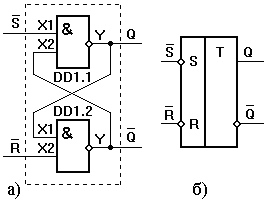

На рисунке 29,а приведена функциональная схема RS-триггера с инверсными входами на двух логических элементах 2И-НЕ, а на рисунке 6,б – его условное обозначение на принципиальных схемах.

Рисунок 29 – RS-триггер с инверсными входами: а) функциональная схема, б) УГО

Таблица переходов RS-триггера с инверсными входами имеет вид:

Таблица 9 – Таблица переходов RS-триггера с инверсными входами

| Входы | | | |

| | | ||

| 0 | 0 | 0 | - |

| 1 | - | ||

| 0 | 1 | 0 | 1 |

| 1 | 1 | ||

| 1 | 0 | 0 | 0 |

| 1 | 0 | ||

| 1 | 1 | 0 | 0 |

| 1 | 1 | ||

Рисунок 30 – Граф функционирования

Рассмотренные триггеры относятся к так называемым асинхронным триггерам. В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы. В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс.

Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигналов с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса.

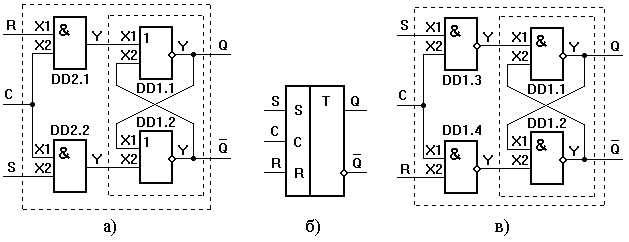

На рисунках 31,а,в приведены функциональные схемы синхронного RS-триггера с прямыми входами, а условное обозначение этих триггеров на принципиальных схемах показано на рисунке 31,б.

Рисунок 31 – Синхронный RS-триггер с прямыми входами: а), в) функциональные схемы, б) УГО

2.2.3 D-триггер – это триггер с задержкой. Является всегда синхронным. Он переходит в то состояние, которое соответствует логическому сигналу на входе D. При этом сигнал на выходе триггера появляется только после того, как закончится действие синхроимпульса.

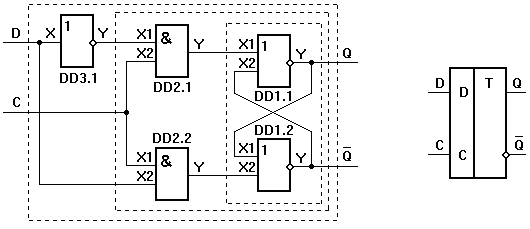

Функциональная схема D-триггера со статическим управлением и его условное обозначение на принципиальных схемах приведена на рисунке 32.

Рисунок 32 – D-триггера со статическим управлением:а) функциональная схема, б) УГО

Таблица переходов D-триггера имеет вид:

Таблица 10 – Таблица переходов D-триггера

| C | D | | |

| 0 | 0 | 0 | 0  |

| 1 | 1 Хранение | ||

| 1 | 0 | 0 | |

| 1 | 1 | ||

| 1 | 0 | 0 | 0  Установка «0» |

| 1 | 0 | ||

| 1 | 0 | 1  Установка «1» | |

| 1 | 1 |

Временная диаграмма работы D-триггера со статическим управлением приведена на рисунке 33.

Рисунок 33 – Временные диаграммы работы D-триггера

Из диаграммы следует, что передача информации с входа D на выход Q осуществляется во время действия синхронизирующего импульса.

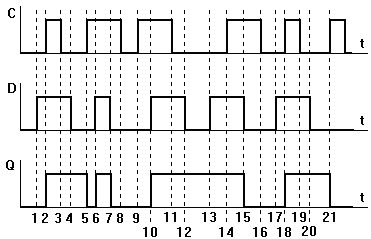

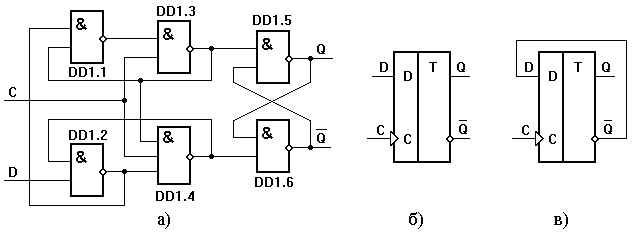

Широко используют D-триггеры с динамическим управлением. В них передача информации с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса. Функциональная схема D-триггера с передачей информации с входа на выход триггера по фронту синхронизирующего импульса приведена на рисунке 34,а, а его условное обозначение на принципиальных схемах – на рисунке 34,б.

Рисунок 34– D-триггера с динамическим управлением:а) функциональные схемы, б), в) УГО

D-триггер с динамическим управлением легко превратить в счетный триггер. С этой целью необходимо инверсный выход триггера соединить с информационным входом D, а импульсы подавать на синхронизирующий вход. Схема такого соединения приведена на рисунке 34,в.

2.2.4 JK-триггер – универсальный триггер. На его типе можно построить любой другой тип триггера.

Особенностью его работы является то, что при подаче на оба его входа J и K «1» (активного сигнала) триггер изменяет своё состояние на противоположное.

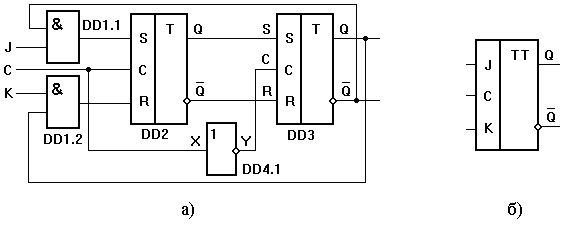

Функциональная схема JK-триггера, построенного с использованием двухтактных (двухступенчатых) RS-триггеров, приведена на рисунке 35,а, а его условное обозначение на принципиальных схемах – на рисунке 35,б.

Рисунок 35 – JK-триггер: а) функциональные схемы, б) УГО

Таблица переходов JK-триггера имеет вид:

Таблица 11 – Таблица переходов JK-триггера

| J | K | | |

| 0 | 0 | 0 | 0  Хранение |

| 1 | 1 | ||

| 1 | 0 | 0  Установка «0» | |

| 1 | 0 | ||

| 1 | 0 | 0 | 1  Установка «1» |

| 1 | 1 | ||

| 1 | 0 | 1  Режим счёта | |

| 1 | 0 |

Рисунок 36 – Временные диаграммы работы JK-триггера

Достоинства JK-триггера:

-

Не имеет запрещённых комбинаций. -

Является универсальным, то есть на его основе путём объединения входов можно получить любой другой триггер.

Рисунок 37 – Использование JK-триггера

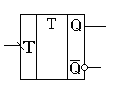

2.2.5 Т-триггер – это триггер со счётным входом. Он изменяет своё состояние на противоположное (

Рисунок 38 – Условно-графическое обозначение T-триггера.

Таблица переходов асинхронного Т-триггера имеет вид:

Таблица 12 – Таблица переходов асинхронного T-триггера

| T | | |

| 0 | 0 | 0  Хранение |

| 1 | 1 | |

| 1 | 0 | 1  Режим счёта |

| 1 | 0 |

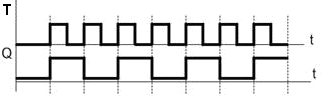

Рисунок 39 – Временные диаграммы работы асинхронного T-триггера

Таблица переходов синхронного Т-триггера имеет вид:

Таблица 13 – Таблица переходов синхронного T-триггера

| С | T | Qn=1 | Qn |

| 0 | * | 0 | 0  Хранение |

| 1 | 1 | ||

| 1 | 0 | 0 | 0  Хранение |

| 1 | 1 | ||

| 1 | 0 | 1  Режим счёта | |

| 1 | 0 |

Рисунок 40 – Временные диаграммы работы синхронного T-триггера

Асинхронный Т-триггер можно построить на RS-триггерах с входом «синхро», если использовать обратные связи:

Рисунок 41 – УГО Т-триггера, построенного на RS-триггере

За счёт обратной связи на одном из информационных входов R или S будет присутствовать «1». Поступление сигнала на вход С создаст комбинацию из двух активных сигналов RS-триггера, что вызовет изменение состояния триггера на противоположное.

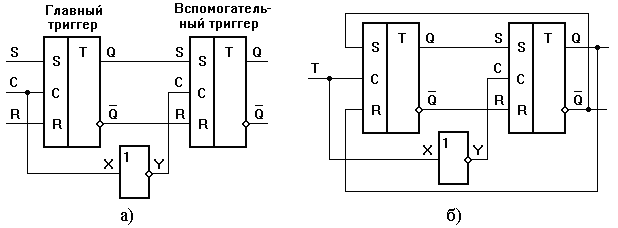

На рисунке 42 приведена схема счетного триггера, построенного на основе двухтактного RS-триггера. Двухтактный RS-триггер состоит из двух триггеров: главного и вспомогательного. Иногда главный триггер называют ведущим, а вспомогательный ведомым. По окончании синхронизирующего (тактового) импульса вспомогательный триггер переписывает информацию с выхода главного триггера.

Рисунок 42 – Двухтактная схема Т-триггера

2.3 Регистры памяти и сдвига

2.3.1 Регистры. Общие сведения. Назначение

Регистр (RG)– последовательностное цифровое устройство (ПЦУ), предназначенное для записи многоразрядных двоичных чисел, кратковременного их хранения и преобразования.

В качестве запоминающих элементов в регистрах используются триггеры.

Функции регистров:

- хранения двоично-кодированной информации;

- сдвига хранимого в регистре числа на определенное число разрядов влево или вправо;

- преобразование числа из последовательной формы в параллельную либо наоборот (преобразование из параллельной формы представления числа в последовательную);

- получения инверсного кода числа.

Параметры регистров:

- Разрядность – определяется количеством триггеров в регистре;

- Быстродействие - определяется максимальной тактовой частотой приема (записи), передачи (чтения) и сдвига информации.

2.3.2 Классификация регистров

Основные признаки классификации регистров: