ВУЗ: Томский государственный университет систем управления и радиоэлектроники

Категория: Учебное пособие

Дисциплина: Электроника

Добавлен: 23.10.2018

Просмотров: 5624

Скачиваний: 22

21

Напряжение в точке А равно падению напряжения на эмит-

терном переходе

A

U , смещенном в прямом направлении. Из

вольт-амперных характеристик (рис. 8.9, б) видно, что этого на-

пряжения недостаточно, чтобы последовательно включенные

коллекторный переход многоэмиттерного транзистора и эмит-

терный переход второго транзистора были смещены в прямом

направлении. Следовательно, токи базы и коллектора второго

транзистора практически равны нулю и напряжение на выходе

равно логической единице (

K

E ).

На основании эквивалентной схемы (рис. 8.9) можно запи-

сать напряжение в точке А

1

0

1

0

0

0

ln

ln

K

K

А

Т

T

I

I

I

I

U

I

I

+

+

= ϕ

+ ϕ

;

(8.8

а

)

1

0

0

2

ln

Э

А

Т

I

I

U

I

+

= ϕ

, (8.8

б

)

где

1

Э

I

—

суммарный

ток

через

эмиттерные

переходы

много

-

эмиттерного

транзистора

,

1

K

I

—

ток

коллекторного

перехода

первого

транзистора

,

0

I —

обратный

ток

переходов

.

Приравни

-

вая

правые

части

выражений

(8.8

а

)

и

(8.8

б

),

после

несложных

преобразований

получим

:

(

)

1

0

0

1

0

2

2

Э

K

I

I

I

I

I

+

=

− , (8.9)

учитывая

,

что

1

0

Э

I

I

>> (8.9),

окончательно

запишем

1 0

1

0

2

Э

K

I I

I

I

≈

− . (8.10)

Из

(8.10)

получим

1

1

Э

K

I

I

>>

,

т

.

е

.

коллекторный

переход

первого

транзистора

,

а

также

коллекторный

и

эмиттерный

пере

-

ходы

второго

транзистора

закрыты

.

Напряжение

на

выходе

логи

-

ческого

элемента

равно

единице

(

K

E ).

На

рис

. 8.10

приведена

эквивалентная

схема

логического

эле

-

мента

для

случая

,

когда

на

обоих

эмиттерах

первого

транзистора

логические

единицы

(

K

E ).

Эмиттерные

переходы

первого

транзи

-

стора

закрыты

,

а

коллекторный

переход

смещается

в

прямом

на

-

правлении

.

Эмиттерный

переход

второго

транзистора

смещается

в

22

прямом

направлении

,

и

транзистор

входит

в

режим

насыщения

.

Напряжение

на

выходе

логического

элемента

равно

нулю

.

Э

3

Э

2

R

К

U

ВЫХ

R

Б

E

K

I

Б

β

Э

1

К

1

I

RБ

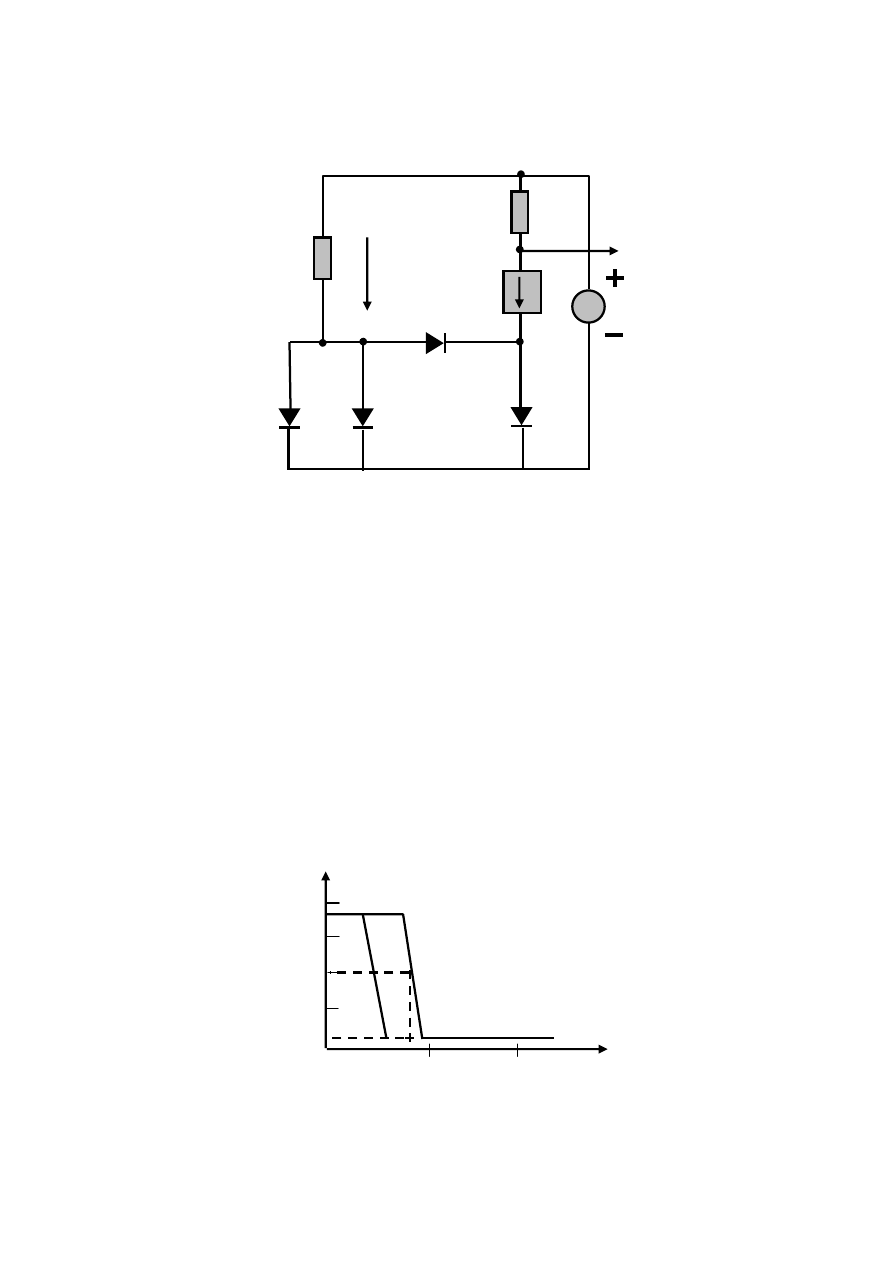

Рис. 8.10 — Эквивалентная схема логического

элемента для момента времени, когда на входах

действуют сигналы равные логическим единицам

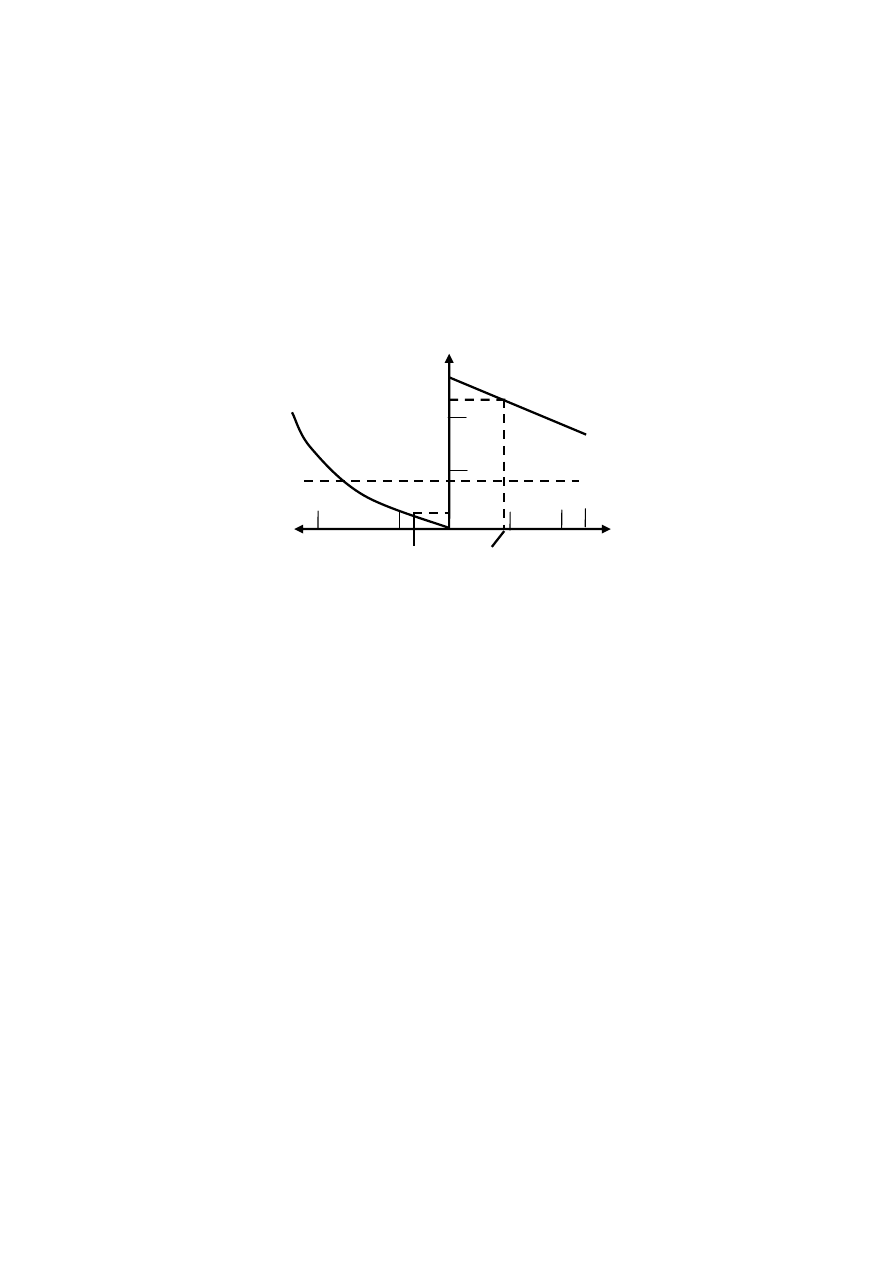

Передаточная

характеристика

рассматриваемого

элемента

ТТЛ

при

U

ип

=3

В

,

Т

=20°

С

и

n=1

приведена

на

рис

. 8.11.

При

сня

-

тии

этой

характеристики

для

ЛЭ

,

имеющего

m

входов

,

входное

напряжение

изменяют

только

на

одном

из

входов

в

диапазоне

от

0

до

U

ип

,

а

на

остальные

входы

подают

напряжение

1

U .

При

по

-

вышении

температуры

U

пор

понижается

(

температурный

коэффи

-

циент

около

— 2

мВ

/°

С

),

что

приводит

к

уменьшению

0

П

U

и

уве

-

личению

1

П

U .

Соответствующая

характеристика

для

Т

= 120 °

С

показана

на

рис

. 8.11.

1

0

U

0

2

U

1

U

ПОР

U

ВЫХ

U

ВХ

2

Рис. 8.11 — Передаточная характеристика

ТТЛ элемента

23

Нагрузочная

способность

ЛЭ

прежде

всего

ограничена

тем

,

что

с

ростом

числа

нагрузок

увеличиваются

выходные

токи

.

Вы

-

ходные

характеристики

элемента

ТТЛ

при

U

ип

=3

В

, R

2

=1,2

кОм

,

β =

60

и

Т

— 20 °

С

приведены

на

рис

. 8.12.

Видно

,

что

увеличение

выходных

токов

приводит

к

понижению

уровня

1

U

и

повышению

уровня

0

U .

I

0

ВЫХ

I

1

ВЫХ

U

0

А

U

1

вых макс

U

ВЫХ

I

0

вых макс

I

1

вых макс

U

1

ВЫХ

U

ПОР

20

0,8

Рис. 8.12 — Выходные характеристики

элемента ТТЛ

Средняя

потребляемая

мощность

может

быть

оценена

по

формуле

:

0

1

1

1

1

2

0,5

(

)

СР

ИП

Б

Б

K

P

U

I

I

I

=

+

+

. (8.11)

Поскольку

при

снижении

напряжения

питания

уменьшают

-

ся

помехоустойчивость

и

нагрузочная

способность

,

оно

ограни

-

чивается

значением

.

2

ИП МИН

U

> В. Поэтому потребляемую

мощность можно уменьшить, только увеличив сопротивления

R

1

и

R

2

. Однако при этом возрастает средняя задержка. Средняя за-

держка определяется временем перезарядки паразитных емко-

стей. Кроме того, средняя задержка зависит от времени рассасы-

вания избыточного заряда в выходном транзисторе.

Для повышения помехоустойчивости, нагрузочной способно-

сти и обеспечения высокого быстродействия при значительно

большей емкости нагрузки в элементах ТТЛ используют сложный

инвертор. Такие элементы применяют в микросхемах малой и

средней степеней интеграции, а также в выходных каскадах БИС.

24

VT5

VT4

VT3

B

A

U

ИП

R

1

R

2

R

3

R

4

VT1

VT2

C=AB

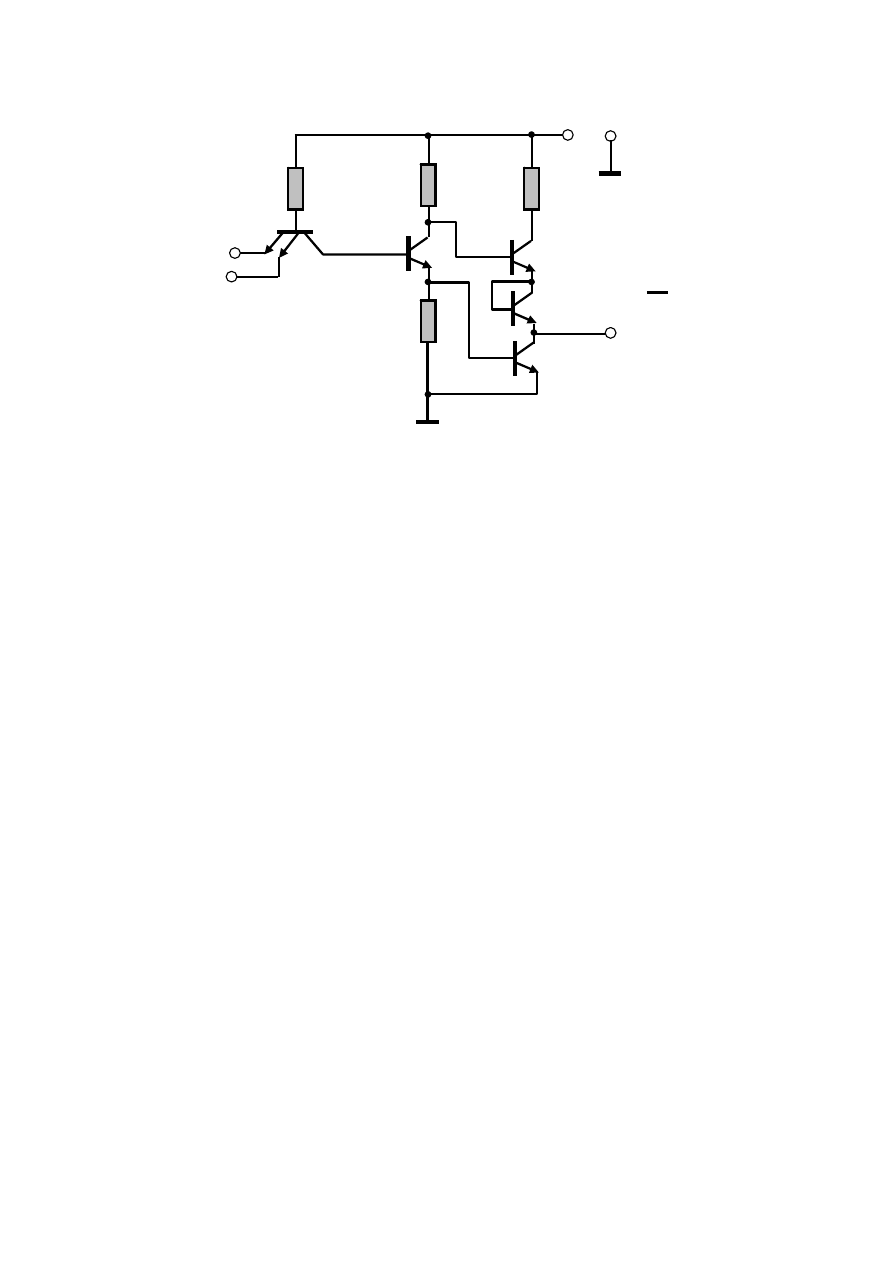

Рис. 8.13 — Схема элемента ТТЛ со сложным

инвертором

Схема элемента ТТЛ со сложным инвертором представлена

на рис. 8.13. Этот элемент выполняет логическую функцию

И

-

НЕ. Назначение входного транзистора и резистора

R1

то же,

что и в простейшем элементе. Остальные транзисторы и резисто-

ры составляют сложный инвертор, содержащий промежуточный

каскад на транзисторе VТ2 и резисторах R2, R3 и выходной кас-

кад на транзисторах VТЗ — VТ5 и резисторе

R4.

Транзистор VТ5

используется в диодном включении (

0

КБ

U

= ). С выходов проме-

жуточного каскада (с коллектора и эмиттера VТ2) задаются

управляющие сигналы, обеспечивающие противофазное пере-

ключение транзисторов VТЗ и VТ4 выходного каскада: если один

из них включен, то другой выключен. При

0

ВХ

U

U

=

на одном

или нескольких входах, как и в простейшем элементе ТТЛ, кол-

лекторный ток входного транзистора и напряжение на базе тран-

зистора VТ2 близки к нулю. Поэтому транзисторы VТ2 и VТЗ за-

крыты. Транзистор VТ4 открыт, так как в его базу втекает ток,

задаваемый резистором R2. Напряжение на выходе соответствует

напряжению высокого уровня. Пренебрегая малым падением на-

пряжения на этом резисторе, выходное напряжение можно оце-

нить по формуле:

1

1

2

,

ИП

БЭ

U

U

U

=

−

(8.12)

где

1

2

БЭ

U

— падение напряжения на эмиттерных переходах тран-

25

зисторов VТ4 и VТ5. Через эти переходы протекает выходной ток

элемента ТТЛ, являющийся входным током нагрузочных элемен-

тов. В зависимости от значения выходного тока

1

БЭ

U

может при-

нимать значения 0,45...0,5 В при Т = 25 °С. Для обеспечения

большей помехоустойчивости для ЛЭ со сложным инвертором

необходимо более высокое напряжение питания. Типовое напря-

жение питания 5 В. При этом для

1

БЭ

U

=0,5 В из (10.12) получаем

1

U

=4 В. Нагрузочная способность по сравнению с нагрузочной

способностью простейшего элемента ТТЛ увеличивается за счет

использования транзистора VТ4. В этом состоянии VТ4 работает

в активном режиме. Выходная характеристика элемента ТТЛ со

сложным инвертором аналогична по форме зависимости для про-

стой логической схемы. При напряжении

1

U

на всех входах мно-

гоэмиттерного транзистора транзистор VТ2 открывается коллек-

торным током входного транзистора и переходит в режим насы-

щения. Напряжение на его коллекторе понижается, и транзистор

VТ4 закрывается. Транзистор VТЗ открывается эмиттерным то-

ком транзистора VТ2 и также переходит в режим насыщения по-

сле разряда паразитной ёмкости С

Н

.

При этом выходное напряжение соответствует напряжению

низкого уровня и определяется напряжением насыщения транзи-

стора VТЗ. Для того чтобы транзистор VТ4 не открывался при

понижении выходного напряжения, в схему введен транзистор

VТ5. Сопротивления

R1

и

R2

выбирают из условия

R1>R2

, по-

этому эмиттерный ток транзистора VТ2 в режиме насыщения

значительно больше тока базы. Следовательно, в промежуточном

каскаде происходит усиление тока. В результате в базу транзи-

стора VТЗ поступает больший ток, чем в простейшем элементе

при том же сопротивлении R1, что увеличивает нагрузочную

способность в состоянии

0

ВЫХ

U

U

=

.

Форма выходной характеристики ЛЭ со сложным инверто-

ром в этом состоянии такая же, как и характеристики простого

элемента. Однако значения токов

I

ВЫХ

значительно больше. Рези-

стор

R3

необходим для создания цепи, по которой протекает ба-

зовый ток транзистора VТЗ во время процесса рассасывания. Ре-

зистор

R4

с малым сопротивлением (около 100 Ом) служит для