Добавлен: 29.10.2018

Просмотров: 48133

Скачиваний: 190

386

Глава 5. Ввод и вывод информации

В-третьих, при вводе-выводе, отображаемом на пространство памяти, любая команда,

которая может обращаться к памяти, может также обращаться и к регистрам управ-

ления. Например, если есть команда TEST, проверяющая значение слова памяти на

равенство нулю, она может быть применена также для проверки на равенство нулю

значения в регистре управления, что может быть сигналом незанятости устройства

и возможности приема им новой команды. При этом код на ассемблере может иметь

следующий вид:

LOOP: TEST PORT_4 // проверка того, содержит ли порт 4 значение 0

BEQ READY // если он содержит 0, переход к метке ready

BRANCH LOOP // если нет, продолжение проверки

READY:

При отсутствии отображения регистров ввода-вывода на пространство памяти регистр

управления сначала должен быть считан в центральный процессор, а затем проверен,

для чего потребуются две команды вместо одной. В случае использования показанного

ранее цикла нужно будет добавить еще четыре команды, что слегка замедлит отклик

устройства, проверяемого на незанятость.

При конструировании компьютеров практически всегда приходится идти на компро-

миссы, и данный случай не исключение. У ввода-вывода, отображаемого на простран-

ство памяти, есть и свои недостатки. Во-первых, большинство современных компьюте-

ров используют ту или иную разновидность кэширования слов памяти. Кэширование

регистров управления устройством может привести к пагубным последствиям. По-

смотрим, что получится с циклом в представленном ранее ассемблерном коде при

использовании кэширования. Первое обращение к PORT_4 приведет к тому, что это

слово попадет в кэш. При последующих обращениях значение будет браться прямо

из кэша без запроса самого устройства. А когда устройство наконец-то освободится,

программа просто не сможет это определить и цикл продолжится до бесконечности.

Чтобы предотвратить подобную ситуацию при использовании ввода-вывода, отобра-

жаемого на пространство памяти, аппаратура должна иметь возможность выборочного

отключения кэширования, например на постраничной основе. Это свойство приводит

к дополнительному усложнению как аппаратного обеспечения, так и операционной

системы, которым приходится управлять избирательным кэшированием.

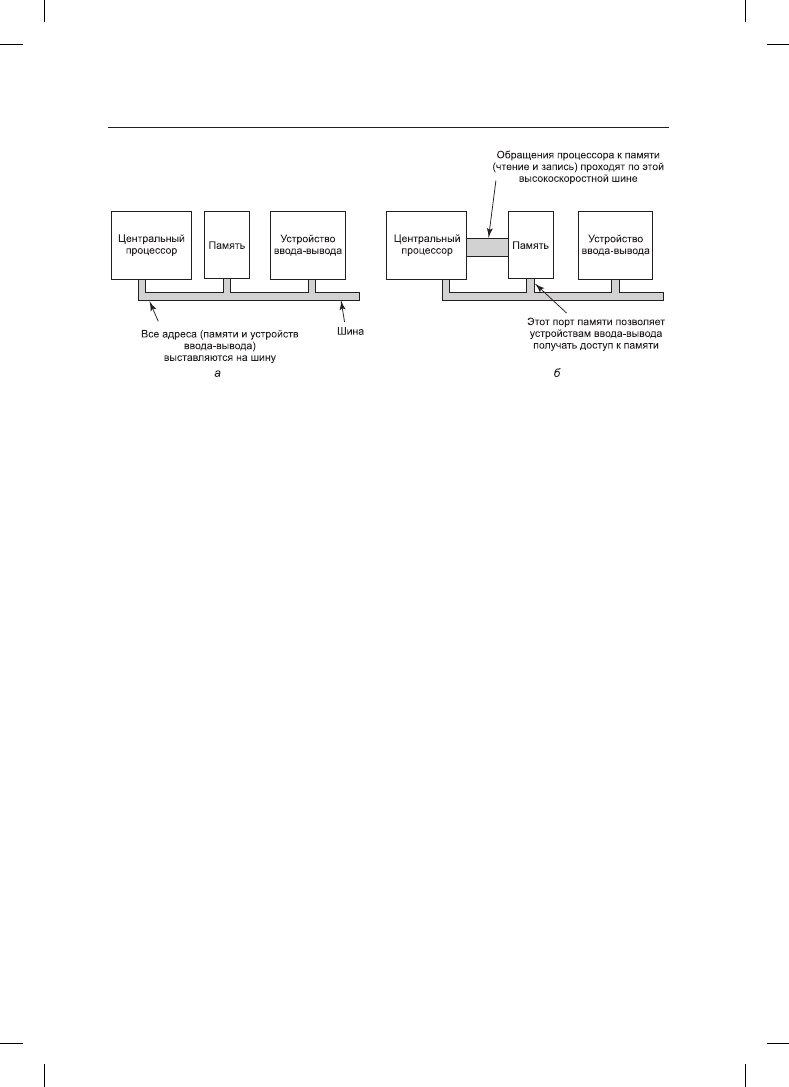

Во-вторых, если используется только одно адресное пространство, то все модули

памяти и все устройства ввода-вывода должны проверять все обращения к памяти,

чтобы понять, кому из них следует отвечать. Если у компьютера, как показано на

рис. 5.2, а, используется одна общая шина, то заставить всех рассматривать каждый

адрес несложно.

Но в современных персональных компьютерах наблюдается тенденция использования

выделенной высокоскоростной шины памяти (рис. 5.2, б). Эта шина специально при-

способлена для оптимизации производительности памяти, чтобы не идти на компро-

мисс ради медлительных устройств ввода-вывода. У машин семейства x86 могут быть

несколько шин (шины памяти, шины PCIe, SCSI и USB), показанных на рис. 1.12.

Проблема, возникающая при использовании отдельной шины памяти на машинах

с отображением регистров ввода-вывода на память, состоит в том, что устройства вво-

да-вывода не могут увидеть адреса памяти, выставляемые процессором на эту шину,

следовательно, они не могут реагировать на эти адреса. Поэтому, чтобы заставить

отображаемый на память ввод-вывод работать на системе с несколькими шинами,

5.1. Основы аппаратного обеспечения ввода-вывода

387

Рис. 5.2. Архитектура: а — использующая одну шину; б — с двойной шиной памяти

нужно предпринять какие-то специальные меры. Одним из возможных вариантов

является первоначальное направление всех обращений к пространству памяти по

высокоскоростной шине напрямую к модулям памяти. Если эти модули не смогут от-

ветить, центральный процессор попробует воспользоваться другими шинами. Такая

конструкция вполне жизнеспособна, но требует дополнительного усложнения аппа-

ратного обеспечения.

Второе возможное решение предусматривает установку на шину памяти специального

отслеживающего устройства, передающего все адреса потенциально заинтересованным

устройствам ввода-вывода. При этом возникает проблема, связанная с неспособностью

устройств ввода-вывода обрабатывать запросы так же быстро, как это делают модули

памяти.

Третий вариант, который как раз и используется в приведенной на рис. 1.12 конфигу-

рации компьютера, основан на фильтрации адресов в контроллере памяти. В данном

случае микросхема контроллера памяти содержит регистры диапазона, заполняемые

в процессе загрузки системы. К примеру, диапазон от 640 К до 1 M – 1 может быть по-

мечен как не принадлежащий пространству оперативной памяти и содержащий адреса,

ведущие не к памяти, а к устройствам. Недостаток этой схемы состоит в необходимости

обозначить в процессе загрузки системы те адреса, которые в действительности не бу-

дут относиться к памяти. Получается, что у каждой схемы есть аргументы за и против

ее использования, поэтому без компромиссов не обойтись.

5.1.4. Прямой доступ к памяти

Независимо от наличия или отсутствия у центрального процессора ввода-вывода,

отображаемого на пространство памяти, ему необходимо обращаться к контролле-

рам устройств, чтобы осуществлять с ними обмен данными. Центральный процессор

может запрашивать данные у контроллера ввода-вывода побайтно, но при этом будет

нерационально расходоваться его рабочее время, поэтому чаще всего используется

другая схема, которая называется прямым доступом к памяти (Direct Memory Access

(DMA)). Чтобы не усложнять объяснение, предполагается, что центральный процессор

обращается ко всем устройствам и к памяти посредством единой системной шины, со-

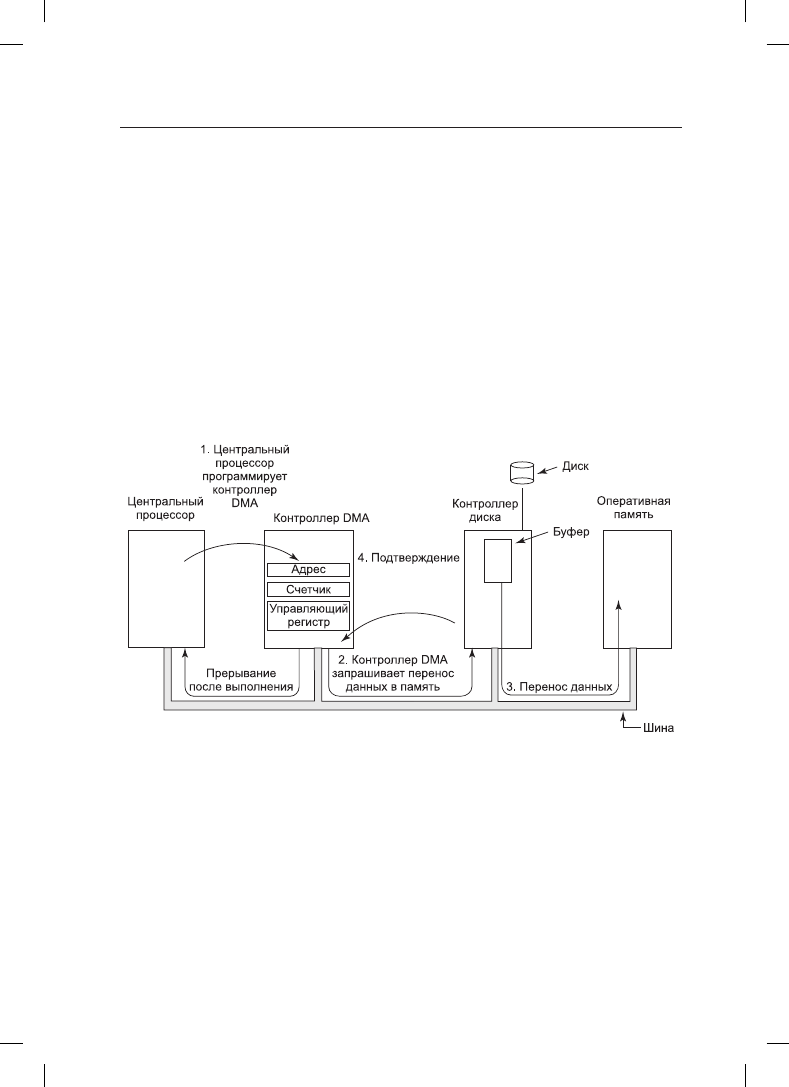

единяющей центральный процессор, память и устройства ввода-вывода (рис. 5.3). Нам

388

Глава 5. Ввод и вывод информации

уже известно, что реальная организация в современных системах намного сложнее, но

все принципы одинаковы. Операционная система может использовать DMA только

при наличии аппаратного DMA-контроллера, присутствующего у большинства систем.

Иногда этот контроллер встроен в контроллеры дисков и другие контроллеры, но такая

конструкция требует отдельного DMA-контроллера для каждого устройства. Чаще

всего для упорядочения обмена данными с несколькими устройствами, проводимого

нередко в параллельном режиме, доступен только один DMA-контроллер (размещен-

ный, к примеру, на системной плате).

На рис. 5.3 показано, что где бы DMA-контроллер ни находился физически, он имеет

доступ к системной шине независимо от центрального процессора. В нем имеется не-

сколько регистров, доступных центральному процессору для чтения и записи. В их

число входят регистр адреса памяти, регистр счетчика байтов и один или несколько

регистров управления. В регистрах управления указываются используемый порт ввода-

вывода, направление передачи данных (чтение из устройства ввода-вывода или запись

в него), единица передаваемой информации (побайтовая или пословная передача),

а также количество байтов, передаваемых в одном пакете.

Рис. 5.3. Операции, осуществляемые при передаче данных с использованием DMA

Чтобы объяснить принцип работы DMA, рассмотрим сначала, как осуществляется

чтение диска, когда DMA не используется. Сначала контроллер диска последователь-

но побитно считывает блок (один или несколько секторов) с диска, пока весь блок не

окажется во внутреннем буфере контроллера. Затем он вычисляет контрольную сумму,

чтобы убедиться в отсутствии ошибок чтения. Затем контроллер инициирует преры-

вание. Когда операционная система приступает к работе, она может в цикле побайтно

или пословно считать дисковый блок из буфера контроллера, считывая при каждом

проходе цикла один байт или слово из регистра контроллера устройства и сохраняя

его в оперативной памяти.

При использовании DMA все происходит по-другому. Сначала центральный процессор

программирует DMA-контроллер, устанавливая значения его регистров таким образом,

5.1. Основы аппаратного обеспечения ввода-вывода

389

чтобы он знал, что и куда нужно передать (шаг 1 на рис. 5.3). Он также выдает команду

контроллеру диска на чтение данных с диска во внутренний буфер контроллера и на

проверку контрольной суммы. После того как в буфере контроллера окажутся досто-

верные данные, к работе может приступать DMA.

DMA-контроллер инициирует передачу данных, выдавая по шине контроллеру дис-

ка запрос на чтение (шаг 2). Этот запрос на чтение выглядит так же, как и любой

другой запрос на чтение, и контроллер диска не знает и даже не интересуется, откуда

он пришел — от центрального процессора или от DMA-контроллера. Обычно адрес

памяти, куда нужно вести запись, выставлен на адресных линиях шины, поэтому,

когда контроллер диска извлекает очередное слово из своего внутреннего буфера, он

знает, куда его следует записать. Запись в память — это еще один стандартный цикл

шины (шаг 3). Когда запись завершается, контроллер диска также по шине посылает

подтверждающий сигнал DMA-контроллеру (шаг 4). Затем DMA-контроллер дает

приращение используемому адресу памяти и уменьшает значение счетчика байтов.

Если счетчик байтов все еще больше нуля, то шаги со 2-го по 4-й повторяются до тех

пор, пока значение счетчика не станет равно нулю. Как только это произойдет, DMA-

контроллер выставляет прерывание, чтобы центральный процессор узнал о завершении

передачи данных. И когда к работе приступает операционная система, ей уже не нужно

копировать дисковый блок в память, потому что он уже там.

Контроллеры DMA существенно различаются по степени сложности. Самые простые

из них, как описано ранее, обслуживают одновременно только одну операцию передачи

данных. Более сложные контроллеры могут быть запрограммированы на одновремен-

ную обработку нескольких таких операций. У таких контроллеров есть несколько на-

боров внутренних регистров, по одному для каждого канала. Центральный процессор

начинает с того, что загружает каждый набор соответствующими параметрами для

передачи данных по определенному каналу. После показанной на рис. 5.3 передачи каж-

дого слова (шаги со 2-го по 4-й), DMA-контроллер решает, какое из устройств обслу-

живать следующим. Он может быть настроен на использование алгоритма кругового

обслуживания, или же у него может быть система приоритетов, дающая преимущество

одним устройствам над другими. Одновременно могут рассматриваться сразу несколь-

ко запросов к различным контроллерам устройств при условии, что есть однозначный

способ обособленной выдачи сигнала подтверждения. Поэтому довольно часто для

каждого DMA-канала на шине используется отдельная линия подтверждения.

Многие шины могут работать в двух режимах: пословном и поблочном. Некоторые

DMA-контроллеры могут также работать в обоих режимах. В первом режиме осу-

ществляются операции, описанные ранее: DMA-контроллер запрашивает передачу

одного слова и получает его. Если центральному процессору также нужна шина, то он

вынужден ждать. Такой механизм называется захватом цикла, поскольку контроллер

устройства ненадолго украдкой перехватывает у центрального процессора первый по-

павшийся цикл шины, слегка замедляя его работу. В блочном режиме DMA-контроллер

предписывает устройству занять шину, осуществить серию пересылок данных, а затем

освободить шину. Такой образ действий называется пакетным режимом. Он более

эффективен, чем захват цикла, поскольку, чтобы занять шину, требуется определенное

время, а тут это время затрачивается на передачу сразу нескольких слов только один

раз. Недостаток пакетного режима заключается в том, что если будет передаваться

довольно длинный пакет данных, то он может заблокировать центральный процессор

и другие устройства на весьма существенный период времени.

390

Глава 5. Ввод и вывод информации

Рассмотренную нами модель иногда называют сквозным режимом, так как DMA-

контроллер предписывает контроллеру устройства осуществить передачу данных

непосредственно в оперативную память. Альтернативный режим, который использу-

ется некоторыми DMA-контроллерами, предусматривает принуждение контроллера

устройства на передачу слова DMA-контроллеру, который затем выставляет на шине

дополнительный запрос на запись слова по месту его предназначения. Эта схема тре-

бует дополнительного цикла шины на каждое передаваемое слово, но она обладает

большей гибкостью, поскольку может копировать из устройства в устройство и даже

из одного места памяти в другое (выполняя сначала чтение из памяти, а затем запись

в память по другому адресу).

Большинство DMA-контроллеров используют для передачи данных физические

адреса памяти. Для этого операционная система должна преобразовать виртуальный

адрес намеченного буфера памяти в физический адрес и записать этот физический

адрес в адресный регистр контроллера DMA. В отдельных DMA-контроллерах вместо

этого используется альтернативная схема, при которой в контроллер записывается

виртуальный адрес. Затем для осуществления преобразования виртуального адреса

в физический DMA-контроллер должен воспользоваться блоком управления памя-

тью (MMU). Виртуальные адреса могут выставляться на шину только в том случае,

если MMU является частью памяти (что встречается довольно редко), а не частью

центрального процессора.

Как уже упоминалось, еще до начала работы DMA диск считывает данные в свой вну-

тренний буфер. Может вызвать удивление, почему контроллер, получив данные с дис-

ка, не сохраняет байты сразу в оперативной памяти. Иными словами, зачем ему нужен

внутренний буфер? На это есть две причины. Во-первых, осуществляя внутреннюю

буферизацию, контроллер диска может проверять контрольную сумму перед тем, как

приступать к передаче данных. Если контрольная сумма не сходится, выставляется

ошибка и данные не передаются.

Во-вторых, как только начинается передача данных с диска, биты поступают с диска

с постоянной скоростью независимо от того, готов контроллер их принимать или нет.

Если бы контроллер попытался записывать данные непосредственно в память, то для

передачи каждого слова ему пришлось бы обращаться к системной шине. Если бы шина

была занята обслуживанием какого-нибудь другого устройства (например, при пакет-

ном режиме работы), то контроллеру пришлось бы ждать. Если бы следующее слово,

прочитанное с диска, поступило еще до того, как было сохранено предыдущее слово,

контроллер вынужден был бы где-нибудь его сохранить. Если бы шина была слишком

занята, то контроллеру пришлось бы заняться хранением довольно большого количе-

ства слов и решать массу административных задач. А когда осуществляется внутренняя

буферизация блока, надобности в использовании шины не возникает вплоть до начала

работы DMA, поэтому конструкция контроллера может быть упрощена, поскольку

передача данных в память с помощью DMA не критична по времени. (Некоторые более

старые контроллеры действительно имели непосредственное обращение к памяти, рас-

полагая совсем небольшой по объему внутренней буферизацией, но когда шина была

слишком занята, передача должна была прерываться из-за ошибки переполнения.)

DMA используется не во всех компьютерах. Аргументом против его использования

является то, что центральный процессор зачастую намного быстрее DMA-контроллера

и может выполнять эту работу намного быстрее (когда ограничивающим фактором

не является скорость работы устройства ввода-вывода). Если для него нет никакой