Файл: Практическая работа 13 исследование триггеров, регистров, счетчиков цель работы ознакомление с принципом.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 06.11.2023

Просмотров: 107

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

По таблице 4 может быть получено следующее уравнение асинхронного Т-триггера:

Как видно из таблицы 4 и уравнения триггера, при Т=1 асинхронный Т-триггер меняет свое состояние на противоположное, а при Т=0 состояние триггера не изменяется.

Так как Т-триггер суммирует (или подсчитывает) по модулю два количество единиц, поступающих на его информационный вход, то Т-триггер называют также триггером со счетным входом.

Логика работы синхронного Т-триггера описывается таблицей переходов, которая имеет вид таблицы 5.

Таблица 5

Из таблицы 5 видно, что при С=0 триггер не изменяет своего состояния, а при С=1 работает как асинхронный Т-триггер.

Функциональная схема Т-триггера может быть построена на основе синхронного RS-триггера (однотактного или двухтактного).

Схема асинхронного Т-триггера приведена на рисунке 10, а синхронного Т-триггера - на рисунке 11. Обе схемы построены на основе синхронного двухтактного RS-триггера. Аналогичные схемы можно строить на основе однотактного RS-триггера. В двухтактных асинхронных Т-триггерах выходной сигнал формируется по заднему фронту входного сигнала Т, а в однотактных - по переднему фронту. В двухтактных синхронных Т-триггерах выходной сигнал формируется по заднему фронту сигнала С.

Схему асинхронного Т-триггера, в свою очередь, можно получить из D-триггера простой коммутацией входов и выходов (см. рисунок 12).

Схему асинхронного Т-триггера, в свою очередь, можно получить из D-триггера простой коммутацией входов и выходов (см. рисунок 12).

JK-триггер

JK-триггер называется также универсальным триггером. Универсальность схемы JK-триггера состоит в том, что простой коммутацией входов и выходов можно получать схемы других типов триггеров.

JK-триггер имеет два информационных входа. Вход J используется для установки триггера в состояние 1, а вход К -для установки в состояние 0, т.е. входы J и К аналогичны входам R и S RS-триггера.

Отличие заключается в том, что на входы J и К могут одновременно поступать сигналы 1. В этом случае JК- триггер изменяет свое состояние на противоположное.

Таблица переходов JK-триггера при С=1 имеет вид таблицы 6.

И з таблицы 6 можно получить следующее уравнение JK-триггера:

з таблицы 6 можно получить следующее уравнение JK-триггера:

Следовательно, при J=1, K=0 всегда Qt+1=1, а при J=0, K=1 всегда Qt+1=0, т.е. JK-триггер работает как RS-триггер, если рассматривать входы J и K как входы S и R.

В свою очередь, при J=1, K=1 _Qt+1=Qt, т.е. триггер переходит в противоположное состояние (работает как Т-триггер).

Функциональная схема двухтактного JK-триггера и УГО триггера показаны на рисунке 13. Примеры получения других типов триггеров на основе JK-триггера представлены на рисунок 14.

JK-триггер, кроме основных информационных входов и входа синхронизации, может иметь также дополнительные информационные входы, например, дополнительные инверсные асинхронные входы R и S, которые используются для установки триггера в 0 или 1 независимо от значения сигнала на входе синхронизации. Кроме того, триггер может иметь несколько входов J или K, объединенных по схеме И.

Регистры.

Наиболее распространенным узлом цифровой техники и устройств автоматики являются регистры. Регистры строятся на базе синхронных одно- и двухступенчатых RS и D-триггеров. Регистры могут быть реализованы также на базе JK-триггеров.

Регистры с параллельным приемом и выдачей информации служат для хранения информации и называются регистрами памяти или хранения. Запись новой информации в регистр осуществляется после установки на входах D0 ... Dm новой цифровой комбинации при поступлении синхроимпульса С. Количество разрядов записываемой цифровой информации определяется разрядностью регистра, которая, в свою очередь, определяется количеством триггеров, образующих этот регистр. Регистры памяти могут быть реализованы на D-триггерах, если информация поступает на входы регистра в виде однофазных сигналов и на RS-триггерах, если информация поступает в виде парафазных сигналов. В некоторых случаях регистры могут иметь вход для установки выходов в состояние “0”. Этот асинхронный вход называют входом R “сброса” триггеров регистра. На рис. 15 приведены схемы четырехразрядных регистров памяти на D- и RS-триггерах, синхронизируемых уровнем и фронтом синхроимпульсов (обычно четыре триггера объединены в одном корпусе ИМС). На рисунке 15 показаны регистры хранения на D-триггерах, синхронизируемых фронтом (а) и на RS-триггерах, синхронизируемых фронтом (б). На рисунке 15, в показано УГО регистра.

а б в

Рисунок 15

Регистры с последовательным приемом или выдачей информации называются сдвиговыми регистрами или регистрами сдвига. Они могут выполнять функции хранения и преобразования информации (умножение и деление чисел двоичной системы счисления, преобразование параллельного кода в последовательный и наоборот и т.д.).

На рисунке 16, а и 16,б приведены схемы четырехразрядных регистров сдвига, реализованных на D- и RS-триггерах, а временные диаграммы, поясняющие работу регистра сдвига, приведены на рисунке 17.

Рисунок 16

Рисунок 17

Порядок выполнения работы

Задание 1. Построить на элементах 2И-НЕ и 2ИЛИ-НЕ схемы асинхронных RS-

триггеров (см. рисунок 3) и исследовать логику их работы в статическом режиме. Для этого собрать схемы с использованием пробников и переключателей.

Путем моделирования работы триггеров получить таблицы переходов и сравнить их с таблицей 1. Образцы схем для моделирования приведены на рисунке 18. Исследуемые схемы и таблицы занести в отчет.

Задание 2. Построить на элементах 2И-НЕ и 2-2И-2ИЛИ-НЕ схемы синхронных RS- триггеров (см. рисунок 4) и исследовать логику их работы в статическом режиме. Образцы схем для моделирования приведены на рисунке 19 и 20. В качестве элементов 2-2И-2ИЛИ-НЕ использована микросхема 7455, в которой располагается элемент 4-4И-2ИЛИ-НЕ. Исследуемые схемы и таблицы занести в отчет.

Задание 3. Исследовать в статическом режиме логику работы RS-триггера, который имеется в библиотеке программы. Для этого собрать схему, показанную на рисунке 21. Получить таблицу переходов триггера и сравнить ее с таблицей 1. Исследуемую схему и таблицу занести в отчет.

Задание 4. Исследовать в статическом режиме логику работы двухтактного RS-триггера. Для этого собрать схему, показанную на рисунке 22. Получить таблицу переходов триггера и сравнить ее с таблицей 1.

Исследуемую схему и таблицу занести в отчет.

З адание 5. Исследовать в статическом режиме логику работы асинхронного D-триггера. Для этого собрать схему, показанную на рисунке 23. Получить таблицу переходов триггера и сравнить ее с таблицей 3. Исследуемую схему и таблицу занести в отчет.

адание 5. Исследовать в статическом режиме логику работы асинхронного D-триггера. Для этого собрать схему, показанную на рисунке 23. Получить таблицу переходов триггера и сравнить ее с таблицей 3. Исследуемую схему и таблицу занести в отчет.

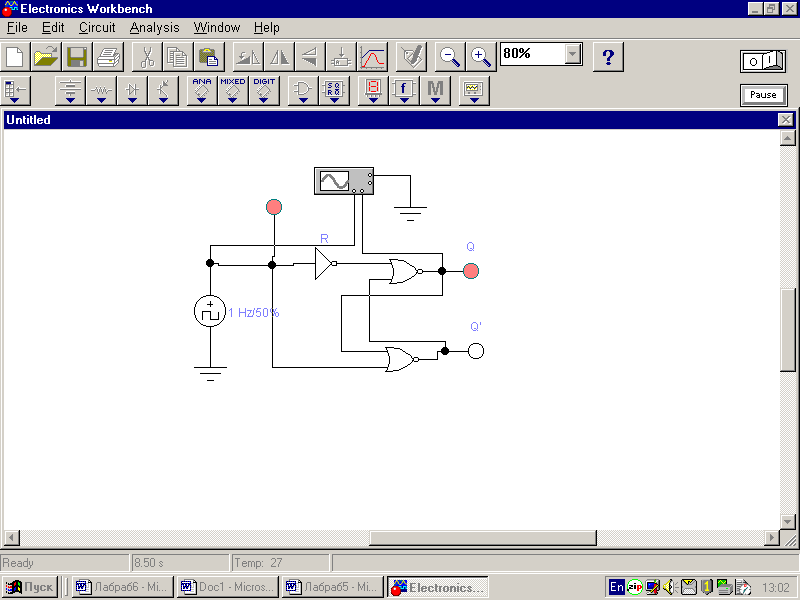

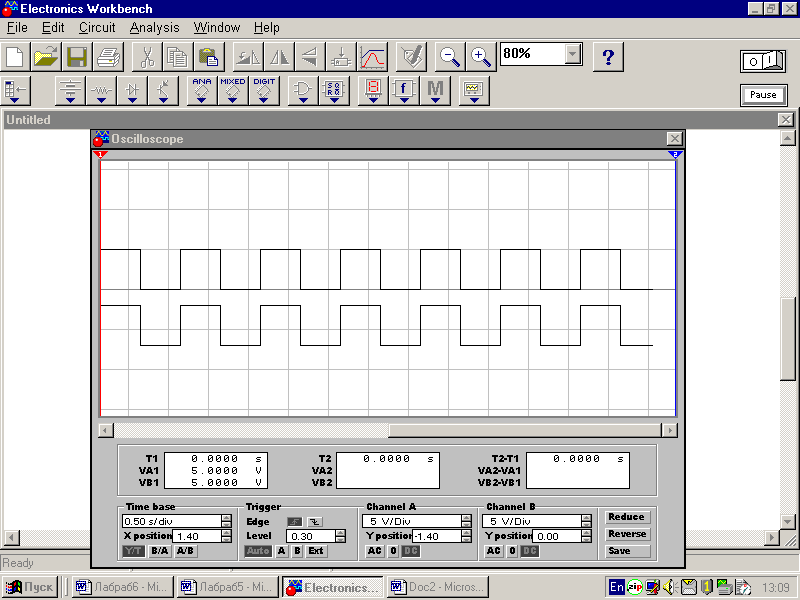

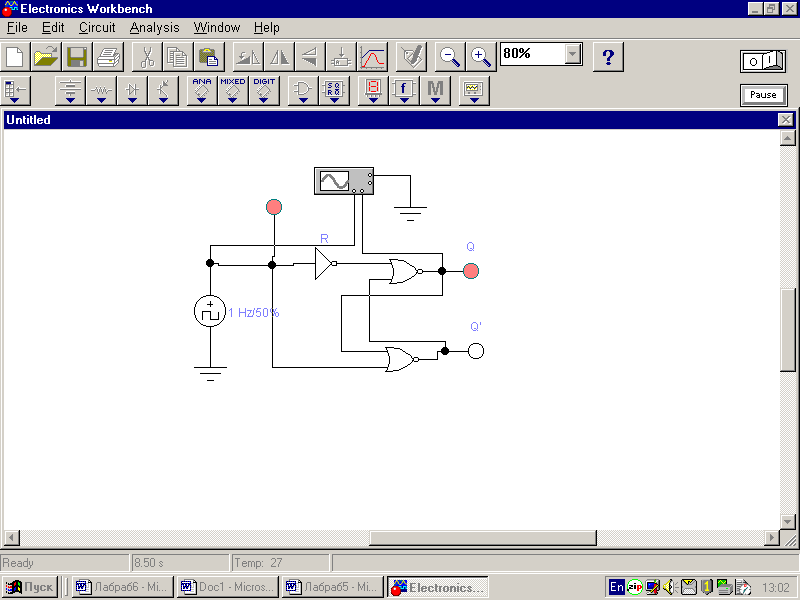

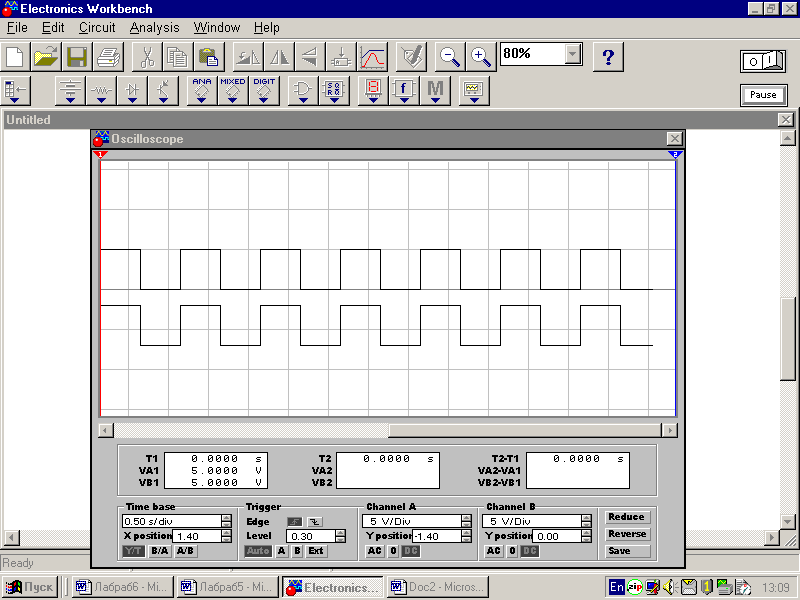

Задание 6. Исследовать в динамическом режиме логику работы асинхронного D-триггера. Для этого собрать схему, показанную на рисунке 24. Для визуального наблюдения работы схемы установить частоту генератора 1 Гц. Зарисовать полученную осциллограмму. Исследуемую схему и таблицу занести в отчет.

Задание 7. Собрать и исследовать в статическом режиме схему синхронного D- триггера на элементе 2И-2И-2ИЛИ-НЕ, в качестве которого использовать микросхему 7451 с 2-мя элементами 2И-2И-2ИЛИ-НЕ. Схема для исследования показана на рисунке 25. Результаты исследования занести в отчет.

Задание 8. Собрать и исследовать микросхему 7474, состоящую из 2-х синхронных D-триггеров. Схема показана на рисунке 26. Результаты исследования занести в отчет.

Задание 9. Собрать схему и исследовать работу асинхронного Т-триггера, построенного на базе синхронного D-триггера в статическом режиме. Соответствующая схема показана на рисунке 27. В качестве синхронного D-триггера использовать микросхему 7474 с дополнительными асинхронными входами установки и сброса (инверсные входы R и S). Результаты исследования занести в отчет.

Рисунок 24

Задание 10. Исследовать работу синхронного JK-триггера в динамическом режиме. Для этого собрать схему, показанную на рисунке 28. При подаче на входы J и K сигналов высокого уровня, а на вход синхронизации импульсов от генератора, триггер будет работать в режиме

переключения с частотой в два раза ниже, чем частота генератора. Для визуальной индикации подключить осциллограф к выходам генератора и триггера.

З адание 11. Собрать схему и исследовать работу синхронного JK-триггера в статическом режиме. Соответствующая схема показана на рисунке 29. В качестве синхронного JK-триггера использовать микросхему 74112. Результаты исследования занести в отчет.

адание 11. Собрать схему и исследовать работу синхронного JK-триггера в статическом режиме. Соответствующая схема показана на рисунке 29. В качестве синхронного JK-триггера использовать микросхему 74112. Результаты исследования занести в отчет.

Задание 12*.

1) Разработать и начертить схему электрическую функциональную четырехразрядного параллельного регистра на базе D-триггеров синхронизируемых фронтом для четных вариантов или на базе RS-триггеров, синхронизируемых фронтом для нечетных вариантов.

2) Разработать и начертить схему электрическую функциональную четырехразрядного регистра сдвига на базе на RS-триггеров, синхронизируемых фронтом, для четных вариантов или на базе D-триггеров, синхронизируемых фронтом, для нечетных вариантов.

3) Смоделировать параллельный регистр, разработанный в п. 12.1, в среде Electronics Workbench. Поочередно подать на входы D0 ... D3 код, соответствующий четырем младшим разрядам двоичного числа, равного номеру вашего варианта, и код на единицу меньший с помощью соответствующих ключей. Подать синхроимпульс С с помощью генератора слов Word Generation, включив его в ручном режиме Step, и убедиться в правильной работе параллельного регистра по состоянию логических пробников на его выходах.

4) Смоделировать регистр сдвига, разработанный в п. 12.2, в среде Electronics Workbench. Для имитации работы схемы подключить ее синхровход к генератору слов Word Generation, включив его в циклическом режиме Sycle. Подать на входы D0 ... D3 регистра код, соответствующий четырем младшим разрядам двоичного числа, равного номеру вашего варианта плюс три. Получить временные диаграммы входных и выходных сигналов сдвигающего регистра на экране логического анализатора Logic Analizer.

Содержание отчета

В отчет о выполненной работе включить следующие материалы:

1. тему и цель работы;

2. результаты выполнения заданий: исследуемые схемы, полученные таблицы переходов, временные диаграммы;

3. анализ полученных результатов

Как видно из таблицы 4 и уравнения триггера, при Т=1 асинхронный Т-триггер меняет свое состояние на противоположное, а при Т=0 состояние триггера не изменяется.

Так как Т-триггер суммирует (или подсчитывает) по модулю два количество единиц, поступающих на его информационный вход, то Т-триггер называют также триггером со счетным входом.

Логика работы синхронного Т-триггера описывается таблицей переходов, которая имеет вид таблицы 5.

| Входы | Состояния | ||

| C | Т | Q(0) | Q(1) |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Из таблицы 5 видно, что при С=0 триггер не изменяет своего состояния, а при С=1 работает как асинхронный Т-триггер.

Функциональная схема Т-триггера может быть построена на основе синхронного RS-триггера (однотактного или двухтактного).

Схема асинхронного Т-триггера приведена на рисунке 10, а синхронного Т-триггера - на рисунке 11. Обе схемы построены на основе синхронного двухтактного RS-триггера. Аналогичные схемы можно строить на основе однотактного RS-триггера. В двухтактных асинхронных Т-триггерах выходной сигнал формируется по заднему фронту входного сигнала Т, а в однотактных - по переднему фронту. В двухтактных синхронных Т-триггерах выходной сигнал формируется по заднему фронту сигнала С.

Схему асинхронного Т-триггера, в свою очередь, можно получить из D-триггера простой коммутацией входов и выходов (см. рисунок 12).

Схему асинхронного Т-триггера, в свою очередь, можно получить из D-триггера простой коммутацией входов и выходов (см. рисунок 12).

JK-триггер

JK-триггер называется также универсальным триггером. Универсальность схемы JK-триггера состоит в том, что простой коммутацией входов и выходов можно получать схемы других типов триггеров.

JK-триггер имеет два информационных входа. Вход J используется для установки триггера в состояние 1, а вход К -для установки в состояние 0, т.е. входы J и К аналогичны входам R и S RS-триггера.

Отличие заключается в том, что на входы J и К могут одновременно поступать сигналы 1. В этом случае JК- триггер изменяет свое состояние на противоположное.

Таблица переходов JK-триггера при С=1 имеет вид таблицы 6.

Таблица 6

| Входы | Состояния | ||

| J | K | Q(0) | Q(1) |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

И

з таблицы 6 можно получить следующее уравнение JK-триггера:

з таблицы 6 можно получить следующее уравнение JK-триггера: Следовательно, при J=1, K=0 всегда Qt+1=1, а при J=0, K=1 всегда Qt+1=0, т.е. JK-триггер работает как RS-триггер, если рассматривать входы J и K как входы S и R.

В свою очередь, при J=1, K=1 _Qt+1=Qt, т.е. триггер переходит в противоположное состояние (работает как Т-триггер).

Функциональная схема двухтактного JK-триггера и УГО триггера показаны на рисунке 13. Примеры получения других типов триггеров на основе JK-триггера представлены на рисунок 14.

JK-триггер, кроме основных информационных входов и входа синхронизации, может иметь также дополнительные информационные входы, например, дополнительные инверсные асинхронные входы R и S, которые используются для установки триггера в 0 или 1 независимо от значения сигнала на входе синхронизации. Кроме того, триггер может иметь несколько входов J или K, объединенных по схеме И.

Регистры.

Наиболее распространенным узлом цифровой техники и устройств автоматики являются регистры. Регистры строятся на базе синхронных одно- и двухступенчатых RS и D-триггеров. Регистры могут быть реализованы также на базе JK-триггеров.

Регистры с параллельным приемом и выдачей информации служат для хранения информации и называются регистрами памяти или хранения. Запись новой информации в регистр осуществляется после установки на входах D0 ... Dm новой цифровой комбинации при поступлении синхроимпульса С. Количество разрядов записываемой цифровой информации определяется разрядностью регистра, которая, в свою очередь, определяется количеством триггеров, образующих этот регистр. Регистры памяти могут быть реализованы на D-триггерах, если информация поступает на входы регистра в виде однофазных сигналов и на RS-триггерах, если информация поступает в виде парафазных сигналов. В некоторых случаях регистры могут иметь вход для установки выходов в состояние “0”. Этот асинхронный вход называют входом R “сброса” триггеров регистра. На рис. 15 приведены схемы четырехразрядных регистров памяти на D- и RS-триггерах, синхронизируемых уровнем и фронтом синхроимпульсов (обычно четыре триггера объединены в одном корпусе ИМС). На рисунке 15 показаны регистры хранения на D-триггерах, синхронизируемых фронтом (а) и на RS-триггерах, синхронизируемых фронтом (б). На рисунке 15, в показано УГО регистра.

а б в

Рисунок 15

Регистры с последовательным приемом или выдачей информации называются сдвиговыми регистрами или регистрами сдвига. Они могут выполнять функции хранения и преобразования информации (умножение и деление чисел двоичной системы счисления, преобразование параллельного кода в последовательный и наоборот и т.д.).

На рисунке 16, а и 16,б приведены схемы четырехразрядных регистров сдвига, реализованных на D- и RS-триггерах, а временные диаграммы, поясняющие работу регистра сдвига, приведены на рисунке 17.

Рисунок 16

Рисунок 17

Порядок выполнения работы

Задание 1. Построить на элементах 2И-НЕ и 2ИЛИ-НЕ схемы асинхронных RS-

триггеров (см. рисунок 3) и исследовать логику их работы в статическом режиме. Для этого собрать схемы с использованием пробников и переключателей.

Путем моделирования работы триггеров получить таблицы переходов и сравнить их с таблицей 1. Образцы схем для моделирования приведены на рисунке 18. Исследуемые схемы и таблицы занести в отчет.

Задание 2. Построить на элементах 2И-НЕ и 2-2И-2ИЛИ-НЕ схемы синхронных RS- триггеров (см. рисунок 4) и исследовать логику их работы в статическом режиме. Образцы схем для моделирования приведены на рисунке 19 и 20. В качестве элементов 2-2И-2ИЛИ-НЕ использована микросхема 7455, в которой располагается элемент 4-4И-2ИЛИ-НЕ. Исследуемые схемы и таблицы занести в отчет.

Задание 3. Исследовать в статическом режиме логику работы RS-триггера, который имеется в библиотеке программы. Для этого собрать схему, показанную на рисунке 21. Получить таблицу переходов триггера и сравнить ее с таблицей 1. Исследуемую схему и таблицу занести в отчет.

Задание 4. Исследовать в статическом режиме логику работы двухтактного RS-триггера. Для этого собрать схему, показанную на рисунке 22. Получить таблицу переходов триггера и сравнить ее с таблицей 1.

Исследуемую схему и таблицу занести в отчет.

З

адание 5. Исследовать в статическом режиме логику работы асинхронного D-триггера. Для этого собрать схему, показанную на рисунке 23. Получить таблицу переходов триггера и сравнить ее с таблицей 3. Исследуемую схему и таблицу занести в отчет.

адание 5. Исследовать в статическом режиме логику работы асинхронного D-триггера. Для этого собрать схему, показанную на рисунке 23. Получить таблицу переходов триггера и сравнить ее с таблицей 3. Исследуемую схему и таблицу занести в отчет.

Задание 6. Исследовать в динамическом режиме логику работы асинхронного D-триггера. Для этого собрать схему, показанную на рисунке 24. Для визуального наблюдения работы схемы установить частоту генератора 1 Гц. Зарисовать полученную осциллограмму. Исследуемую схему и таблицу занести в отчет.

Задание 7. Собрать и исследовать в статическом режиме схему синхронного D- триггера на элементе 2И-2И-2ИЛИ-НЕ, в качестве которого использовать микросхему 7451 с 2-мя элементами 2И-2И-2ИЛИ-НЕ. Схема для исследования показана на рисунке 25. Результаты исследования занести в отчет.

Задание 8. Собрать и исследовать микросхему 7474, состоящую из 2-х синхронных D-триггеров. Схема показана на рисунке 26. Результаты исследования занести в отчет.

Задание 9. Собрать схему и исследовать работу асинхронного Т-триггера, построенного на базе синхронного D-триггера в статическом режиме. Соответствующая схема показана на рисунке 27. В качестве синхронного D-триггера использовать микросхему 7474 с дополнительными асинхронными входами установки и сброса (инверсные входы R и S). Результаты исследования занести в отчет.

Рисунок 24

Задание 10. Исследовать работу синхронного JK-триггера в динамическом режиме. Для этого собрать схему, показанную на рисунке 28. При подаче на входы J и K сигналов высокого уровня, а на вход синхронизации импульсов от генератора, триггер будет работать в режиме

переключения с частотой в два раза ниже, чем частота генератора. Для визуальной индикации подключить осциллограф к выходам генератора и триггера.

З

адание 11. Собрать схему и исследовать работу синхронного JK-триггера в статическом режиме. Соответствующая схема показана на рисунке 29. В качестве синхронного JK-триггера использовать микросхему 74112. Результаты исследования занести в отчет.

адание 11. Собрать схему и исследовать работу синхронного JK-триггера в статическом режиме. Соответствующая схема показана на рисунке 29. В качестве синхронного JK-триггера использовать микросхему 74112. Результаты исследования занести в отчет.Задание 12*.

1) Разработать и начертить схему электрическую функциональную четырехразрядного параллельного регистра на базе D-триггеров синхронизируемых фронтом для четных вариантов или на базе RS-триггеров, синхронизируемых фронтом для нечетных вариантов.

2) Разработать и начертить схему электрическую функциональную четырехразрядного регистра сдвига на базе на RS-триггеров, синхронизируемых фронтом, для четных вариантов или на базе D-триггеров, синхронизируемых фронтом, для нечетных вариантов.

3) Смоделировать параллельный регистр, разработанный в п. 12.1, в среде Electronics Workbench. Поочередно подать на входы D0 ... D3 код, соответствующий четырем младшим разрядам двоичного числа, равного номеру вашего варианта, и код на единицу меньший с помощью соответствующих ключей. Подать синхроимпульс С с помощью генератора слов Word Generation, включив его в ручном режиме Step, и убедиться в правильной работе параллельного регистра по состоянию логических пробников на его выходах.

4) Смоделировать регистр сдвига, разработанный в п. 12.2, в среде Electronics Workbench. Для имитации работы схемы подключить ее синхровход к генератору слов Word Generation, включив его в циклическом режиме Sycle. Подать на входы D0 ... D3 регистра код, соответствующий четырем младшим разрядам двоичного числа, равного номеру вашего варианта плюс три. Получить временные диаграммы входных и выходных сигналов сдвигающего регистра на экране логического анализатора Logic Analizer.

Содержание отчета

В отчет о выполненной работе включить следующие материалы:

1. тему и цель работы;

2. результаты выполнения заданий: исследуемые схемы, полученные таблицы переходов, временные диаграммы;

3. анализ полученных результатов