Файл: Лабораторная работа 3 Разработка схем цос на плис типа fpga.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 30.11.2023

Просмотров: 52

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Варианты 4,9

Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=10 Мгц, частота подавления Fstop=19 Мгц, фильтр имеет 7(8) коэффициентов.

-0.038645752774681554

0.12608229298259332

0.21239603218007624

0.28323565416535013

0.28323565416535013

0.21239603218007624

0.12608229298259332

-0.038645752774681554

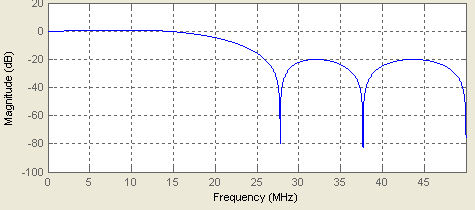

Варианты 5,12

Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=16 Мгц, частота подавления Fstop=26 Мгц, фильтр имеет 7(8) коэффициентов.

-0.024458211392255642

0.1385734715904797

0.20432647461212372

0.26273795244659287

0.26273795244659287

0.20432647461212372

0.1385734715904797

-0.024458211392255642

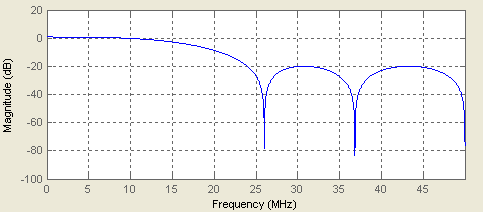

Варианты 6,11

Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=12 Мгц, частота подавления Fstop=24 Мгц, фильтр имеет 7(8) коэффициентов.

-0.058116432908280218

0.049430803026937656

0.20936548340988409

0.34953467616723588

0.34953467616723588

0.20936548340988409

0.049430803026937656

-0.058116432908280218

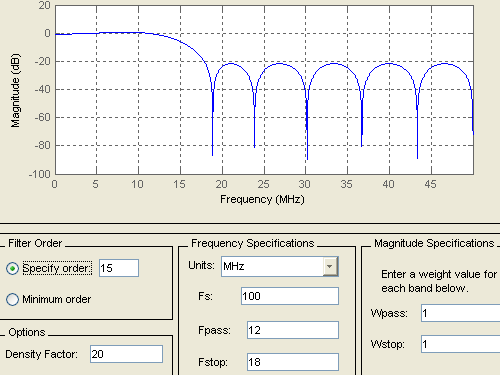

5. Разработать нерекурсивный фильтр нижних частот.

Частотные характеристики фильтра задаются в fdatool.

Определить реакцию на единичный импульс.

Проверить частотные характеристики фильтра.

Варианты 1-12

Частота дискретизации Fs=100 Мгц, частота пропускания Fpass=12Мгц, частота подавления Fstop=18 Мгц, фильтр имеет 15(16) коэффициентов.

0.037059570118627934

-0.02307320394269835

-0.052956774526219129

-0.062069563249109824

-0.017519265429228749

0.083952385419489794

0.20538459563162348

0.28813463217040336

0.28813463217040336

0.20538459563162348

0.083952385419489794

-0.017519265429228749

-0.062069563249109824

-0.052956774526219129

-0.02307320394269835

0.037059570118627934

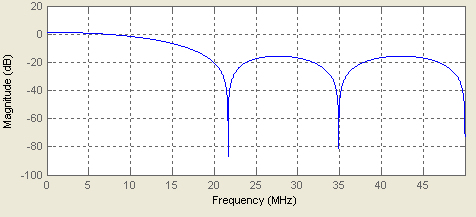

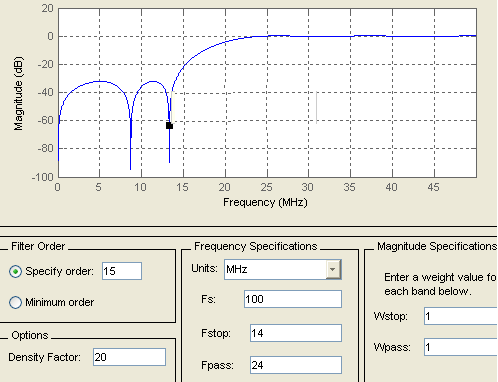

6. Разработать нерекурсивный фильтр высоких частот.

Частотные характеристики фильтра задаются в fdatool.

Определить реакцию на единичный импульс.

Проверить частотные характеристики фильтра.

Варианты 1-12

Частота дискретизации Fs=100 Мгц, частота подавления Fstop=14 Мгц, частота пропускания Fpass=24Мгц, фильтр имеет 15(16) коэффициентов.

0.017425690480098226

-0.0060410075547963783

-0.037948478513453787

-0.03481532541025964

0.036865329587026013

0.11464314902818995

0.045582703094050298

-0.52418449504105036

0.52418449504105036

-0.045582703094050298

-0.11464314902818995

-0.036865329587026013

0.03481532541025964

0.037948478513453787

0.0060410075547963783

-0.017425690480098226

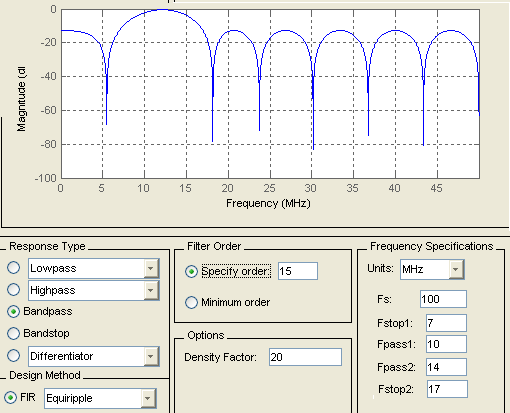

7. Разработать полосовой фильтр.

Частотные характеристики фильтра задаются в fdatool.

Определить реакцию на единичный импульс.

Проверить частотные характеристики фильтра.

Варианты 1-12

0.11624549922712731

-0.020790206504145009

-0.073891791891143851

-0.1177347608815346

-0.11345647456159967

-0.050813727213856463

0.03987313582326811

0.10544954752035379

0.10544954752035379

0.03987313582326811

-0.050813727213856463

-0.11345647456159967

-0.1177347608815346

-0.073891791891143851

-0.020790206504145009

0.11624549922712731

ПРИЛОЖЕНИЕ

Пример схемы на языке Verilog:

Y(n) = 0.75*x(n) + 0.25*x(n-1)

`timescale 1ns / 1ps

module f2(x, clk, y); // внешние сигналы

input [7:0] x; input clk; output reg [7:0] y;

reg [7:0] x75=0,xz25b=0,xz=0; // внутренние

wire [7:0] x25,x5,xz25; // сигналы

always @ (posedge clk) begin

x75 <= x5+x25; // 0.75*x(n)

xz25b <= xz25; // 0.25*x(n-1)

y <= x75 + xz25b;

xz <= x;

end

assign x5 = {x[7],x[7:1]}; // 0.5*x(n)

assign x25 = {x[7],x[7],x[7:2]}; // 0.25*x(n)

assign xz25 = {xz[7],xz[7],xz[7:2]};

endmodule

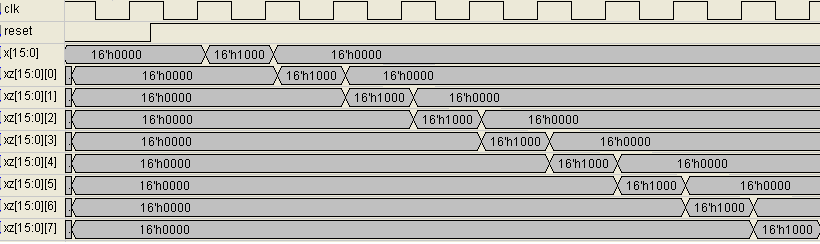

Нерекурсивный фильтр. Входной буфер

reg signed [15:0] xz [0 : 7]; // двумерный массив xz

always @ (posedge clk ) // 8 16-разрядных чисел

if (!in_reset_n) // сброс xz[0], xz[1],…, xz[7]

for (i = 0; i < 8; i = i + 8'd1) //

xz[i] <= #1 0;

else // сдвиг xz[1]<-xz[0], xz[2]<-xz[1],…, xz[7]<-xz[6],

begin // xz[0] <- x; выполняется одновременно

for (i = 1; i < 8; i = i + 8'd1)

xz[i] <= xz[i - 1]; //

xz [0] <= x; //

end

Нерекурсивный фильтр. Задание коэффициентов

wire signed [20:0] b[0 : 3]; // двумерный массив

assign b[0] = 21'h1f58fb;

assign b[1] = 21'h1c3fd;

assign b[2] = 21'h3622b;

assign b[3] = 21'h4ae1a;

Вычисление yn

Фильтр имеет симметричные коэффициенты: b0=bM-1, b1=bM-2, …

reg signed [15:0] xz [0 : 7]; // двумерный массив xz

reg signed [16:0] xzsum[0 : 3]; // сумм для сим коэф-тов

reg signed [37:0] bxx[0 : 3]; // Рез умнож на коэфф-ты

reg signed [38:0] s0[0 : 1]; // частичные суммы

reg signed [39:0] s1; //

always @ (posedge clk )

for (i = 0; i < 4; i = i + 8'd1) begin

xzsum[i] <= #1 xz[i] + xz[7 - i];

bxx[i] <= #1 xzsum[i] * b[i];

end

// xzsum[0] <= #1 xz[0]+xz[7]; xzsum[1] <= #1 xz[1]+xz[6];

// xzsum[2] <= #1 xz[2]+xz[5]; xzsum[3] <= #1 xz[3]+xz[4];

// bxx[0] <= #1 xzsum[0]*b[0]; bxx[1] <= #1 xzsum[1]*b[1];

// bxx[2] <= #1 xzsum[2]*b[2]; bxx[3] <= #1 xzsum[3]*b[3];

s0[0] <= bxx[0] + bxx[1]; s0[1] <= bxx[2] + bxx[3];

s1 <= s0[0] + s0[1]; //

Чтение входного сигнала из файла

reg signed [15:0] roms [100:0];

initial $readmemh("c:/PRJ/…sin01.txt", roms);

reg [15:0] addr2=0;

reg signed [15:0] rs=0, qsin=0;

always @ (posedge clk)

begin

if ((reset == 1'b0) || (addr2 == 16'd099))

addr2 <= 9'b000000000;

else

addr2 <= addr2 + 9'b000000001;

rs <= (roms[addr2]); qsin <= rs; x <= qsin; //

end

Запись результатов в файл

integer handle1,i,i0;

initial begin

handle1 = $fopen("Z:/nerfxx/… b11.txt"); i0=0;

#2000

for (i = 0; i < 1150; i = i + 1) begin //

$fwrite(handle1," %d %d %d %d ",

i, x, y, f1.b[i0]);

i0=i0+1;

if(i0 > 3)i0=0;

$fwrite(handle1,"\n");

#10;

end

#10;

$fclose(handle1);

end

Заголовок модуля

`timescale 1ns / 1ps // КИХ фильтр

module f07u (

output [15:0] y, // выход данных

input clk, in_reset_n,//

input signed [15:0] x // вход данных,

);

Включение компонента в проектируемое устройство

// .наименование контакта(имя сигнала)

f07u f1 (.in_reset_n(reset), .clk(clk), .x(x), .y(y));