Файл: Лабораторная работа 7 по дисциплине структурное моделирование электротехнических систем Логические элементы. Триггеры.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 30.11.2023

Просмотров: 22

Скачиваний: 3

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Министерство науки и высшего образования Российской Федерации

ФГАОУ ВО «Уральский федеральный университет имени первого Президента России Б.Н. Ельцина»

Уральский энергетический институт

Кафедра «Электротехника»

ЛАБОРАТОРНАЯ РАБОТА №7

ПО ДИСЦИПЛИНЕ

«СТРУКТУРНОЕ МОДЕЛИРОВАНИЕ ЭЛЕКТРОТЕХНИЧЕСКИХ СИСТЕМ»

Логические элементы. Триггеры.

| Руководитель Студенты группы ЭН-490006 | ______________ ______________ | Томашевский Д.Н. Бочкарев Д.А |

Екатеринбург 2023

Цель работы: рассмотрение и изучение моделей логических элементов в программе MatLAB. Построение моделей триггеров.

-

RS-триггер

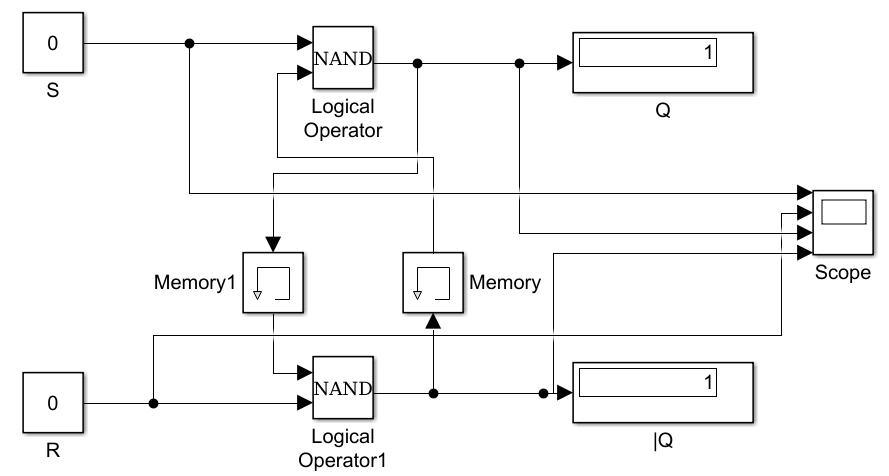

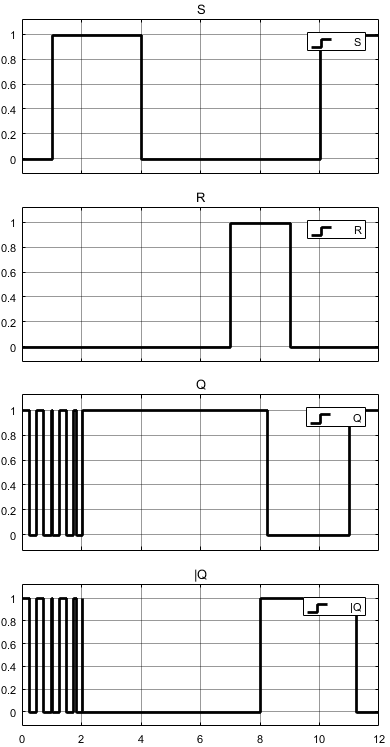

На рисунке 1 представлена схема модели RS-триггера:

Рисунок 1 – Модель RS-триггера на элементах И-НЕ

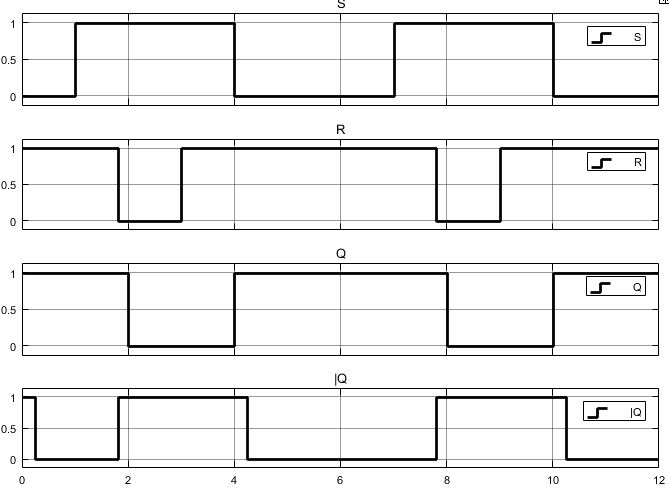

Графики и таблица истинности данного триггера представлены ниже:

| S | R | Q | |Q |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | Предыдущее состояние | Предыдущее состояние |

| 0 | 0 | - | - |

Рисунок 2 – Графики сигналов RS-триггера

При значениях S=1 и R=1 соответствует сохранению триггером предыдущего состояние, что видно на отрезке времени 7-8 с.

При значениях S=0 и R=0 триггер принимает неопределенное значение, не соответствующее ни 1, ни 0.

-

Тактируемый RS-триггер

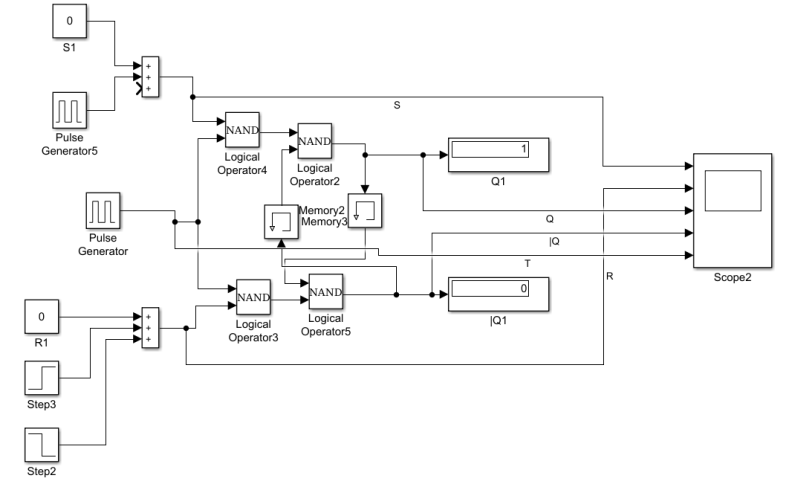

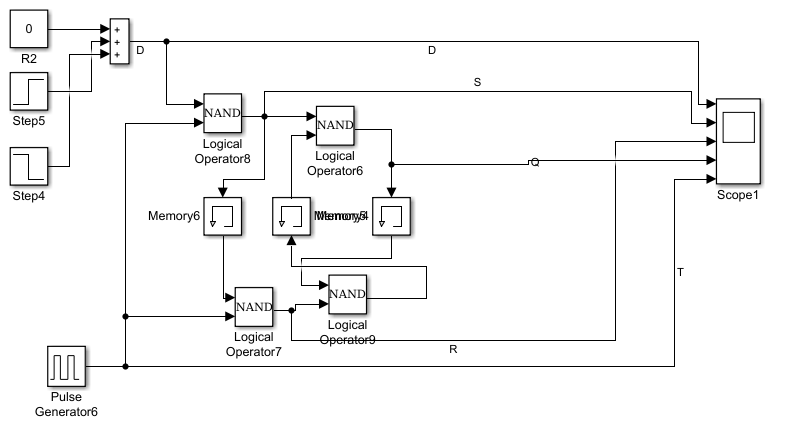

На рисунке 3 представлена схема модели тактируемого RS-триггера:

Рисунок 3 – Модель тактируемого RS-триггера на элементах И-НЕ

Графики и таблица истинности данного триггера представлены ниже:

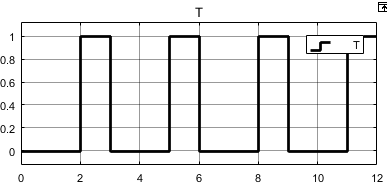

Рисунок 4 – Графики сигналов тактируемого RS-триггера

Таблица 2 – Таблица истинности тактируемого RS-триггера

| T | S | R | Q | |Q |

| 0 | 0 | 0 | - | - |

| 0 | 1 | 0 | - | - |

| 1 | 1 | 0 | 1 | 0 |

| 0 (отключение) | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 (сохранение) | 0 (сохранение) |

| 1 | 0 | 0 | 1 (сохранение) | 0 (сохранение) |

| 1 | 0 | 1 | 0 | 1 |

Особое действие на тактируемый RS-триггер имеет управляющий сигнал T. Он влияет на способность триггера изменять выходящий сигнал в необходимый момент времени, тем самым создавая задержкий.

В начальный момент времени до подачи управляющего сигнала триггер находится в неопределенном состоянии.

-

D-триггер

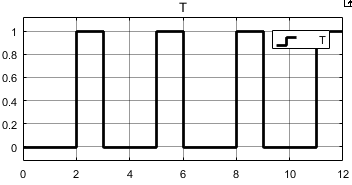

На рисунке 5 представлена схема модели D-триггера:

Рисунок 5 – Модель D-триггера на элементах И-НЕ

Графики и таблица истинности данного триггера представлены ниже:

Рисунок 6 – Графики сигналов D-триггера

Таблица 2 – Таблица истинности D-триггера

| T | D | S | R | Q |

| 0 | 0 | 1 | 1 | - |

| 1 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

-

T-триггер

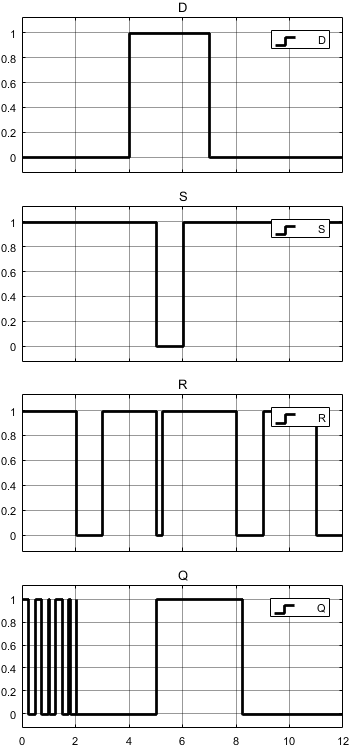

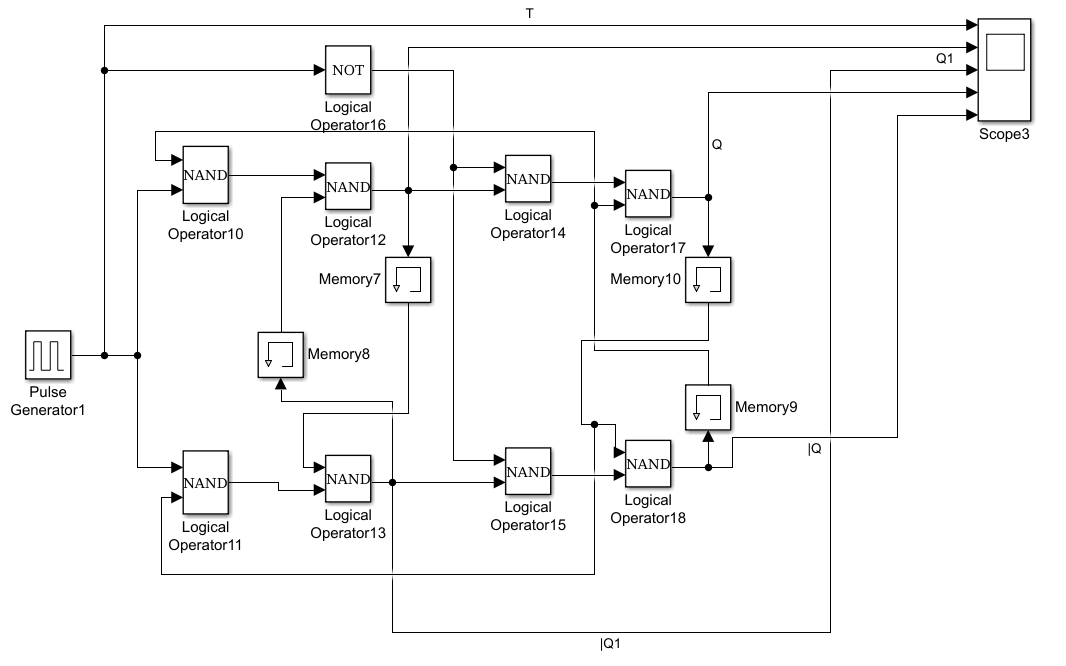

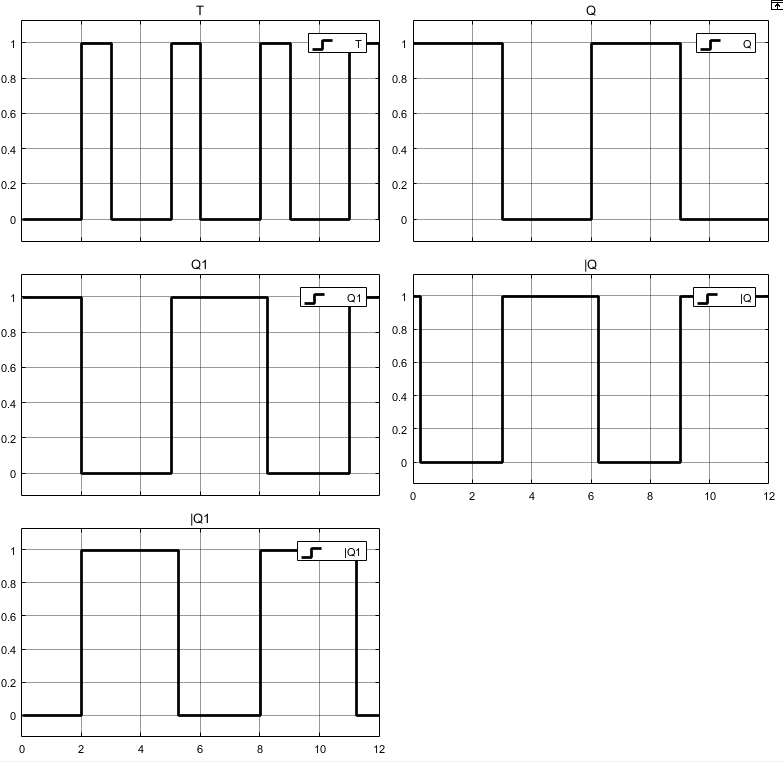

На рисунке 7 представлена схема модели T-триггера:

Рисунок 7 – Модель T-триггера на элементах И-НЕ, НЕ

В Memory7 устанавливается начальное значение 1.

Графики сигналов данного триггера представлены ниже:

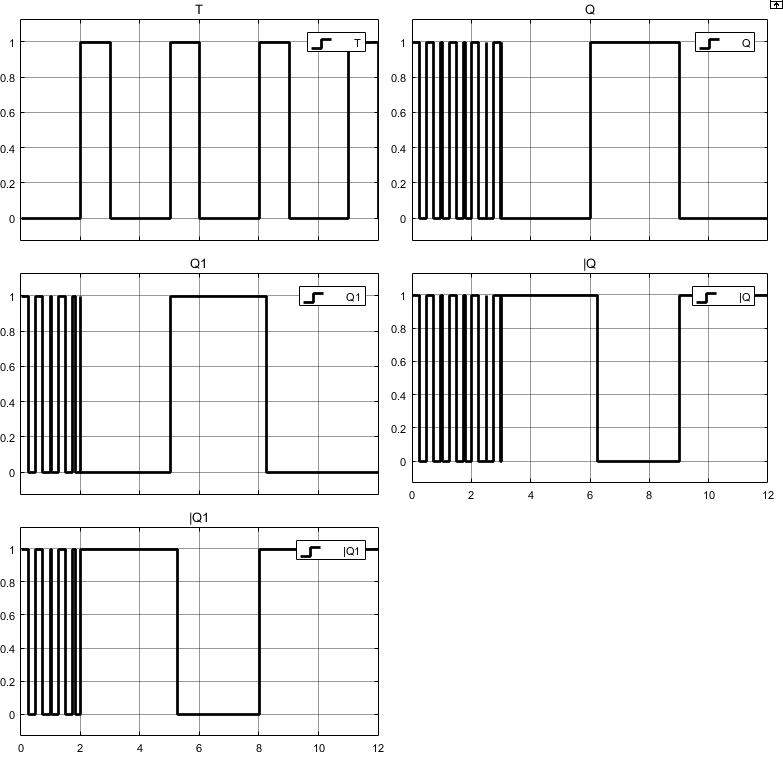

Рисунок 8 – Графики сигналов T-триггера

При каждой подаче единичного значения управляющего сигнала, выходной сигнал меняет свое значение с 1 на 0, либо с 0 на 1, в зависимости от исходного значения.

-

JK-триггер

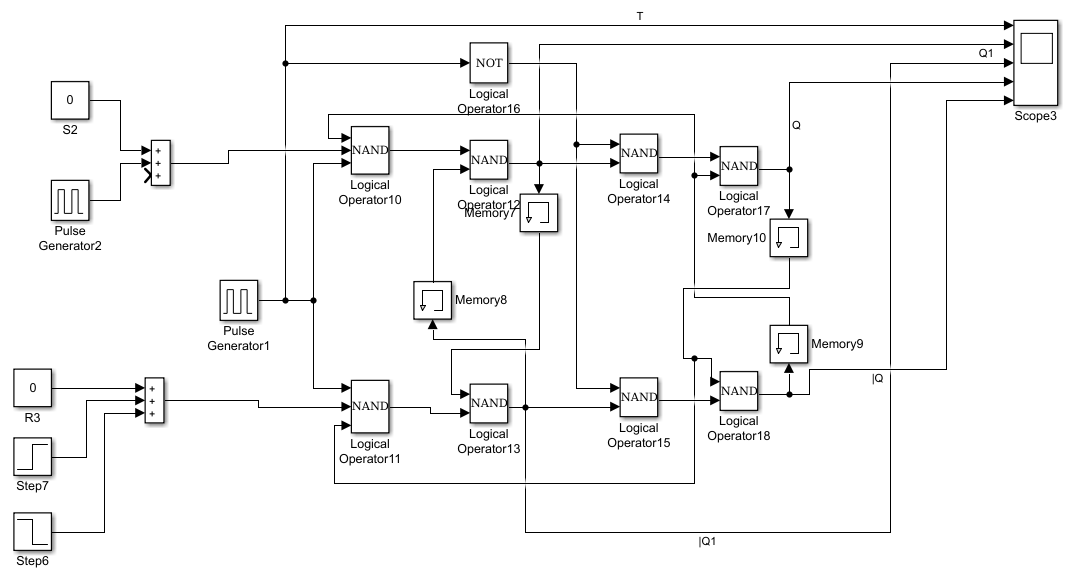

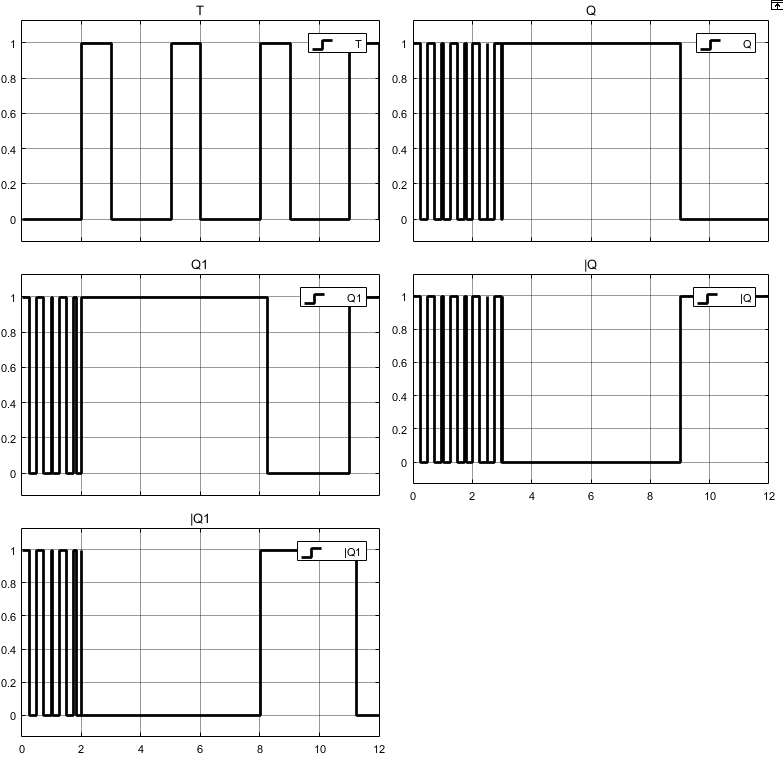

На рисунке 7 представлена схема модели JK-триггера:

Рисунок 7 – Модель JK-триггера на элементах И-НЕ, НЕ

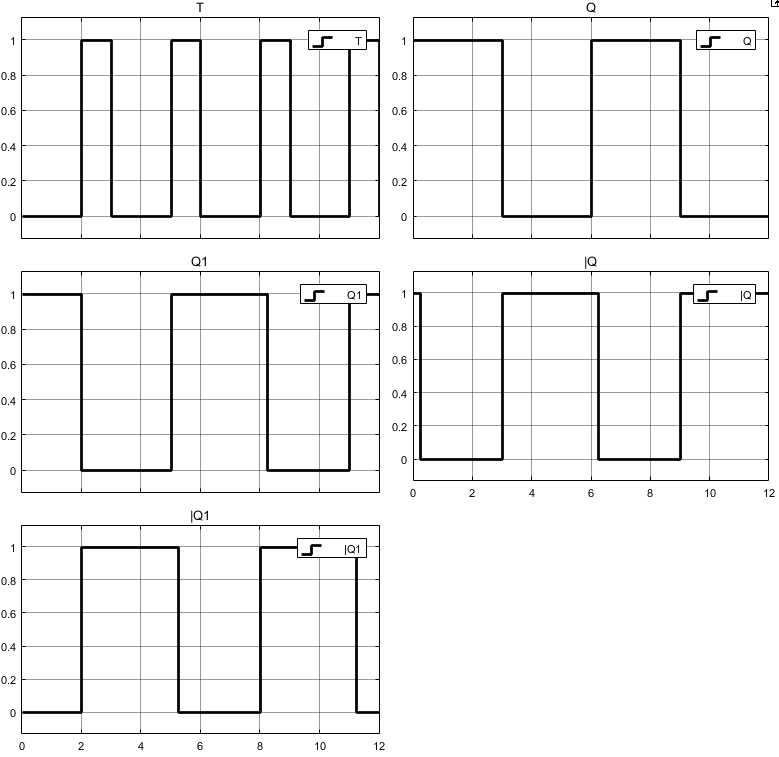

Графики сигналов данного триггера, работающего как тактируемый RS-триггер, D-триггер и T-триггер, представлены ниже:

Рисунок 8 – Графики сигналов JK-триггера, работающего как тактируемый RS-триггер

Рисунок 9 – Графики сигналов JK-триггера, работающего как D-триггер

Рисунок 10 – Графики сигналов JK-триггера, работающего как T-триггер

Полученные графики аналогичны графикам RS-, D- и T-триггеров. На основании этого можно сделать вывод о том, что JK-триггер может работать как RS-, D- и T-триггеры.

-

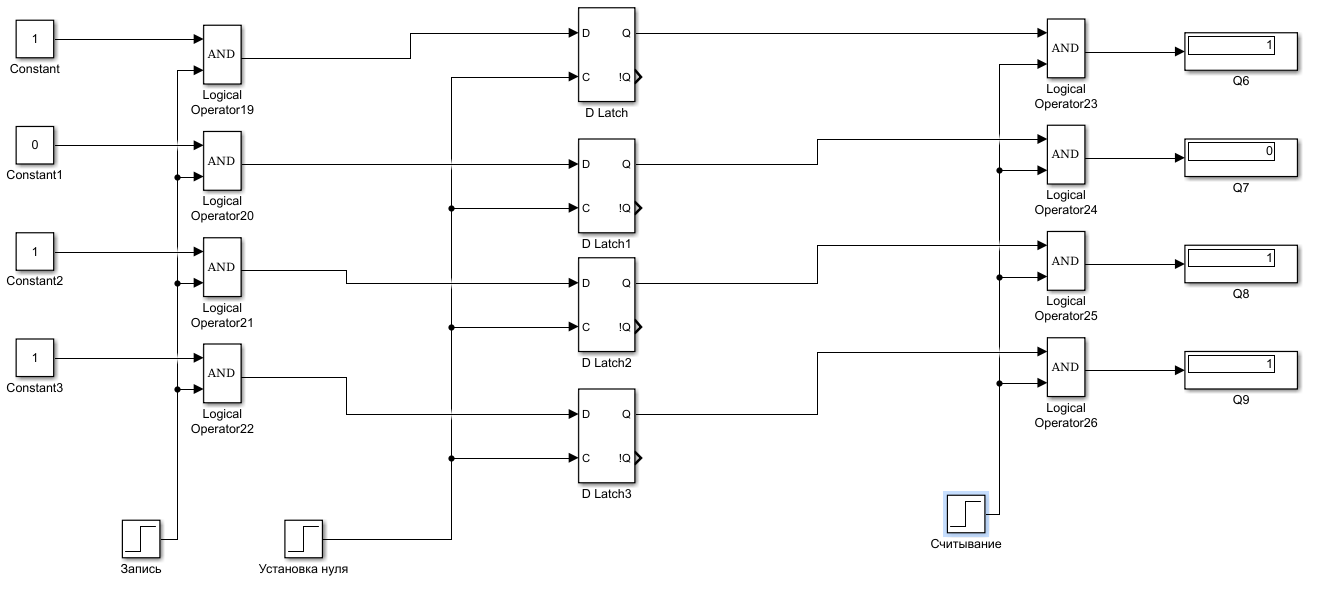

Четырёхразрядный регистр памяти

Схема модели четырёхразрядного регистра памяти изображена на рисунке 11:

Рисунок 11 - Схема модели четырёхразрядного регистра памяти

Перед записью двоичного числа с помощью Step «Установка нуля» подаётся сигнал, что позволяет установить D-триггеры в состояние 0.

Рассмотрим запись и считывание первого разряда «1». Когда подается сигнал от «Запись», на выходе элемента «И» появляется «1», поскольку на входе подается два единичных сигнала. Код входного сигнала записывается в регистр (D-триггер). Данная запись сохраняется и не изменяется в независимости от смены входного сигнала. Считывание происходит после подачи сигнала на элемент «И». Т.к. два сигнала имеют единичные значения, то на выходе также будет «1», что соответствует записанному значению. Аналогично происходит запись-сохранение-считывание с остальными разрядами.

-

Логическая функция

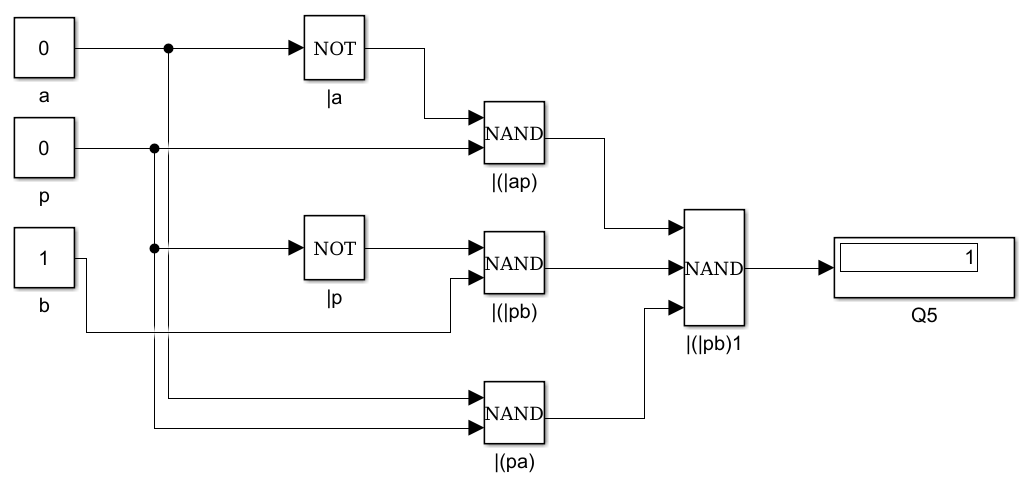

Схема модели логической функции

изображена на рисунке 12:

изображена на рисунке 12:

Рисунок 12 – Схема модели логической функции

Таблица истинности некоторых значений приведена ниже:

Таблица 3 – Таблица истинности логической функции

| a | p | b | y |

| 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |