ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 07.12.2023

Просмотров: 31

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

С была не меньше времени переключения триггера. Временем переключения (срабатывания, установки) триггера называется время, которое проходит от момента изменения входных сигналов до соответствующего изменения состояния выходов и определяющееся задержками распространения сигнала логическими элементами, входящими в состав триггера.

Статический D триггер

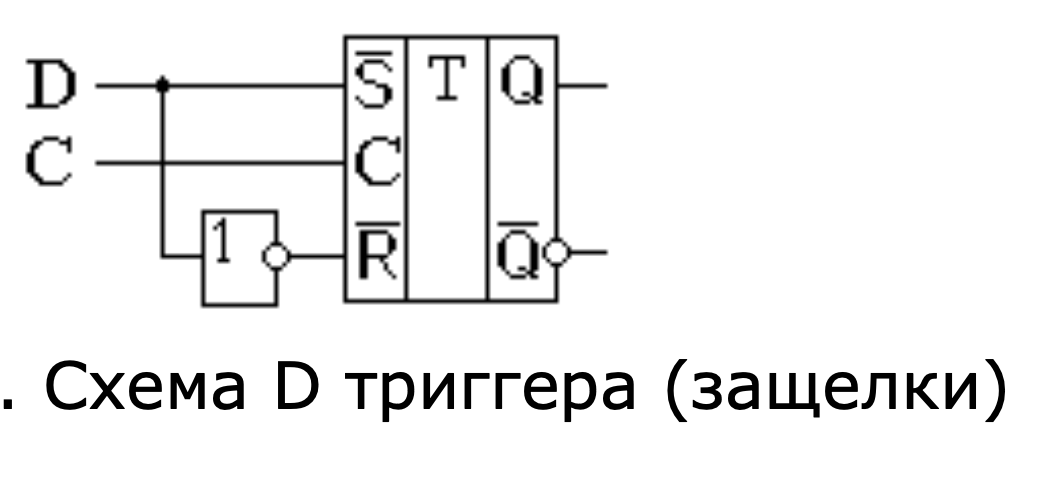

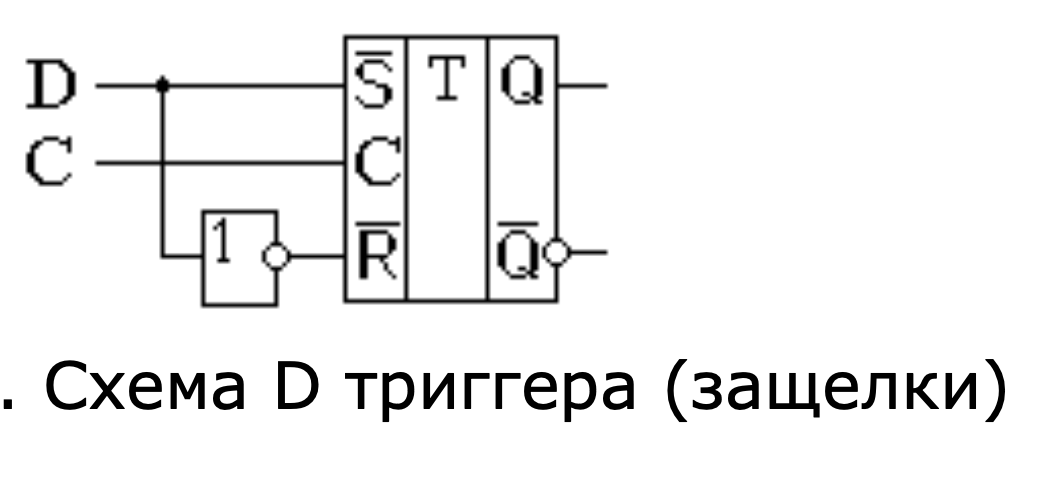

В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке 1.

Рисунок 1. Схема D триггера (защелки)

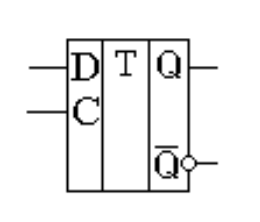

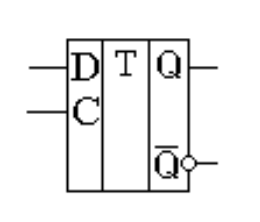

Рисунок 2. Условно-графическое обозначение D триггера (защелки)

D-триггер (от английского DELAY) называют информационным триггером, также триггером задержки. Конкретное значение задержки определяется частотой следования импульсов синхронизации. D - триггер бывает только синхронным. Он может управляться (переключаться) как уровнем тактирующего импульса, так и его фронтом. Для триггера типа D, состояние в интервале времени между сигналом на входной линии и следующим состоянием триггера формируется проще, чем для любого другого типа.

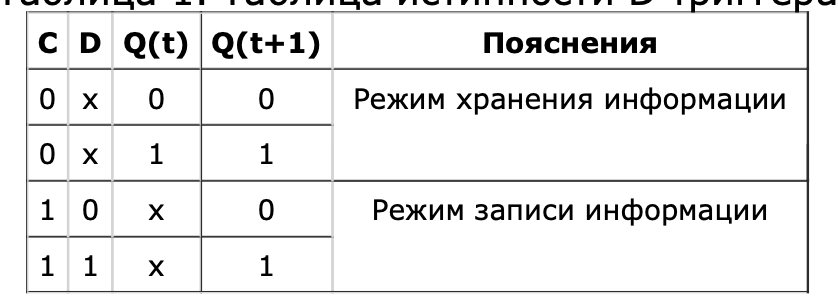

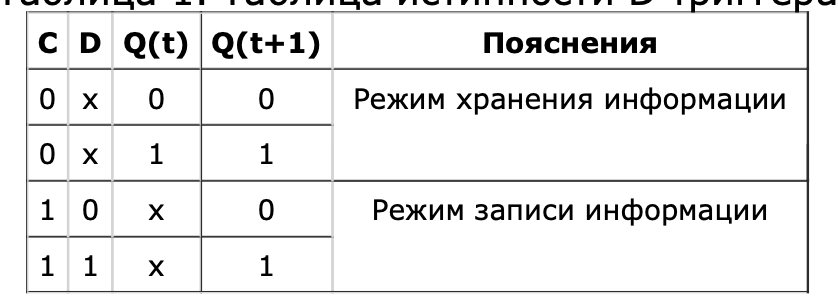

Таблица истинности D триггера достаточно проста, она приведена в таблице 1. Как видно из этой таблицы, этот триггер способен запоминать по синхросигналу и хранить один бит информации.

Таблица 1. Таблица истинности D триггера

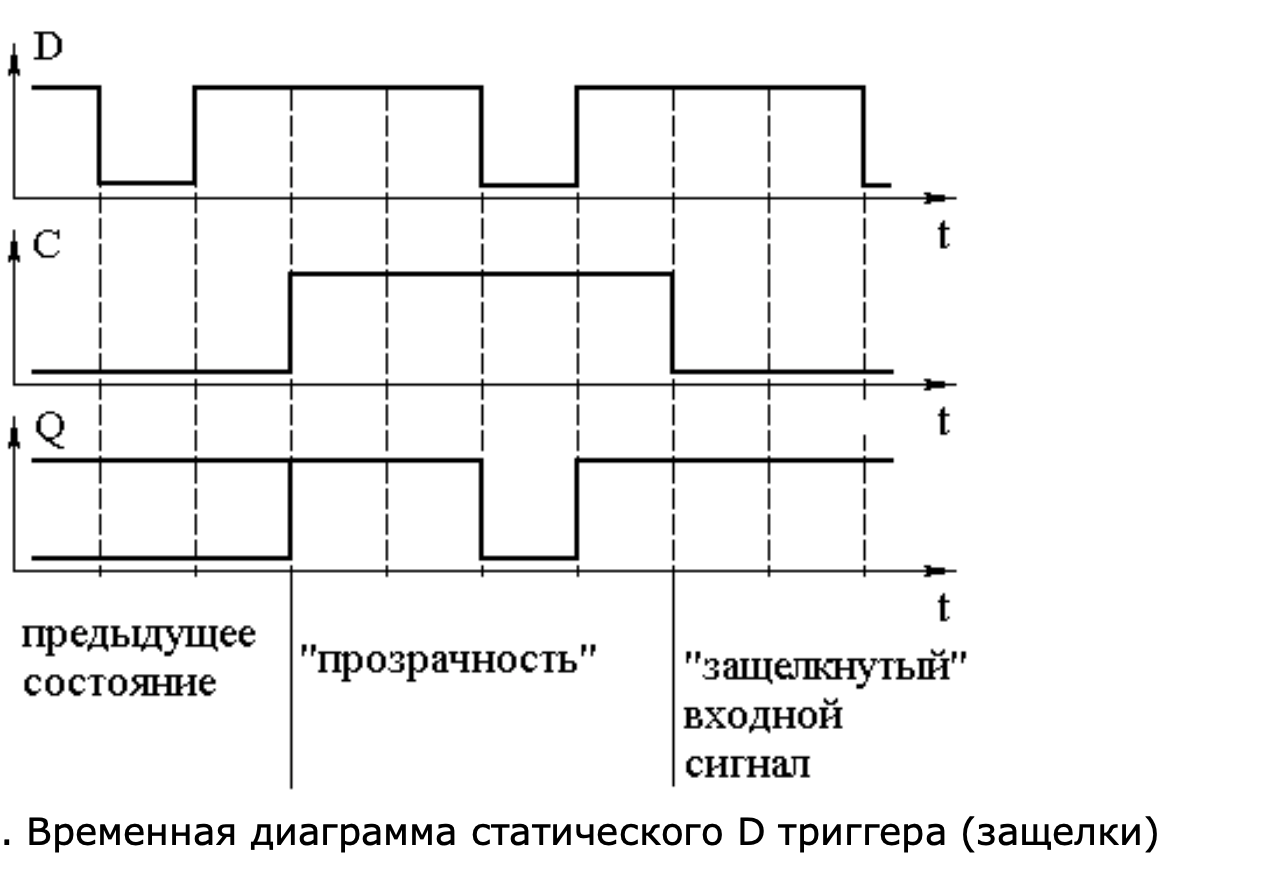

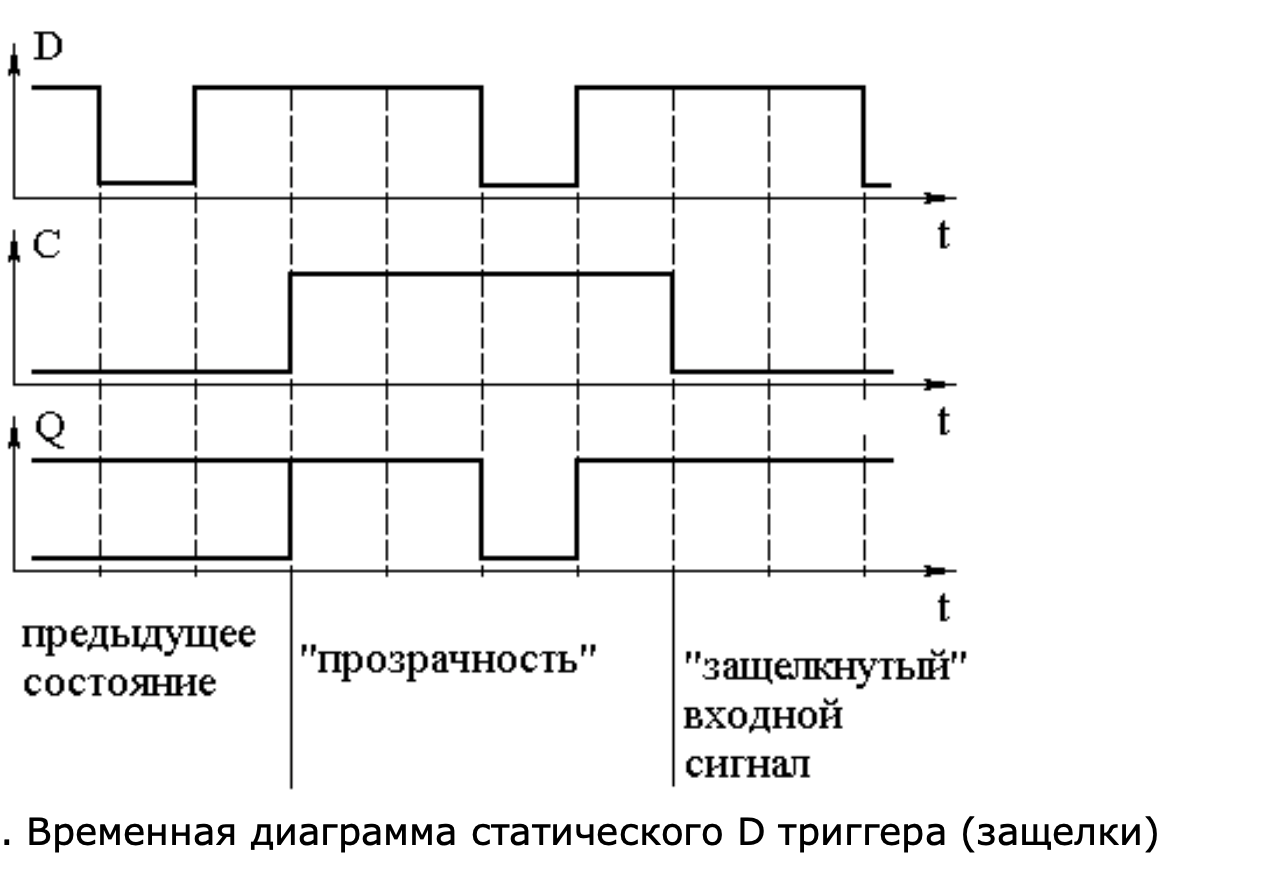

Во всех рассмотренных ранее схемах синхронных триггеров синхросигнал работает по уровню, поэтому триггеры называются триггерами, работающими по уровню или статическими триггерами. Ещё одно название статических D триггеров, пришедшее из иностранной литературы — триггеры-защёлки (latch). Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рисунке 8.

Рисунок 8. Временная диаграмма статического D триггера (защелки)

Для формирования подобной временной диаграммы уже недостаточно механических ключей на входе схемы и логических пробников на светодиодах. Для формирования входных сигналов потребуются генераторы импульсов, а для наблюдения временных диаграмм к выходу схемы следует подключить многоканальный осциллограф.

По временной диаграмме, приведенной на рисунке 8 видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера.

Входное напряжение запоминается в статическом D триггере только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент, отсюда и название — триггер-защелка.

Принципиально в схеме статического D триггера входной переходной процесс (опасные гонки) может беспрепятственно проходить на выход D триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.

Основным недостатком простейшего D-триггера (защелки), рассмотренного в предыдущей статье, является наличие режима "прозрачности". Пока на входе синхронизации присутствует высокий потенциал, триггер записывает входную информацию. Для того, чтобы избежать прохождения входного сигнала на выход схемы приходится на вход триггера подавать очень узкие импульсы.

Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеальном случае длительность фронта импульса равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала.

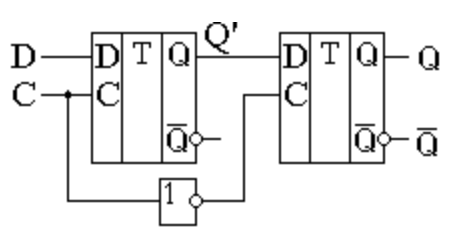

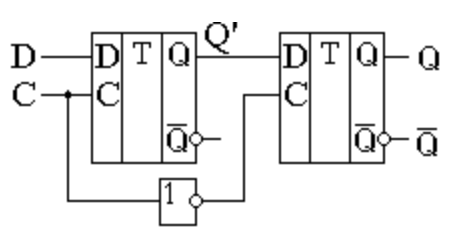

Динамический D триггер, запоминающий входную информацию по фронту, может быть построен из двух статических D триггеров. Сигнал синхронизации C будем подавать на статические D триггеры в противофазе. Схема триггера, запоминающего входную двоичную информацию по фронту, приведена на рисунке 1.

Рисунок 1. Схема динамического D триггера, работающего по фронту

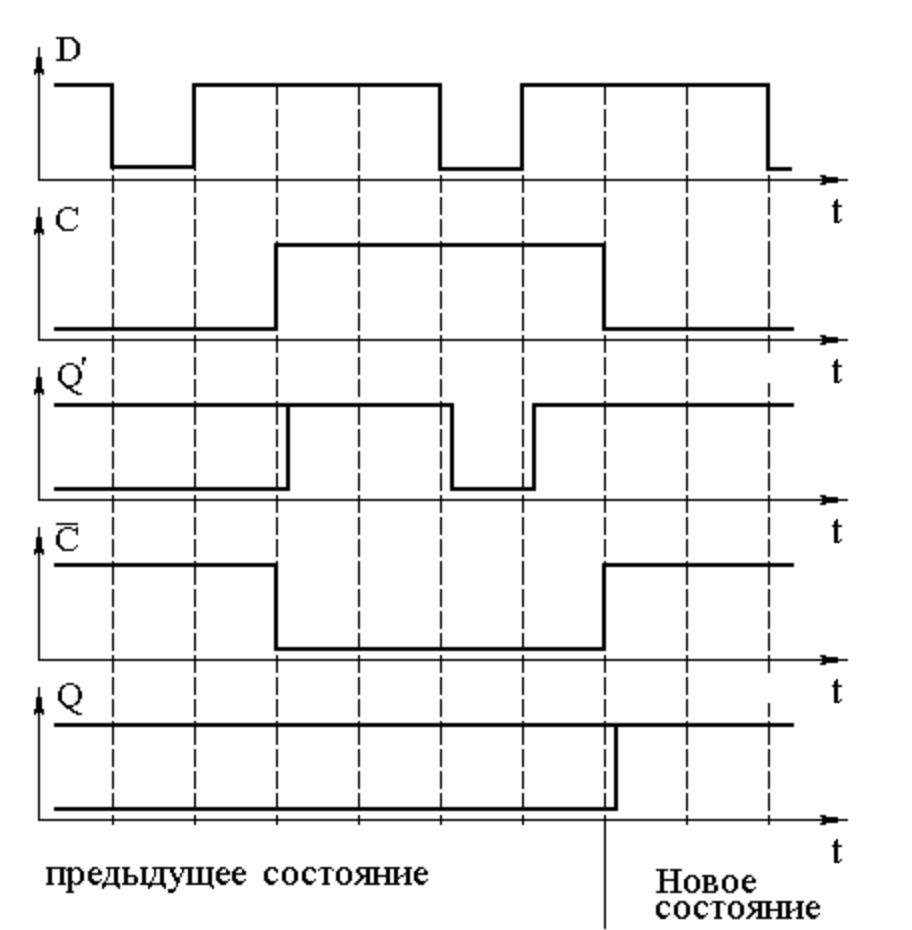

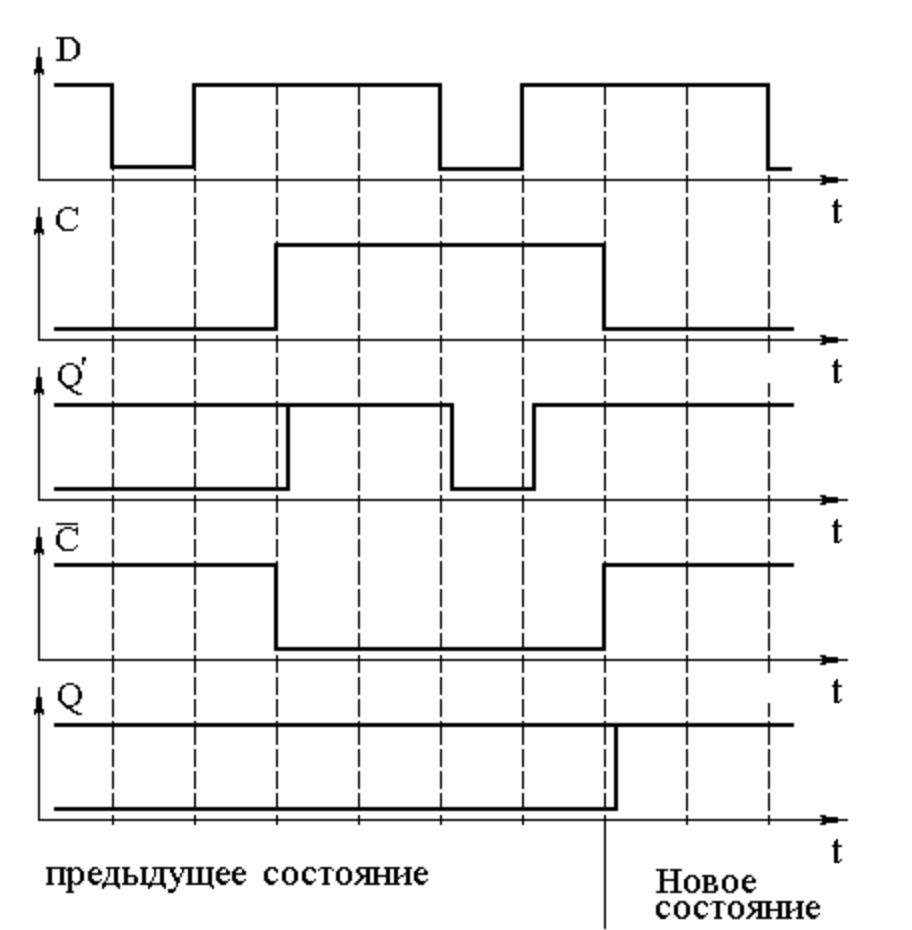

Рассмотрим работу схемы, приведенной на рисунке 1 подробнее. Для этого воспользуемся временными диаграммами, показанными на рисунке 2. На этих временных диаграммах обозначение Q' соответствует сигналу на выходе первого статического D триггера. Так как на вход синхронизации второго статического D триггера тактовый сигнал поступает через инвертор, то когда первый триггер находится в режиме хранения, второй пропускает сигнал на выход схемы. И наоборот, когда первый D триггер пропускает сигнал с входа схемы на свой выход, то второй находится в режиме хранения.

Рисунок 2. Временные диаграммы динамического D триггера

Обратите внимание, что сигнал на выходе всей схемы D триггера в целом не зависит от сигнала на входе "D". Если первый D триггер пропускает сигнал данных со своего входа на выход, то второй статический D триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться.

В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 1 запоминается только в момент изменения сигнала на синхронизирующем входе "C" с единичного потенциала на нулевой. Это полезно не только с точки зрения формирования синхронизирующего сигнала. На динамических D триггерах, в отличие от статических, можно строить последовательные регистры и счетчики. В англоязычной литературе только такие схемы называют D триггерами.

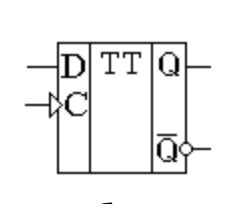

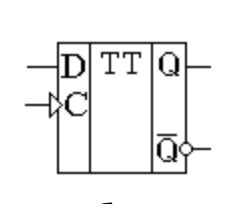

Условно-графическое обозначение динамического D триггера, запоминающего информацию по фронту тактового сигнала, приведено на рисунке 3.

Рисунок 3. Условно-графическое обозначение динамического D триггера

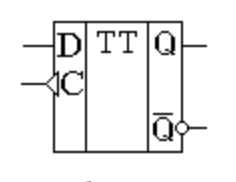

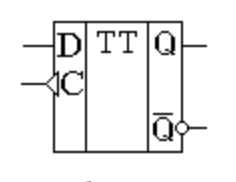

То, что динамический D триггер запоминает входной сигнал по фронту, отображается на условно-графическом обозначении треугольником, изображённым на выводе входа синхронизации. Если запоминание сигнала по входу D происходит по спадающему фронту, то треугольник разворачивают в другую сторону (вершиной ко входу C). То, что внутри динамического триггера находится два статических триггера, отображается в среднем поле условно-графического изображения двойной буквой T.

Рисунок 4. Условно-графическое обозначение динамического D триггера с запоминанием по заднему фронту

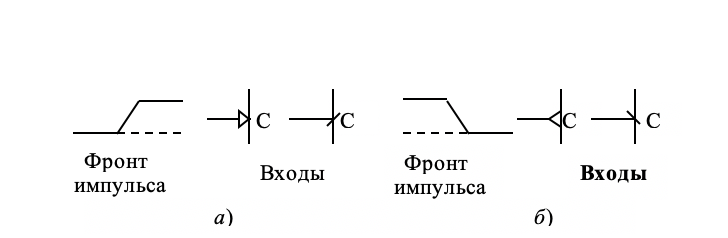

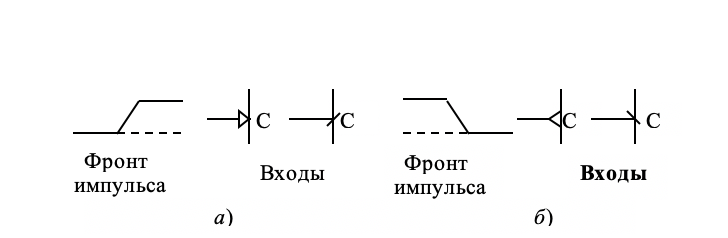

Иногда при изображении динамического входа используют другое обозначение, по какому фронту триггер (или триггеры) изменяет своё состояние. В этом случае используется обозначение входа, как это показано на рисунке 4.

Рисунок 5. Альтернативное обозначение динамических входов

На рисунке 5а обозначен динамический вход, работающий по переднему (нарастающему) фронту сигнала. На рисунке 5б обозначен динамический вход, работающий по заднему (спадающему) фронту сигнала.

T-триггеры

T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.

T-триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации "C", так как счетные триггеры строятся при помощи схем с обратной связью

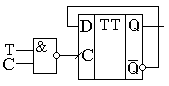

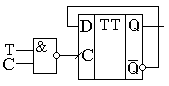

T триггер можно синтезировать из любого двухступенчатого триггера. При этом не важно ТТЛ или КМОП технология используется. Рассмотрим пример синтеза T триггера из динамического D триггера. Для того чтобы превратить D триггер в счётный, необходимо ввести цепь обратной связи с инверсного выхода этого триггера на вход, как показано на рисунке 1.

Рисунок 1. Схема T триггера, построенная на основе D триггера

Временная диаграмма T триггера приведена на рисунке 2. При построении этой временной диаграммы был использован триггер, работающий по заднему фронту синхронизирующего сигнала.

Рисунок 2. Временные диаграммы T триггера

Т-триггеры используются при построении схем различных счётчиков, поэтому в составе БИС различного назначения обычно есть готовые модули этих триггеров. Условно-графическое обозначение T триггера приведено на рисунке 3.

Рисунок 3. Условно-графическое обозначение T триггера

Существует еще одно представление T триггера. При разработке схем синхронных двоичных счетчиков важно осуществлять одновременную запись во все его триггеры. В этом случае вход T триггера служит только для разрешения изменения состояния на противоположное, а синхронизация производится отдельным входом "C". Подобная схема T триггера приведена на рисунке 4.

Рисунок 4. Схема синхронного T триггера, построенная на основе D триггера

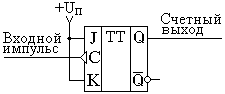

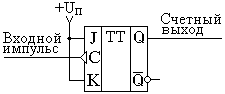

Подобная схема счетного триггера может быть реализована и на JK триггере. Принципиальная схема синхронного T-триггера, выполненная на JK-триггере показана на рисунке 5.

Рисунок 5. Схема синхронного T триггера, построенная на основе JK триггера

Временная диаграмма синхронного T триггера приведена на рисунке 5, а его условно-графическое обозначение — на рисунке 6.

Рисунок 6. Временные диаграммы синхронного T триггера

Рисунок 7. Условно-графическое обозначение синхронного T триггера

Выводы T-триггеры широко применяются в схемах деления и умножения частоты. Без них было бы невозможна реализация синтезаторов частот, которые применяются в качестве задающих генераторов в передатчиках и гетеродинов в приемниках раций, мобильных телефонов или GSM навигаторов. Не менее важна роль T-триггеров в формировании тактовой частоты цифровых микросхем, таких как центральные процессоры компьютеров, планшетов или цифровых фотоаппаратов.

Статический D триггер

В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке 1.

Рисунок 1. Схема D триггера (защелки)

Рисунок 2. Условно-графическое обозначение D триггера (защелки)

D-триггер (от английского DELAY) называют информационным триггером, также триггером задержки. Конкретное значение задержки определяется частотой следования импульсов синхронизации. D - триггер бывает только синхронным. Он может управляться (переключаться) как уровнем тактирующего импульса, так и его фронтом. Для триггера типа D, состояние в интервале времени между сигналом на входной линии и следующим состоянием триггера формируется проще, чем для любого другого типа.

Таблица истинности D триггера достаточно проста, она приведена в таблице 1. Как видно из этой таблицы, этот триггер способен запоминать по синхросигналу и хранить один бит информации.

Таблица 1. Таблица истинности D триггера

Во всех рассмотренных ранее схемах синхронных триггеров синхросигнал работает по уровню, поэтому триггеры называются триггерами, работающими по уровню или статическими триггерами. Ещё одно название статических D триггеров, пришедшее из иностранной литературы — триггеры-защёлки (latch). Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рисунке 8.

Рисунок 8. Временная диаграмма статического D триггера (защелки)

Для формирования подобной временной диаграммы уже недостаточно механических ключей на входе схемы и логических пробников на светодиодах. Для формирования входных сигналов потребуются генераторы импульсов, а для наблюдения временных диаграмм к выходу схемы следует подключить многоканальный осциллограф.

По временной диаграмме, приведенной на рисунке 8 видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера.

Входное напряжение запоминается в статическом D триггере только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент, отсюда и название — триггер-защелка.

Принципиально в схеме статического D триггера входной переходной процесс (опасные гонки) может беспрепятственно проходить на выход D триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.

Динамический D триггер

Основным недостатком простейшего D-триггера (защелки), рассмотренного в предыдущей статье, является наличие режима "прозрачности". Пока на входе синхронизации присутствует высокий потенциал, триггер записывает входную информацию. Для того, чтобы избежать прохождения входного сигнала на выход схемы приходится на вход триггера подавать очень узкие импульсы.

Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеальном случае длительность фронта импульса равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала.

Динамический D триггер, запоминающий входную информацию по фронту, может быть построен из двух статических D триггеров. Сигнал синхронизации C будем подавать на статические D триггеры в противофазе. Схема триггера, запоминающего входную двоичную информацию по фронту, приведена на рисунке 1.

Рисунок 1. Схема динамического D триггера, работающего по фронту

Рассмотрим работу схемы, приведенной на рисунке 1 подробнее. Для этого воспользуемся временными диаграммами, показанными на рисунке 2. На этих временных диаграммах обозначение Q' соответствует сигналу на выходе первого статического D триггера. Так как на вход синхронизации второго статического D триггера тактовый сигнал поступает через инвертор, то когда первый триггер находится в режиме хранения, второй пропускает сигнал на выход схемы. И наоборот, когда первый D триггер пропускает сигнал с входа схемы на свой выход, то второй находится в режиме хранения.

Рисунок 2. Временные диаграммы динамического D триггера

Обратите внимание, что сигнал на выходе всей схемы D триггера в целом не зависит от сигнала на входе "D". Если первый D триггер пропускает сигнал данных со своего входа на выход, то второй статический D триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться.

В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 1 запоминается только в момент изменения сигнала на синхронизирующем входе "C" с единичного потенциала на нулевой. Это полезно не только с точки зрения формирования синхронизирующего сигнала. На динамических D триггерах, в отличие от статических, можно строить последовательные регистры и счетчики. В англоязычной литературе только такие схемы называют D триггерами.

Условно-графическое обозначение динамического D триггера, запоминающего информацию по фронту тактового сигнала, приведено на рисунке 3.

Рисунок 3. Условно-графическое обозначение динамического D триггера

То, что динамический D триггер запоминает входной сигнал по фронту, отображается на условно-графическом обозначении треугольником, изображённым на выводе входа синхронизации. Если запоминание сигнала по входу D происходит по спадающему фронту, то треугольник разворачивают в другую сторону (вершиной ко входу C). То, что внутри динамического триггера находится два статических триггера, отображается в среднем поле условно-графического изображения двойной буквой T.

Рисунок 4. Условно-графическое обозначение динамического D триггера с запоминанием по заднему фронту

Иногда при изображении динамического входа используют другое обозначение, по какому фронту триггер (или триггеры) изменяет своё состояние. В этом случае используется обозначение входа, как это показано на рисунке 4.

Рисунок 5. Альтернативное обозначение динамических входов

На рисунке 5а обозначен динамический вход, работающий по переднему (нарастающему) фронту сигнала. На рисунке 5б обозначен динамический вход, работающий по заднему (спадающему) фронту сигнала.

T-триггеры

T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.

T-триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации "C", так как счетные триггеры строятся при помощи схем с обратной связью

T триггер можно синтезировать из любого двухступенчатого триггера. При этом не важно ТТЛ или КМОП технология используется. Рассмотрим пример синтеза T триггера из динамического D триггера. Для того чтобы превратить D триггер в счётный, необходимо ввести цепь обратной связи с инверсного выхода этого триггера на вход, как показано на рисунке 1.

Рисунок 1. Схема T триггера, построенная на основе D триггера

Временная диаграмма T триггера приведена на рисунке 2. При построении этой временной диаграммы был использован триггер, работающий по заднему фронту синхронизирующего сигнала.

Рисунок 2. Временные диаграммы T триггера

Т-триггеры используются при построении схем различных счётчиков, поэтому в составе БИС различного назначения обычно есть готовые модули этих триггеров. Условно-графическое обозначение T триггера приведено на рисунке 3.

Рисунок 3. Условно-графическое обозначение T триггера

Существует еще одно представление T триггера. При разработке схем синхронных двоичных счетчиков важно осуществлять одновременную запись во все его триггеры. В этом случае вход T триггера служит только для разрешения изменения состояния на противоположное, а синхронизация производится отдельным входом "C". Подобная схема T триггера приведена на рисунке 4.

Рисунок 4. Схема синхронного T триггера, построенная на основе D триггера

Подобная схема счетного триггера может быть реализована и на JK триггере. Принципиальная схема синхронного T-триггера, выполненная на JK-триггере показана на рисунке 5.

Рисунок 5. Схема синхронного T триггера, построенная на основе JK триггера

Временная диаграмма синхронного T триггера приведена на рисунке 5, а его условно-графическое обозначение — на рисунке 6.

Рисунок 6. Временные диаграммы синхронного T триггера

Рисунок 7. Условно-графическое обозначение синхронного T триггера

Выводы T-триггеры широко применяются в схемах деления и умножения частоты. Без них было бы невозможна реализация синтезаторов частот, которые применяются в качестве задающих генераторов в передатчиках и гетеродинов в приемниках раций, мобильных телефонов или GSM навигаторов. Не менее важна роль T-триггеров в формировании тактовой частоты цифровых микросхем, таких как центральные процессоры компьютеров, планшетов или цифровых фотоаппаратов.