ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 13.05.2019

Просмотров: 693

Скачиваний: 6

СОДЕРЖАНИЕ

Двухступенчатый синхронный RS-триггер

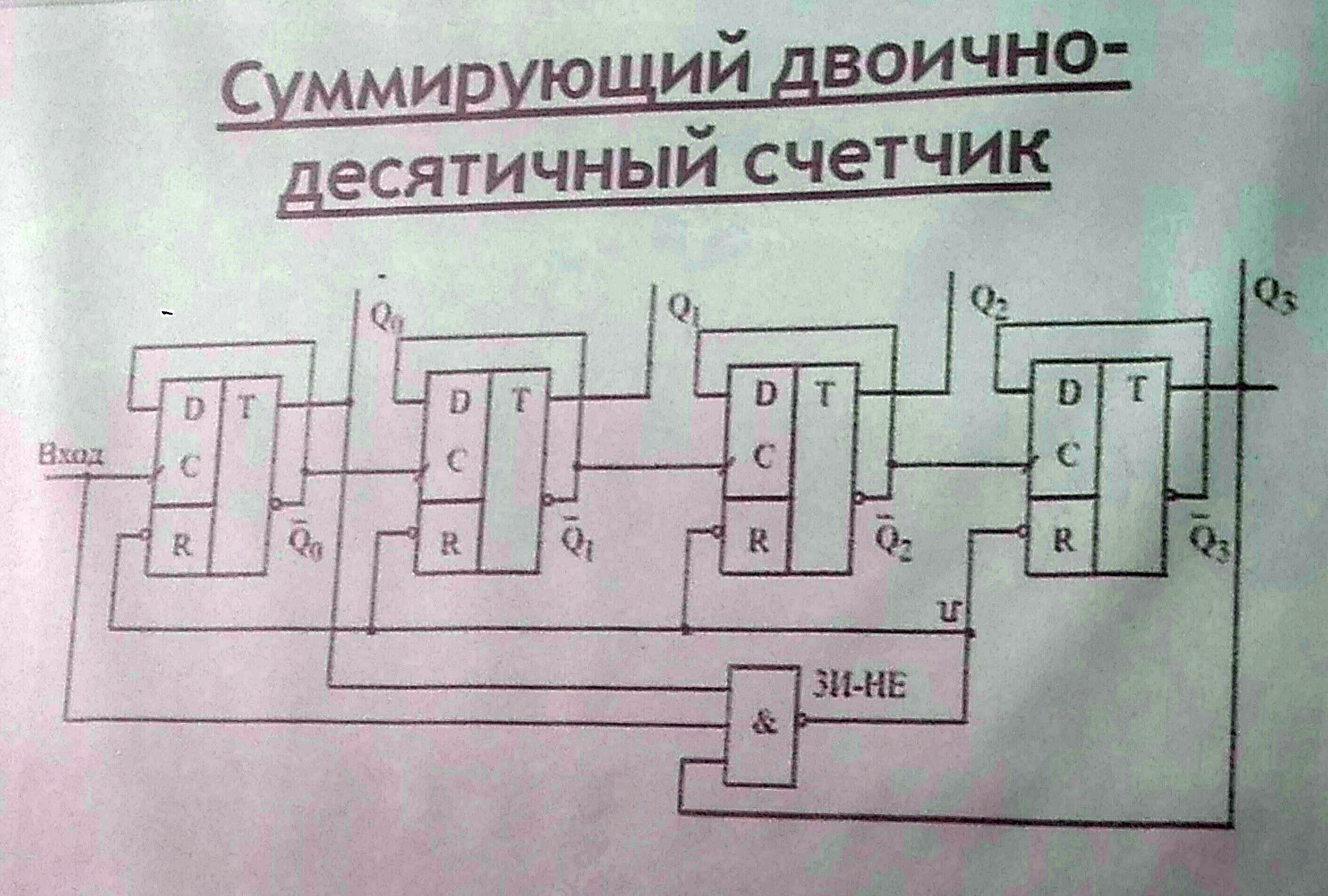

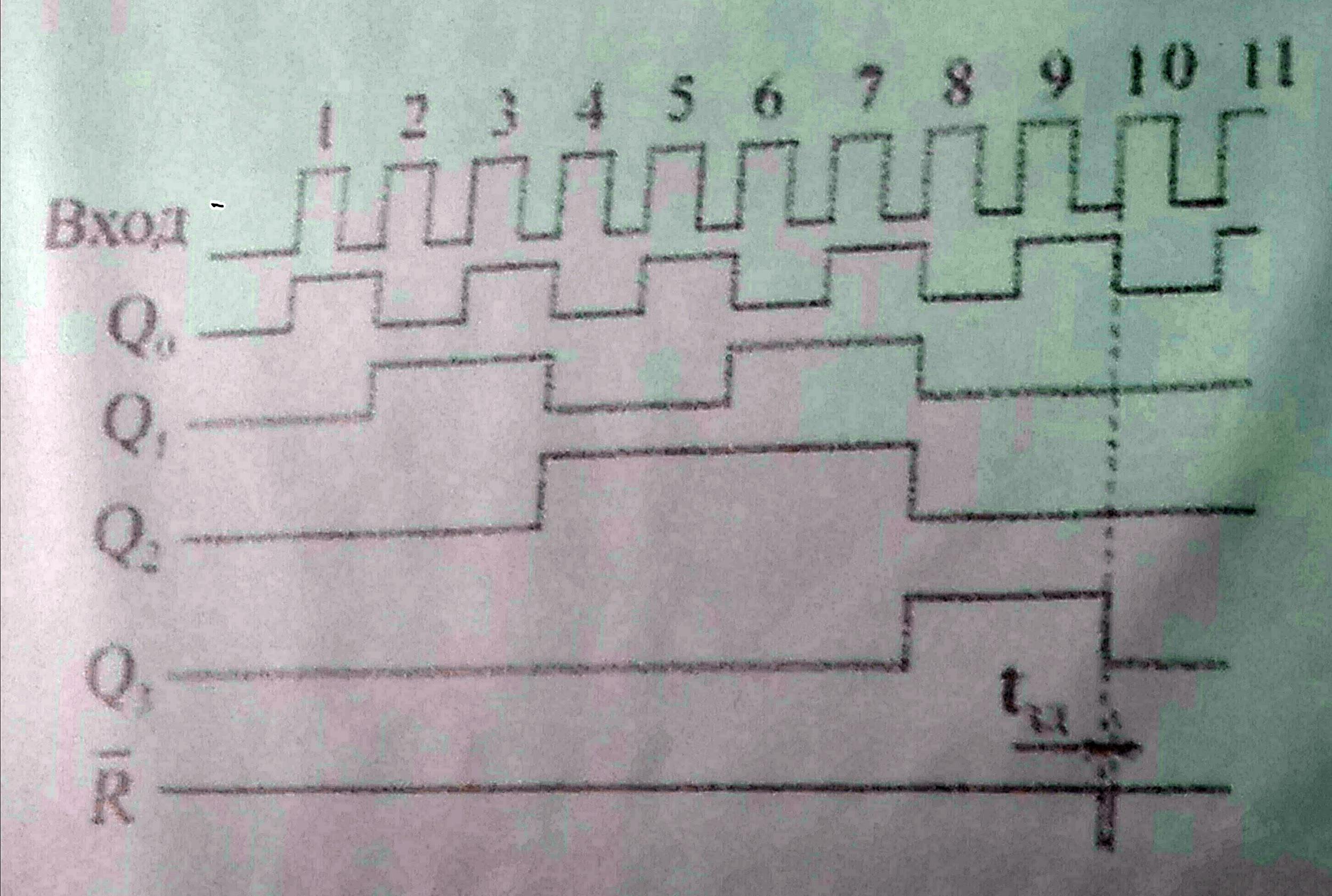

Асинхронный (суммирующий) двоично-десятичный счётчик

Каскадное соединение счетчиков при сквозном переносе

Сведения о счётчиках в интегральном исполнении

Синхронные счётчики семейства ТТЛ

ФДЧ - делитель частоты с фиксированным коэффициентом деления

Арифметико-логическое устройство (АЛУ)

Входы и выходы цифровых микросхем

Счётчик построен на четырёх D-триггерах, следовательно, он может считать от 0 до 15. Но в случае десятичного счётчика нам нужно, чтобы он считал от 0 до 9. На состоянии 10 счётчик должен перейти на новый цикл работы. Для этого в схеме используется 3-входовой элемент И-НЕ. Когда счётчик досчитал до 9 (1001) приходит следующий счётный импульс. На входе первого триггера “1”. На выходе Q0, как следует из состояния 9, “1”. На выходе Q3 - также “1”. Все эти три единицы приходят на вход элемента И-НЕ и, соответственно, на его выходе формируется Q0, который подаётся на инверсный вход сброса R всех триггеров и все триггеры сбрасываются в “0”, то есть имеем на выходе счётчика состояние 0 (0000). Получаем, что счётчик считает от 0 до 9, затем сбрасывается и начинает счёт с начала.

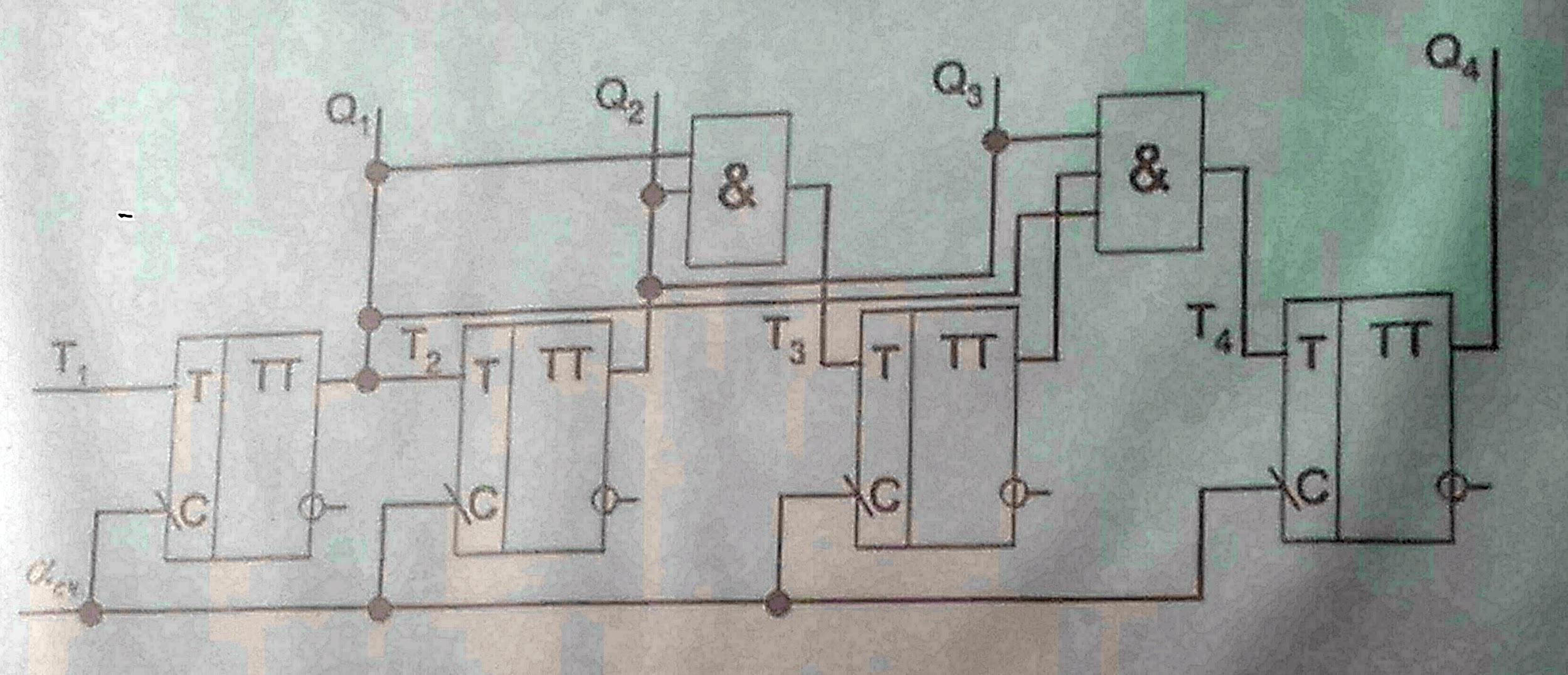

Синхронные счётчики

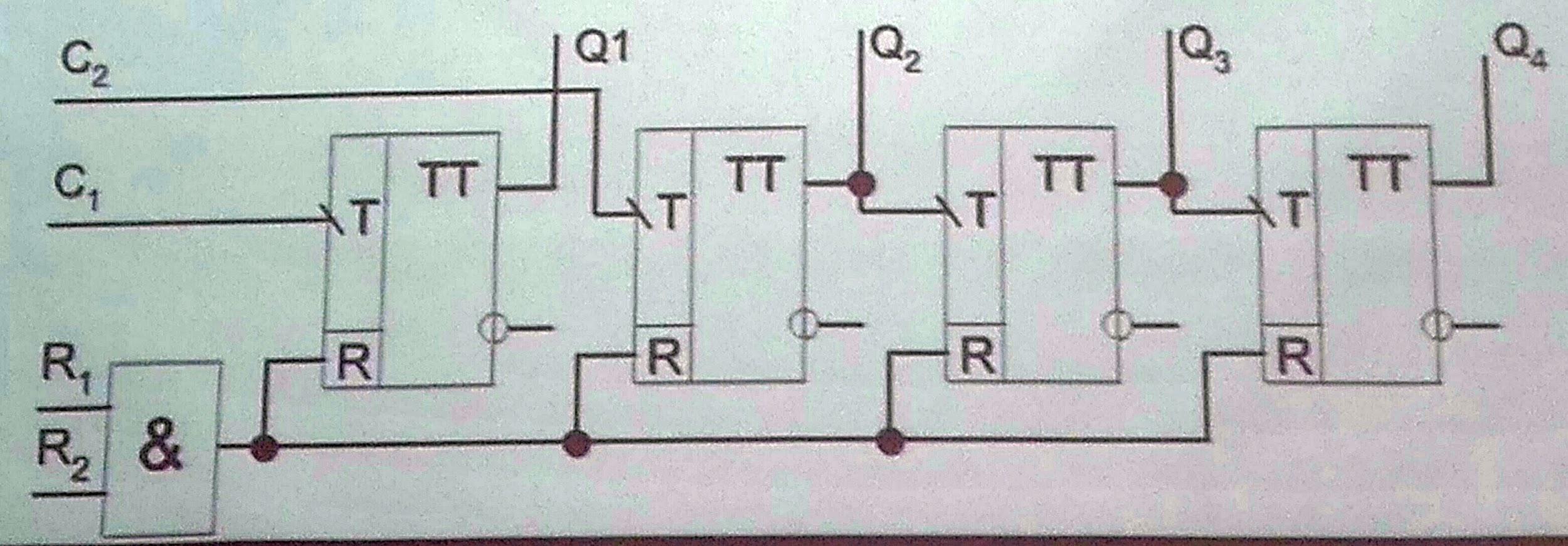

Синхронные счётчики строятся в отличие от асинхронных иначе, так как синхросигнал подается одновременно на все триггеры. В асинхронных синхросигнал подается лишь на 1-ый триггер. Соединение 1-го и 2-го триггера в синхронном счетчике аналогично асинхронному, то есть с выхода предыдущего на вход последующего. Второй и третий триггеры соединяются через элемент И, на который подаются сигналы с выходов предыдущих триггеров, соответственно имеем:

T1 = 1

T2 = Q1 = Q1 T1

T3 = Q1 Q2 = T2 Q2

T4 = Q1 Q2 Q3 = T3 Q3

…

Ti+1 = Ti Qi

Быстродействие синхронных счётчиков значительно выше, чем у асинхронных, так как осуществляется параллельный перенос информации. Но при этом усложняется конструкция и значит меняются аппаратные затраты при реализации счётчика.

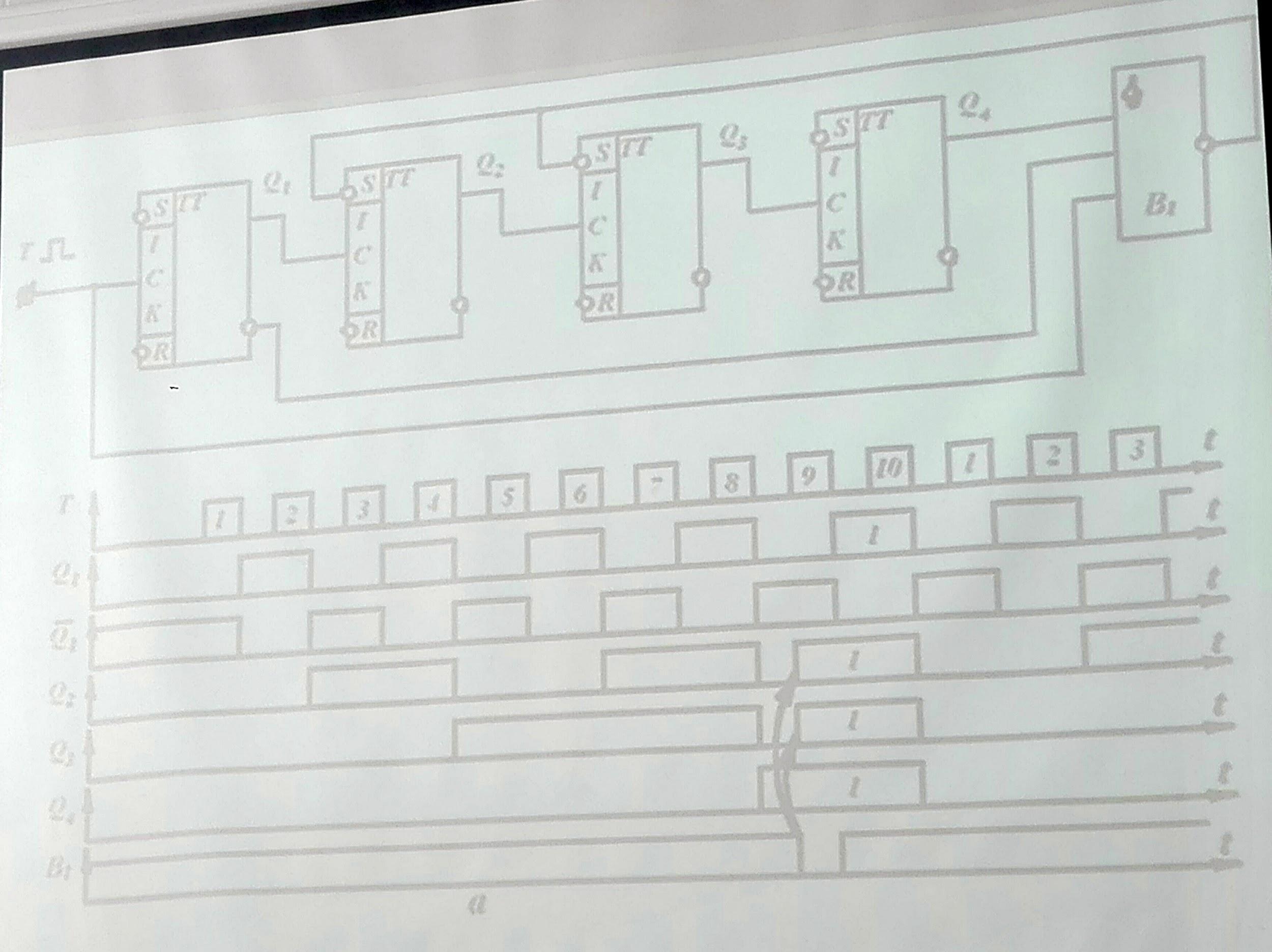

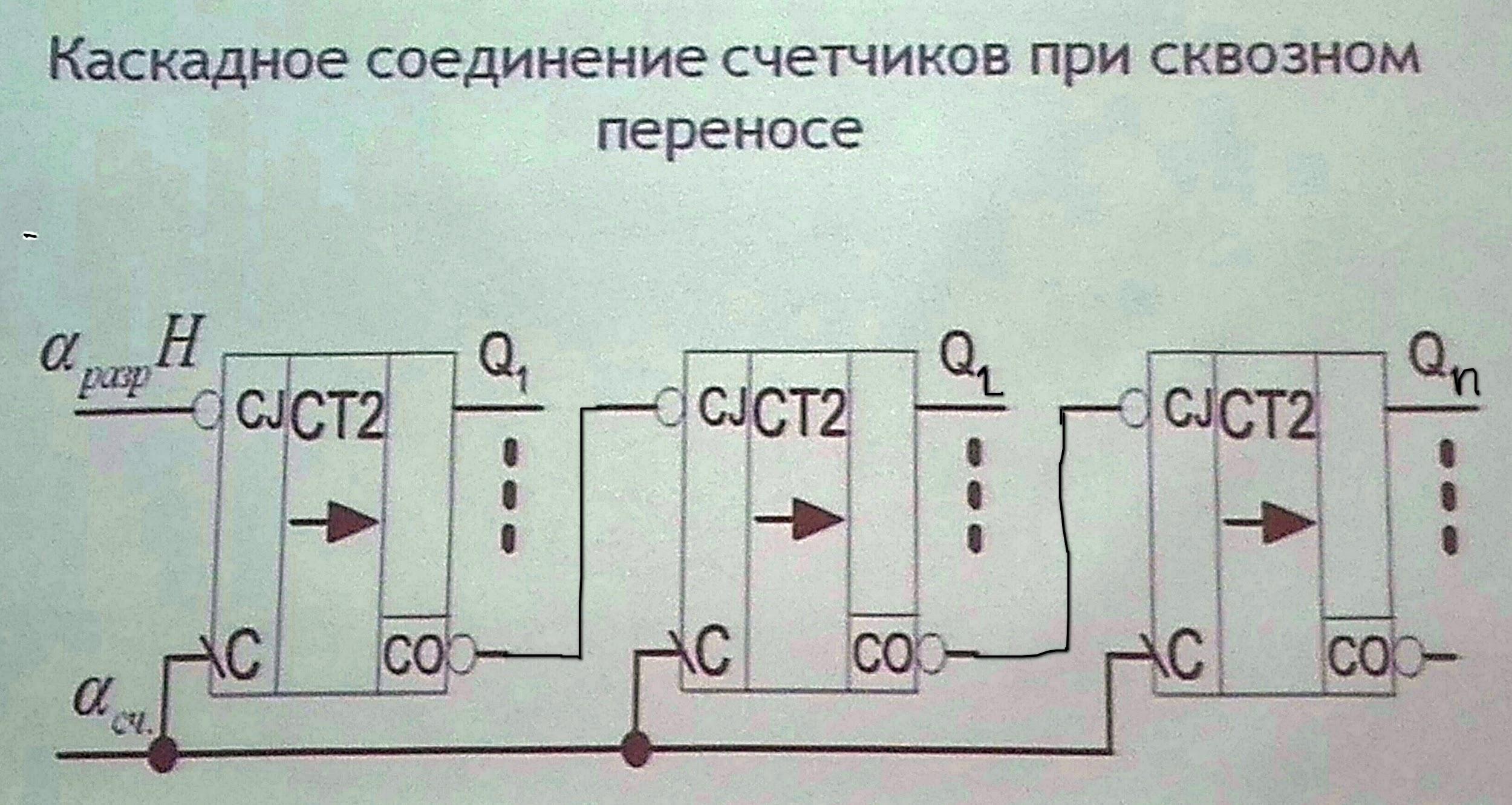

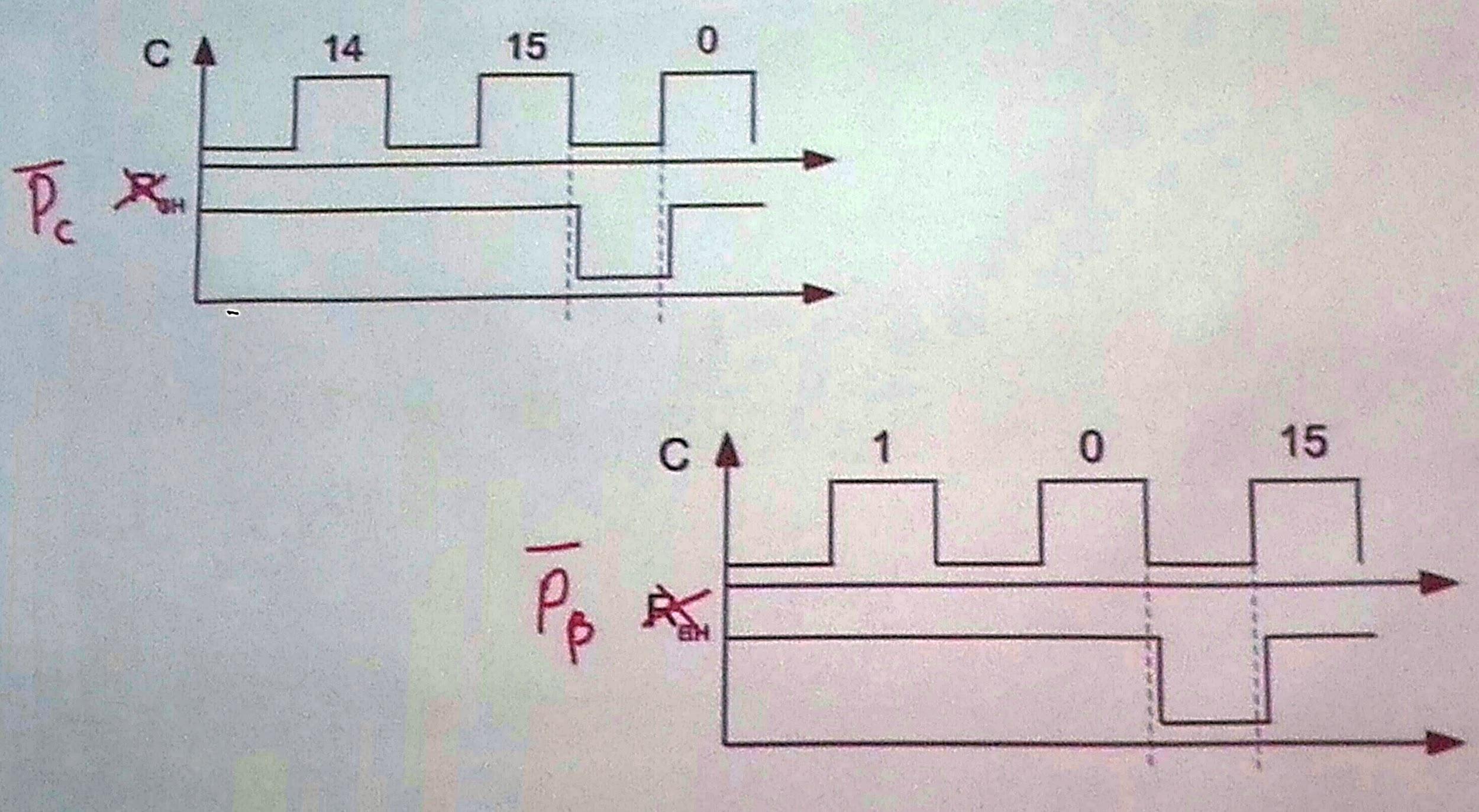

Каскадное соединение счетчиков при сквозном переносе

При каскадном соединении счётчиков перенос осуществляется от младшего разряда к старшему, так когда первый счетчик досчитал до своего максимального значения, на выходе CO-инверсное формируется сигнал переноса который подается на вход разрешения счета CJ-инверсное следующего счетчика и т.д. Перенос информации осуществляется последовательно.

Сведения о счётчиках в интегральном исполнении

Асинхронные счётчики

ИЕ5

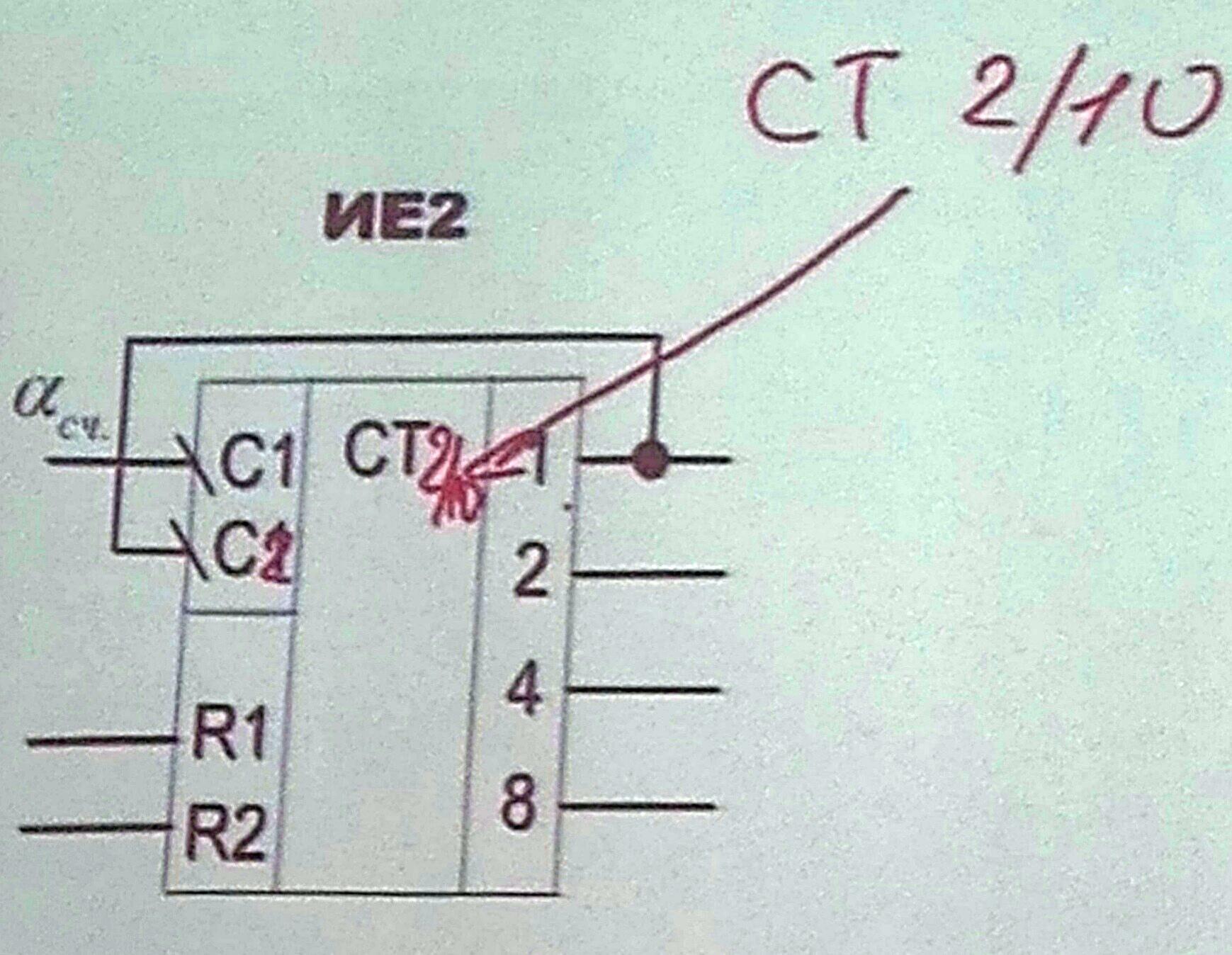

Микросхема ИЕ5 представляет собой два счётчика с разными тактовыми входами C и разными входами сброса R. Первый счётчик реализован на первом триггере и управляется входом C1. Второй счётчик построен на втором, третьем и четвёртом триггерах. И представляет собой трёхразрядный счётчик, управляемый по входу C2. При наличии внешней коммутации: с выхода Q1 на вход C2 … и при подаче счётных импульсов на вход C1 получим четырёхразрядный двоичный счётчик.

Счётчик может использоваться в качестве

делителя частоты, когда первый каскад

осуществляет деление на два (выход 1),

второй каскад осуществляет деление на

2, 4 и 8.

Микросхема ИЕ2 - то же что ИЕ5, но первый каскад осуществляет деление на 2, а второй на 10.

Синхронные счётчики семейства ТТЛ

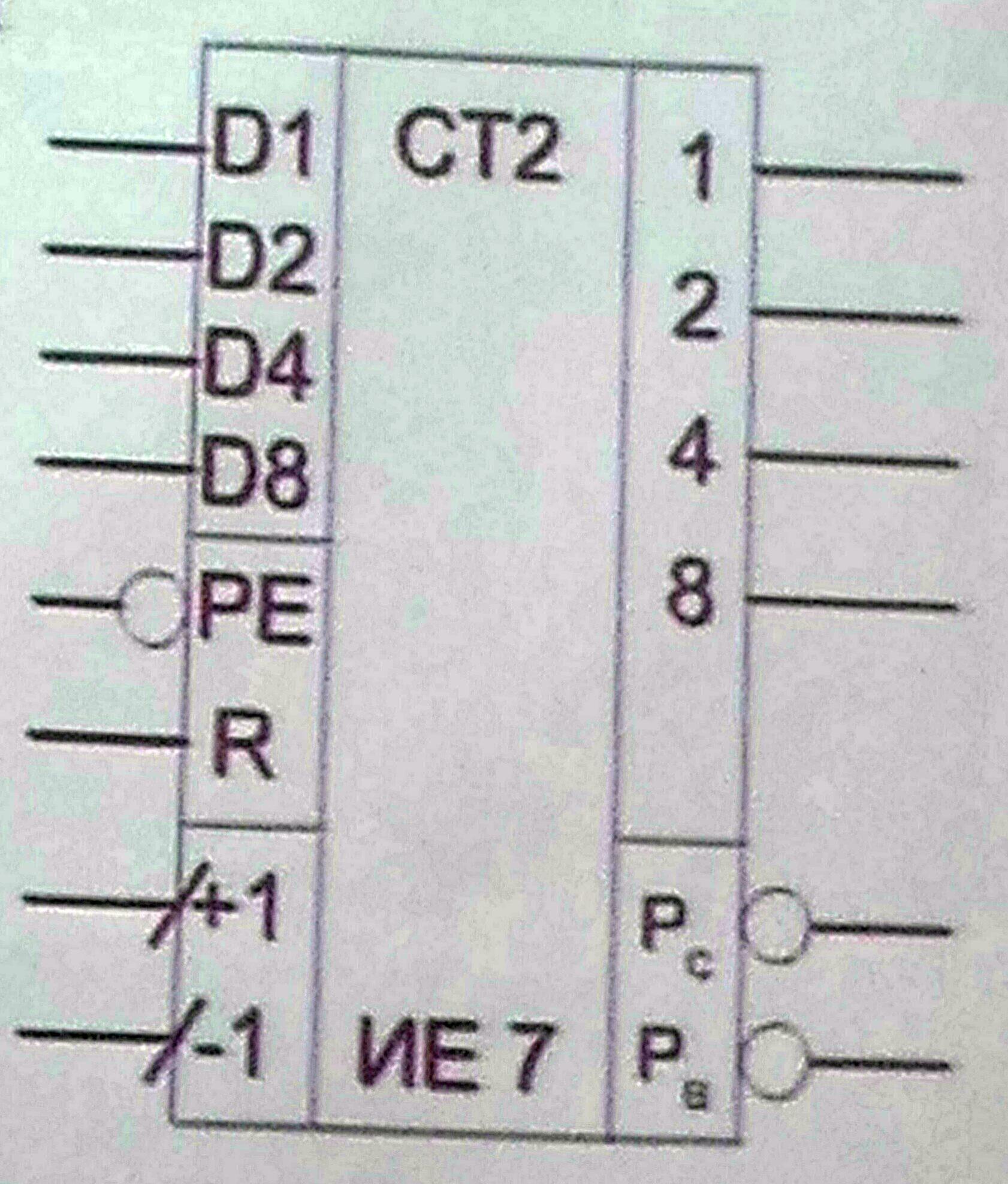

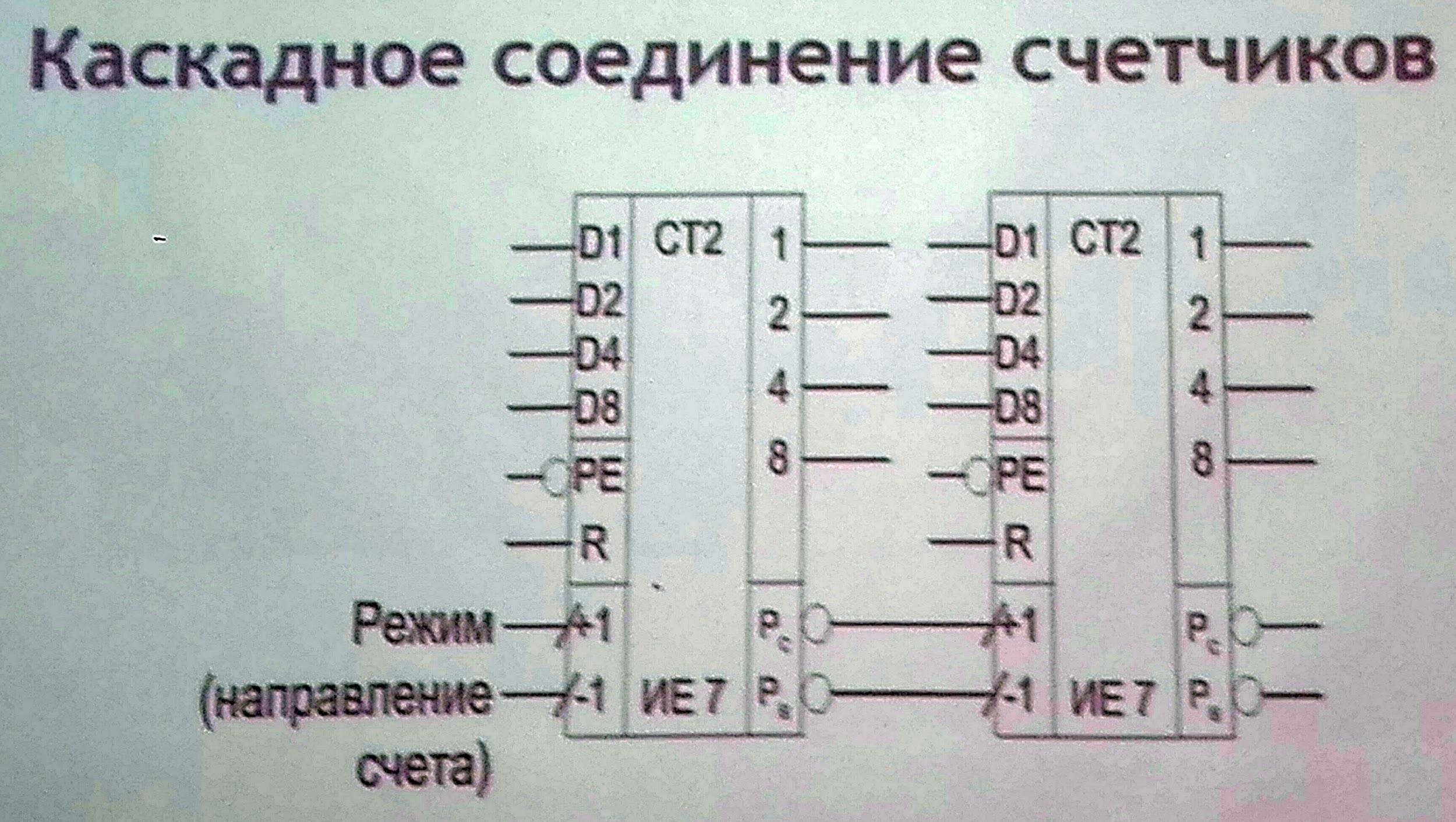

ИЕ7 - двоичный счётчик.

ИЕ6 - двоично-десятичный счётчик.

D1,D2,D4D8 - информационные входы предустановки.

РЕ-инверсное - вход разрешения пред установки

R - вход сброса

+1 - вход разрешения суммирования

-1 - вход разрешения вычитания

1, 2 ,4, 8 - выходы счетчика

Pс-инверсное - выход переноса из старшего разряда.

Pв-инверсное - выход переноса из младшего разряда.

Пусть PE-инверсное равно 0. В этом случае в счётчик записывается информация со входов D1-D8, то есть предустанавливается…

Если на входах 0101, при PE-инверсное равном 0, в счётчик записывается 5 и при PE-инверсном равном 1 и наличии тактовых импульсов на входе +1, счётчик считает 6, 7, 8, 9 и т.д.

На выходе переноса из старшего или младшего разряда на полтакта, формируется сигнал, равный 0, в том случае когда счетчик достигает своего максимального значения.

Для обеспечения каскадного соединения счётчиков, т.е. для увеличения ёмкости счётчиков и количества подсчитываемых импульсов, необходимо соединить выход переноса из старшего разряда Рс-инверсное со входом направления суммирования следующего счётчика (+1) и Рв-инверсное (-1) последующего.

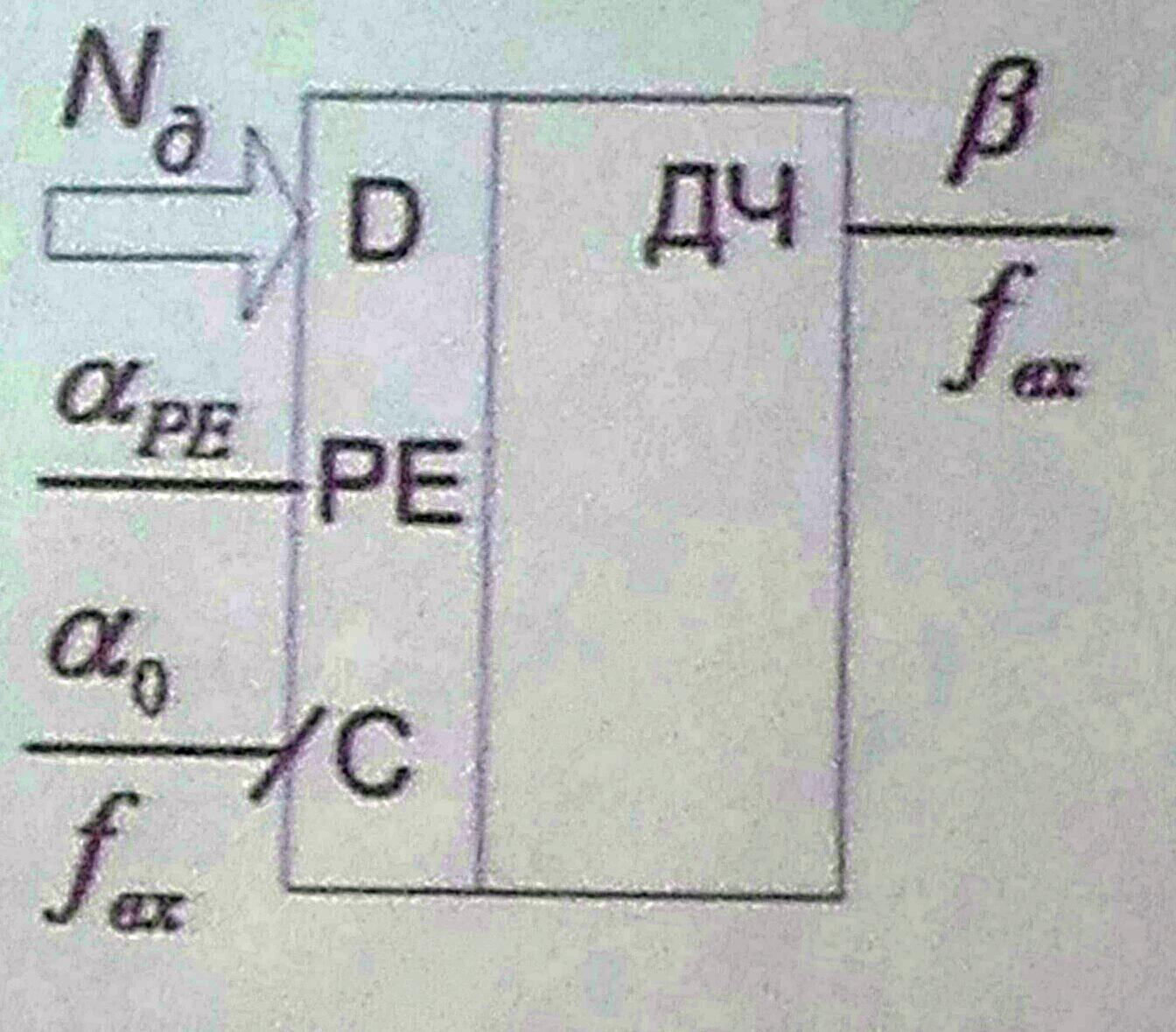

Делители частоты (ДЧ)

Сигнал на выходе делителя частоты

получается делением частоты входного

сигнала на коэффициент деления

(= 2, 4, 8, 16…):

УГО делителя частоты:

ФДЧ - делитель частоты с фиксированным коэффициентом деления

У такого делителя

.

Рассмотрим делитель частоты на счётчике ИЕ-7. Первый выход счётчика осуществляет деление на два. Второй - на четыре. Третий - на восемь. Четвёртый - на шестнадцать. У данного счётчика есть возможность предустановки в начальное состояние, которая осуществляется по входу PE, т.е. счётчик может начать считать не с нуля, а с некоторого предустановленного значения.

Цифровые функциональные узлы

Арифметические микросхемы ТТЛ

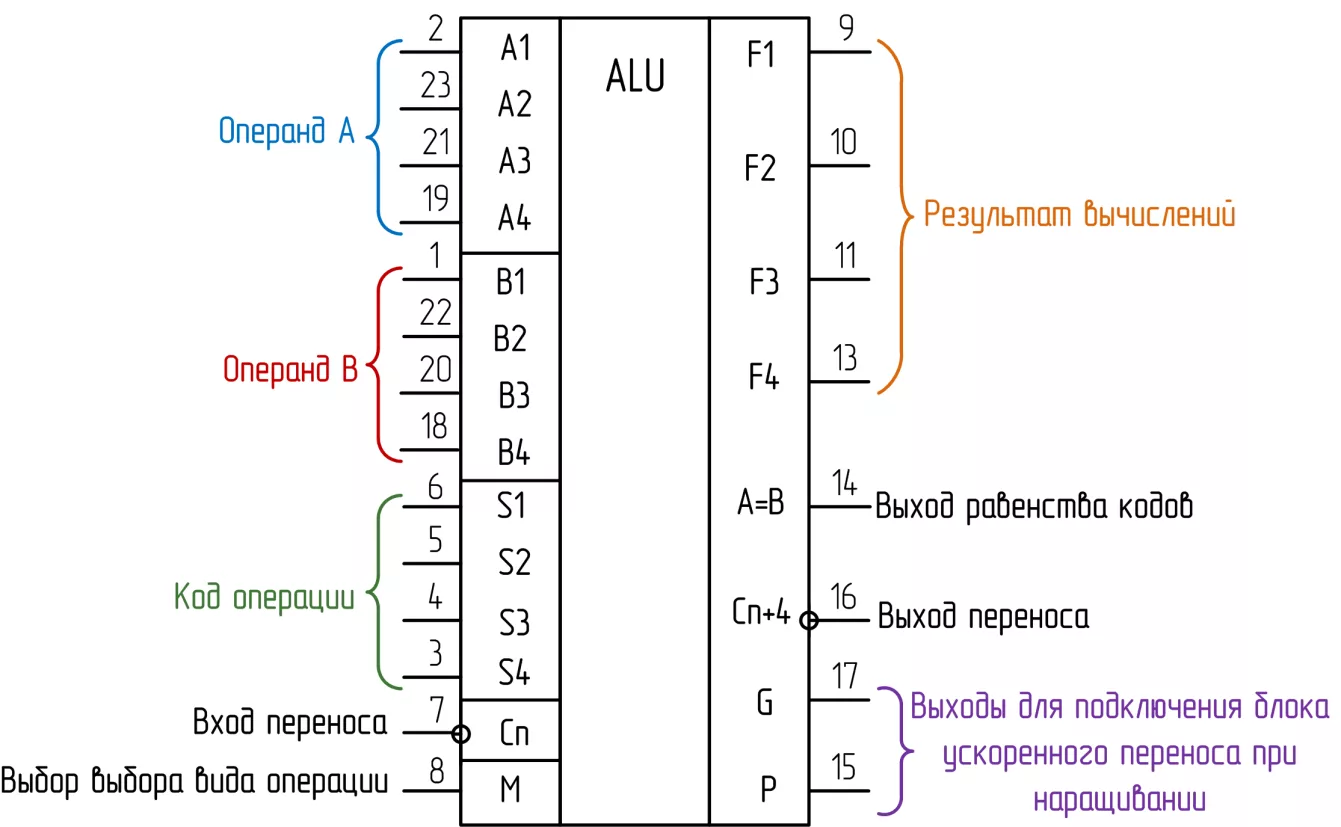

Арифметико-логическое устройство (АЛУ)

1.

Микросхема К155ИП3 - АЛУ

Это 4-разрядное скоростное АЛУ, выполняет 16 логических либо 16 арифметических операций. Для увеличения быстродействия в микросхеме имеется внутренняя схема ускорения переносов. Выходы корпуса на 24 вывода.

A1 - A4, B1 - B4 - входы операндов A и B.

Сn-инверсное - инверсный вход переноса в младший разряд.

S0 - S3 - входы выбора операции.

M:

M=0 - микросхема выполняет арифметические операции,

M=1 - микросхема выполняет логические операции.

F1 - F4 - выходы.

Сn+4-инверсное - инверсный выход переноса из старшего разряда.

G - выход генерации переноса.

P - выход распространение переноса.

K - выход компаратора с открытым коллектором.

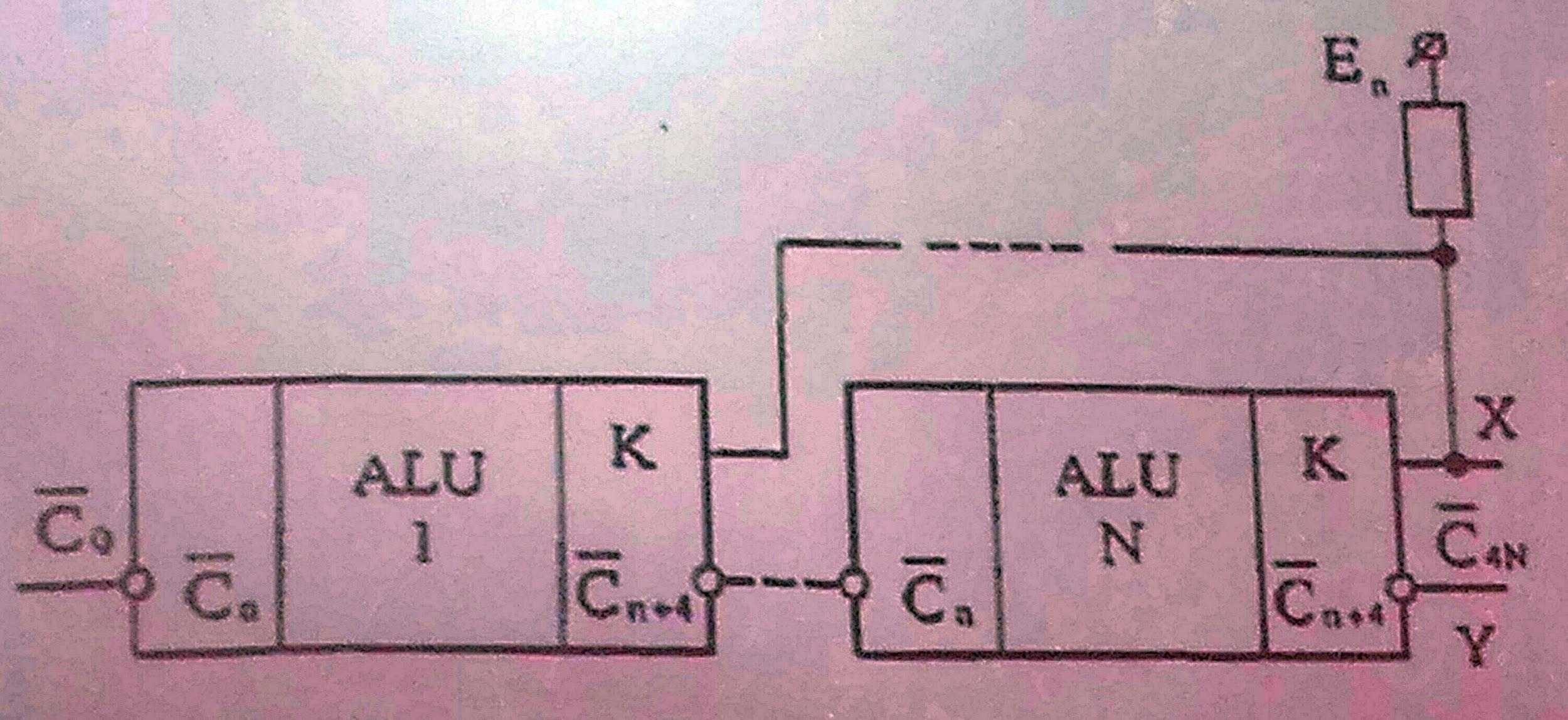

Для увеличения разрядности АЛУ используют их каскадное соединение:

2. Схема ускорения переносов К155ИП4

Используется для увеличения быстродействия АЛУ и обслуживает 4 корпуса АЛУ. Незаменима при их каскадном соединении, так как в случае 16-разрядного АЛУ значительно уменьшается быстродействие такого устройства.

Cn-инверсное - вход приёма сигнала переноса.

G0 - G3 - вход сигналов генерации переноса.

P0 - P3 - вход сигналов распространения переноса.

Cn+x, Cn+y, Cn+z - сигналы переносов.

P - выход распространения переносов.

G - выход генерации переносов.

Рассмотрим соединение и применение К155ИП4 для 16-ти разрядного АЛУ

3. Микросхемы контроля чётности К155ИП2

Используется для контроля правильности высокоскоростных передач по линиям связи определяется проверка четности (нечетности) числа единиц передаваемого кода. К155ИП2 представляет собой восьмиразрядный модуль и имеет 2 входа управления:

-

EE (even enable) - чётный вход управления,

-

OE (odd enable) - нечётный вход управления.

I0 - I7 - информационные входы, для которых осуществляется проверка чётности и нечётности.

2) ЕЕ - вход управления четный, ОЕ - вход управления нечетный ,

-

выходы микросхемы, на которых отображается

число единиц.

Серии цифровых микросхем

Количество выпускаемых микросхем на современном рынке огромно. Для их классификации используется их обозначение, при этом российское обозначение отличается от импортного.

Российское обозначение: КХХХ ХХХ.

KXXX - серия микросхемы,

XXX - название МС.

Обозначение фирмы Texas Instruments: SN 74 LS XX XXX NT.

Температурный диапазон (семейство МС):

-

74 - коммерческие МС. Температура окружающей среды для биполярных МС - от 0 до 70, для КМОП - от -40 до +85.

-

54 - МС военного назначения. От -55 до +125 ℃.

Код серии:

-

Отсутствует - стандартная ТТЛ серия

-

Если LS, то это будет маломощная ТТЛШ ( с диодами Шоттки)

-

S - ТТЛШ

-

ALS - улучшенная ТТЛШ

-

HC - высокоскоростная КМОП

-

AC - улучшенная КМОП

Идентификатор специального типа - может отсутствовать.

Код типа корпуса (может отсутствовать):

N - пластмассовый,

J - керамический,

T - плоский металлический.

Каждая микросхема преобразует тем или иным способом последовательность входных сигналов в последовательность выходных сигналов.

Все цифровые микросхемы работают с логическими сигналами, имеющими 2 разрешенных уровня напряжения. Один сигнал - уровень логической единицы (положительная логика), ноль - логический ноль. И наоборот: единица - уровень логического нуля, а ноль - единицы (отрицательная логика).

Сложные логические элементы

К155ЛР1

В состав микросхемы входят два двухвходовых элемента И, объединённых между собой по ИЛИ и проинвентированных.

К155ЛР4

Триггеры Шмитта

Представляют собой специфические логические элементы, специально рассчитанные на работу со входными аналоговыми сигналами. Предназначены для преобразования входных аналоговых сигналов в выходные цифровые.

При прохождении сигнала по линиям связи его фронты становятся пологими вместо прямоугольных и сигналы искажаются шумами и помехами. Для восстановления формы сигнала и избавления от шумов используют триггеры Шмитта.

Кроме того, они позволяют избавиться от дребезга контактов.

Стандартные микросхемы триггеров Шмитта:

-

ТЛ2

-

ТЛ3

-

ТЛ1

Входы и выходы цифровых микросхем

Вход рассматривается как бесконечно большое сопротивление, никак не влияющее на подключенные к нему выходы. Особенным случаем является висящий вход, когда на него не подаётся никакой сигнал и не подано питание. В этом случае микросхема может работать нестабильно, либо неправильно. Поэтому рекомендуется подключать неиспользуемые входы к источнику питания в случае микросхем ТТЛ, подключение производится через ограничительный резистор.