ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 13.05.2019

Просмотров: 691

Скачиваний: 6

СОДЕРЖАНИЕ

Двухступенчатый синхронный RS-триггер

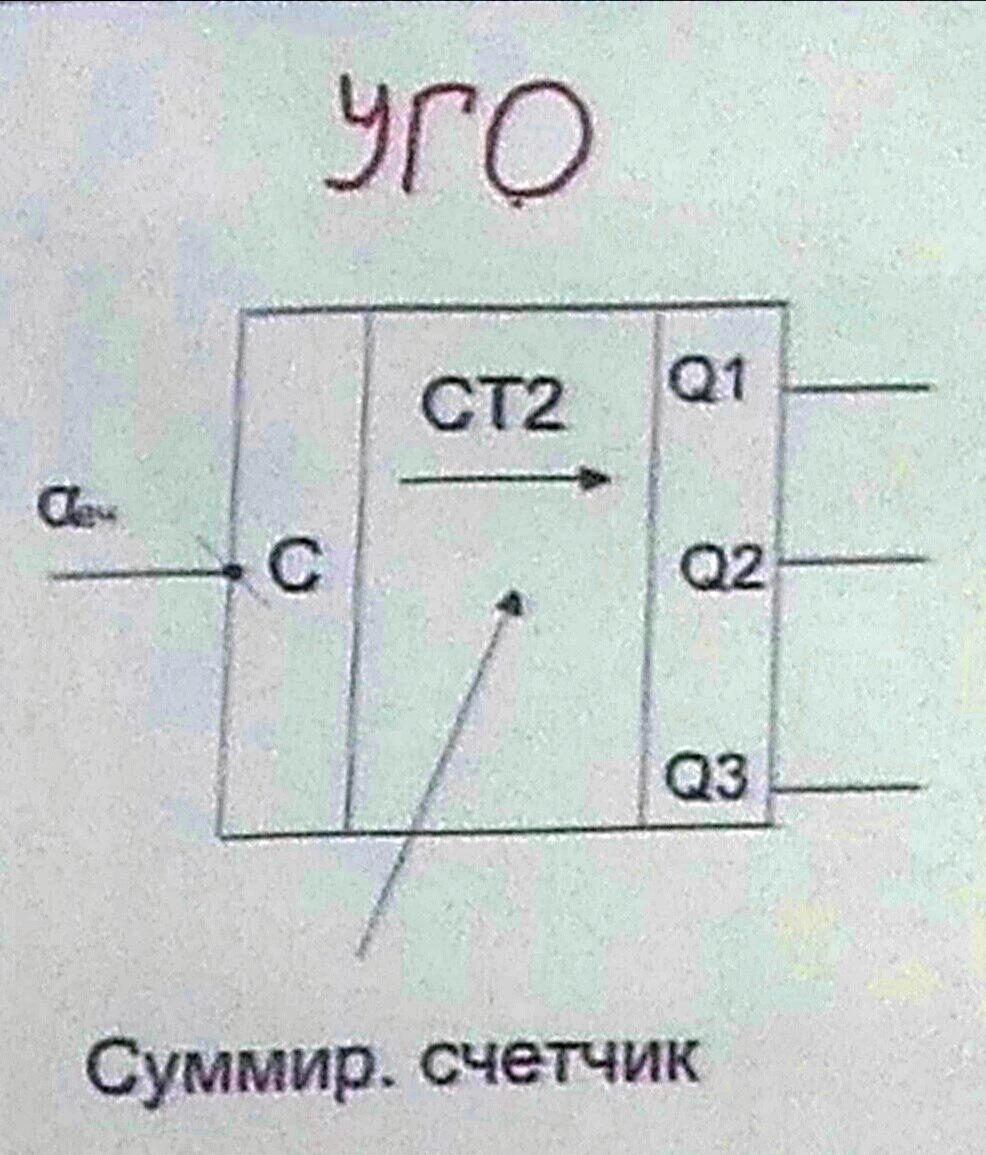

Асинхронный (суммирующий) двоично-десятичный счётчик

Каскадное соединение счетчиков при сквозном переносе

Сведения о счётчиках в интегральном исполнении

Синхронные счётчики семейства ТТЛ

ФДЧ - делитель частоты с фиксированным коэффициентом деления

Арифметико-логическое устройство (АЛУ)

Входы и выходы цифровых микросхем

-

I. Представление чисел в цифровых устройствах (ЦУ)

-

Системы счисления (СС)

-

Система счисления — это совокупность правил записи чисел цифровыми знаками

Системы счисления:

1. Непозиционные

* римская система

2. Позиционные (значение цифры определяется её положением (позицией) в записи числа)

* десятичная

* двоичная

* восьмеричная

* шестнадцатеричная

-

Кодирование

Кодирование — представление чисел в виде, удобном для технической реализации.

Виды кодов:

1. Взвешенные коды

* двоичный код — ДК

* двоично-десятичный код — ДДК

2. Невзвешенные коды

*код Грея

-

Основы синтеза логических устройств

Логические устройства бывают двух видов:

1. Комбинационные схемы (И, ИЛИ, НЕ)

2. Конечные автоматы

Комбинационные схемы не обладают памятью.

Конечные автоматы памятью обладают, т. е. его последующее состояние зависит от предыдущего.

Синтез логических устройств выполняется с использованием методов минимизации, в частности минимизации логической функции методом Вейча-Карно, в результате которого мы получаем минимальные СДНФ или СКНФ, которую в дальнейшем удобно реализовать в заданном базисе. Например, в базисе И-НЕ или ИЛИ-НЕ.

-

Триггеры

-

Классификация триггеров:

-

1. В зависимости от выполняемой функции

*RS

*JK

*D

*T-триггеры

2. В зависимости от наличия управляющего сигнала:

*асинхронные

*синхронные

-

Асинхронный RS-триггер с прямыми информационными входами

|

S |

R |

Q |

|

|

1 |

0 |

1 |

Установка «1» |

|

0 |

1 |

0 |

Установка «0» |

|

0 |

0 |

Qt |

Режим хранения |

|

1 |

1 |

- |

Запрещённая комбинация |

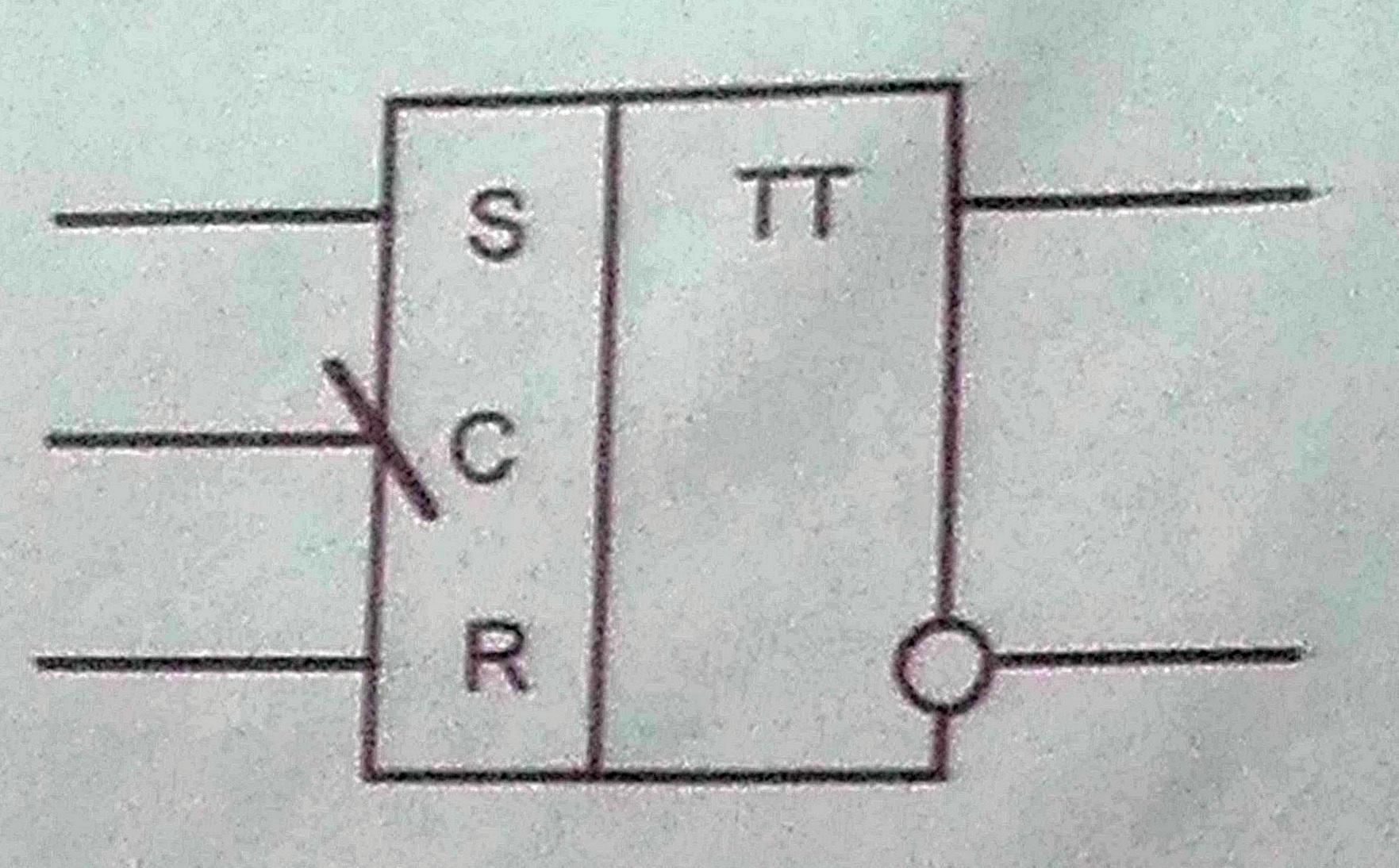

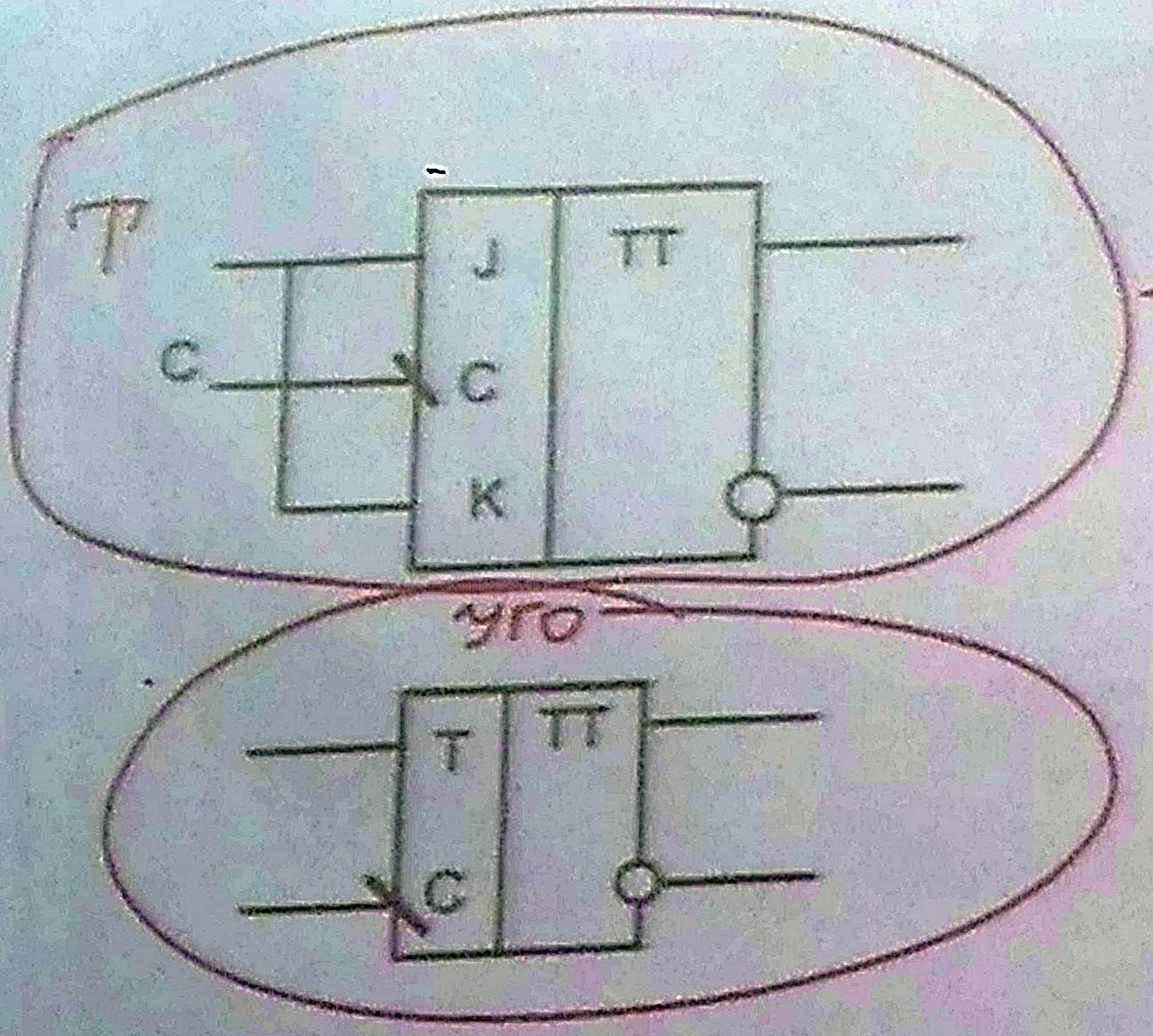

Условно-графическое обозначение (УГО)

“T” - одноступенчатый («TT» - многоступенчатый)

S, R – информационные входы

Q, !Q – выходы

Структурная схема триггера

1.

S=1, R=0

При подаче единицы на вход S вне зависимости от сигнала на втором входе логического элемента в соответствии с таблицей функционирования элемента ИЛИ-НЕ, первый ЛЭ (логический элемент) переключится в «0». Этот «0» по цепи обратной связи поступает на первый вход второго ЛЭ, на втором входе данного логического элемента присутствует «0». Комбинации двух «0» на входе дают единицу на выходе второго ЛЭ, т. е. на выходе всего триггера, таким образом триггер устанавливается в «1».

2. S=0, R=1

На

R - “1” → на выходе DD2 - “0”. По обратной

связи «0» на входе DD1, на входе S - “0”,

тогда на выходе DD1 - “1”, т. е. триггер

переключился в «0».

3. S=0, R=0 – режим хранения

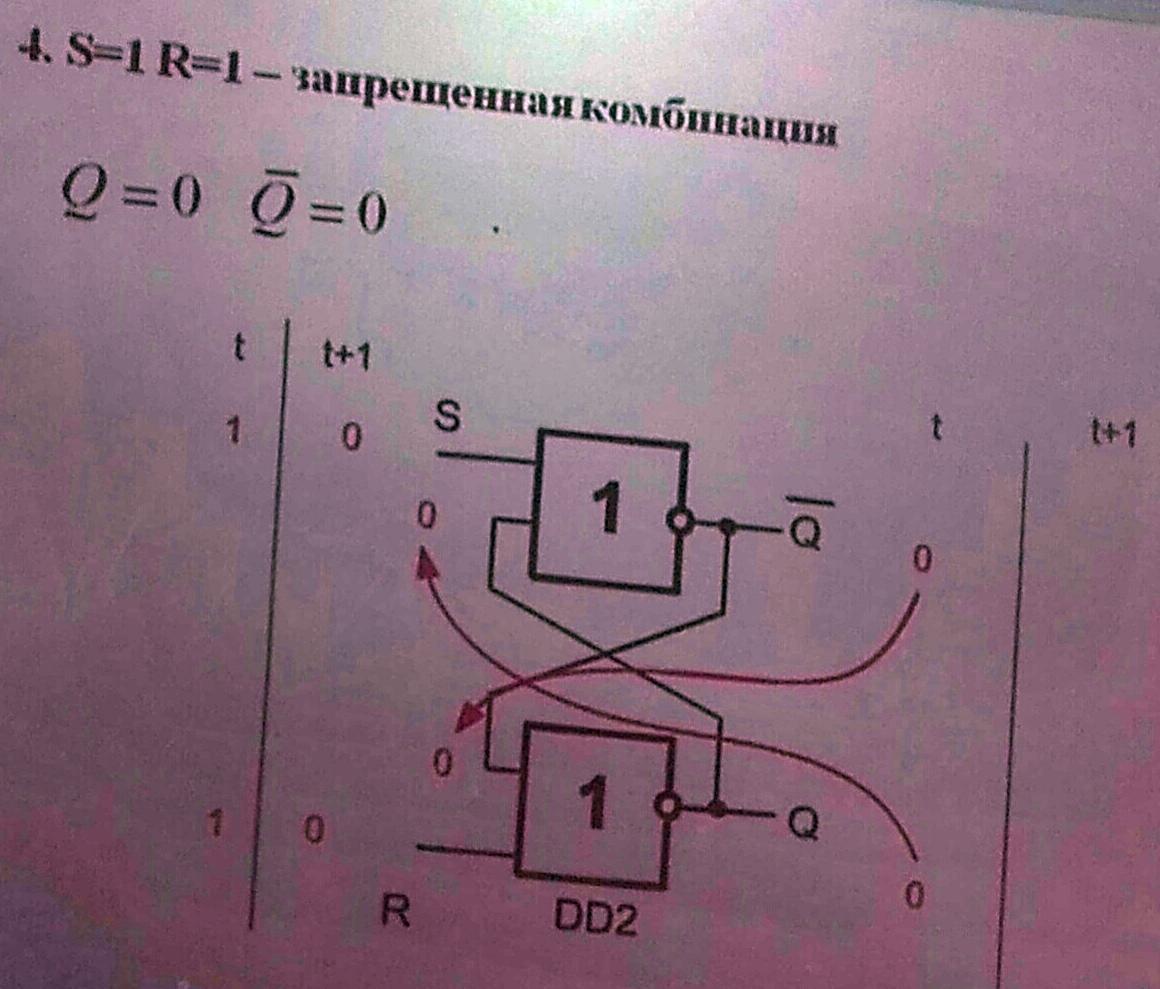

4.

S=1, R=1 – запрещённая комбинация

Пусть в момент времени t на входы S и R подаются «1», тогда на выходах Q и !Q формируются два «0». Эти «0» нарушают правило инверсности выходов триггера, но это не самое страшное. Пусть в момент времени t+1 S = 0, R = 0, тогда «0» с выходов триггера подаются на его входы по обратной связи и получается, что на всех четырёх входах ЛЭ присутствуют «0».

Следующее состояние триггера будет зависеть от того, какой из ЛЭ переключится первым. Если первым переключится DD1, тогда триггер перейдёт в «0». Если первым переключится DD2, тогда триггер перейдёт в «1».

Таким образом, запрещённая комбинация отрицательна тем что состояние триггера в следующий момент времени после запрещённой комбинации будет либо «0», либо «1» с вероятностью 50%.

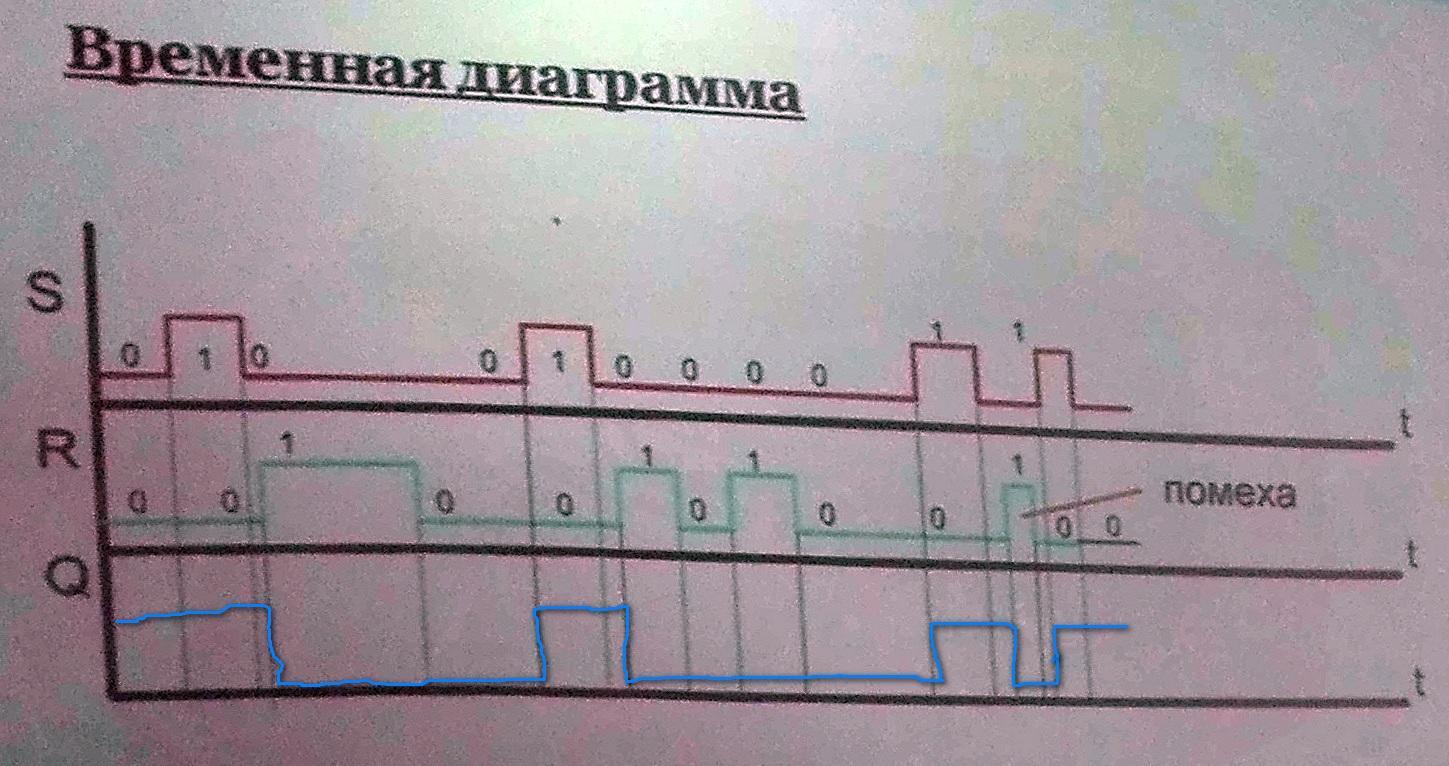

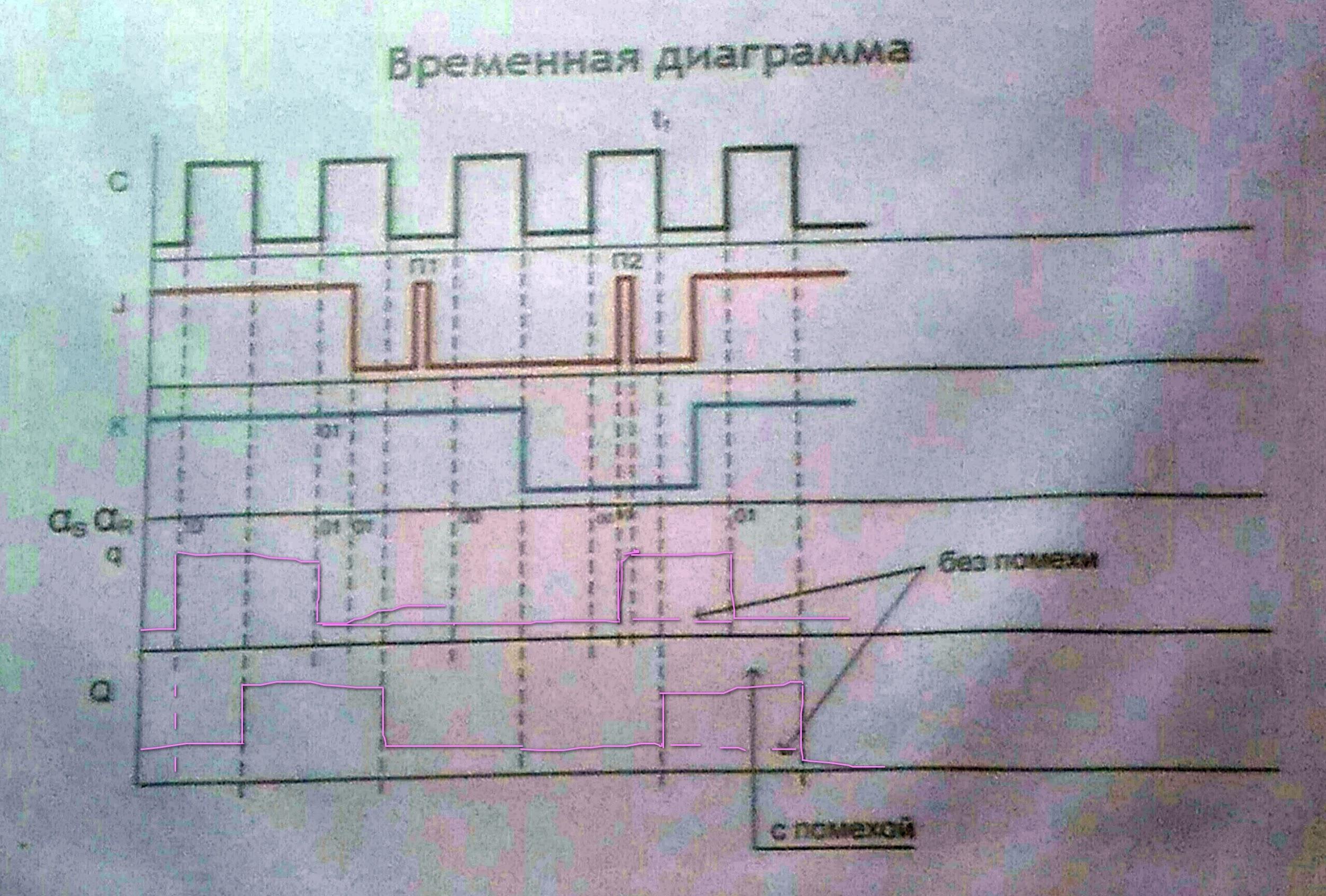

Временная диаграмма:

S R Q

1 0 “1»

0 1 «0»

0 0 хранение

1 1 запрещённая комбинация

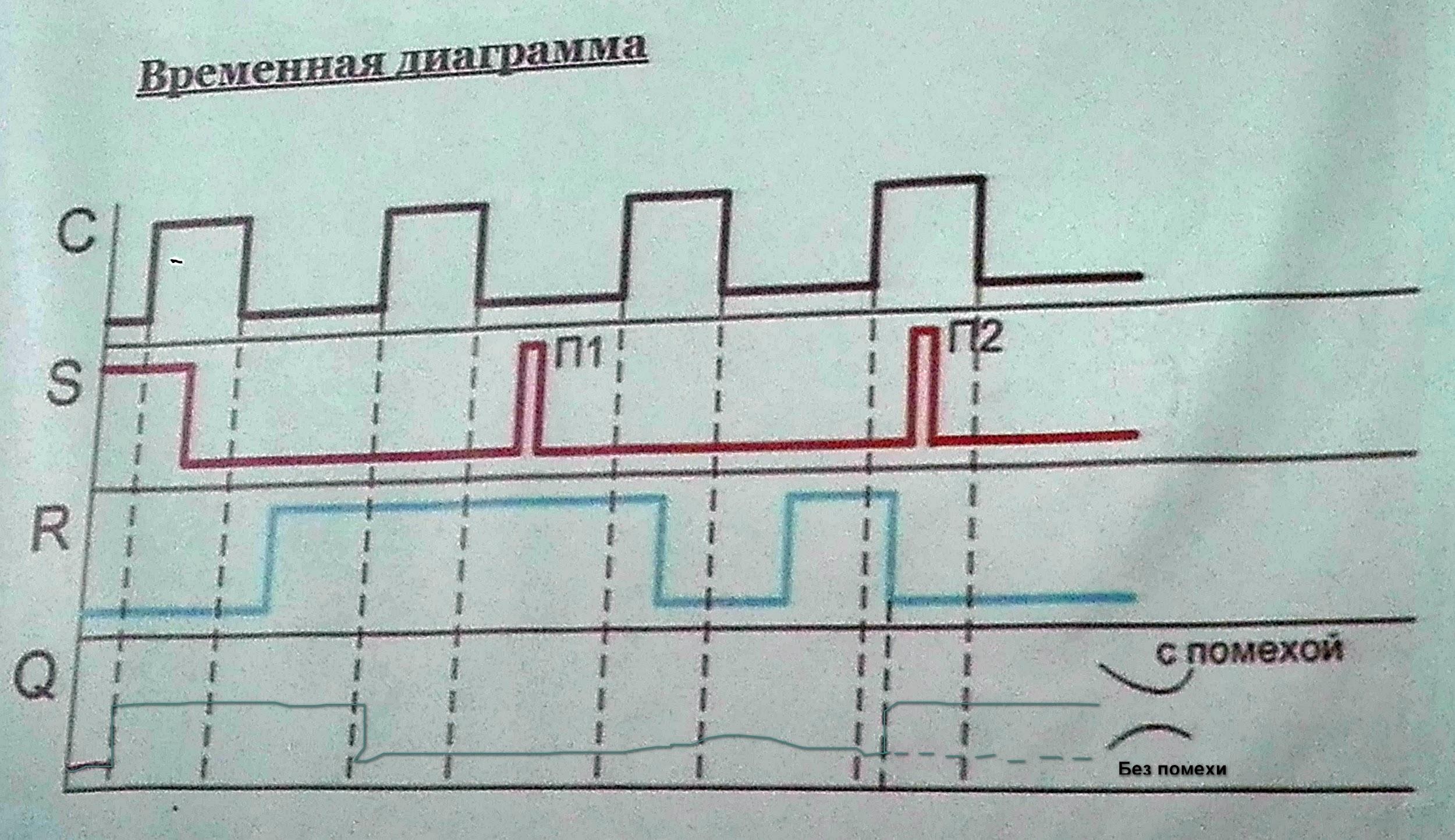

Как видно из временной диаграммы, появление помехи на входе R приводит к мгновенному переключению триггера, таким образом асинхронный RS-триггер обладает низкой помехозащищённостью.

-

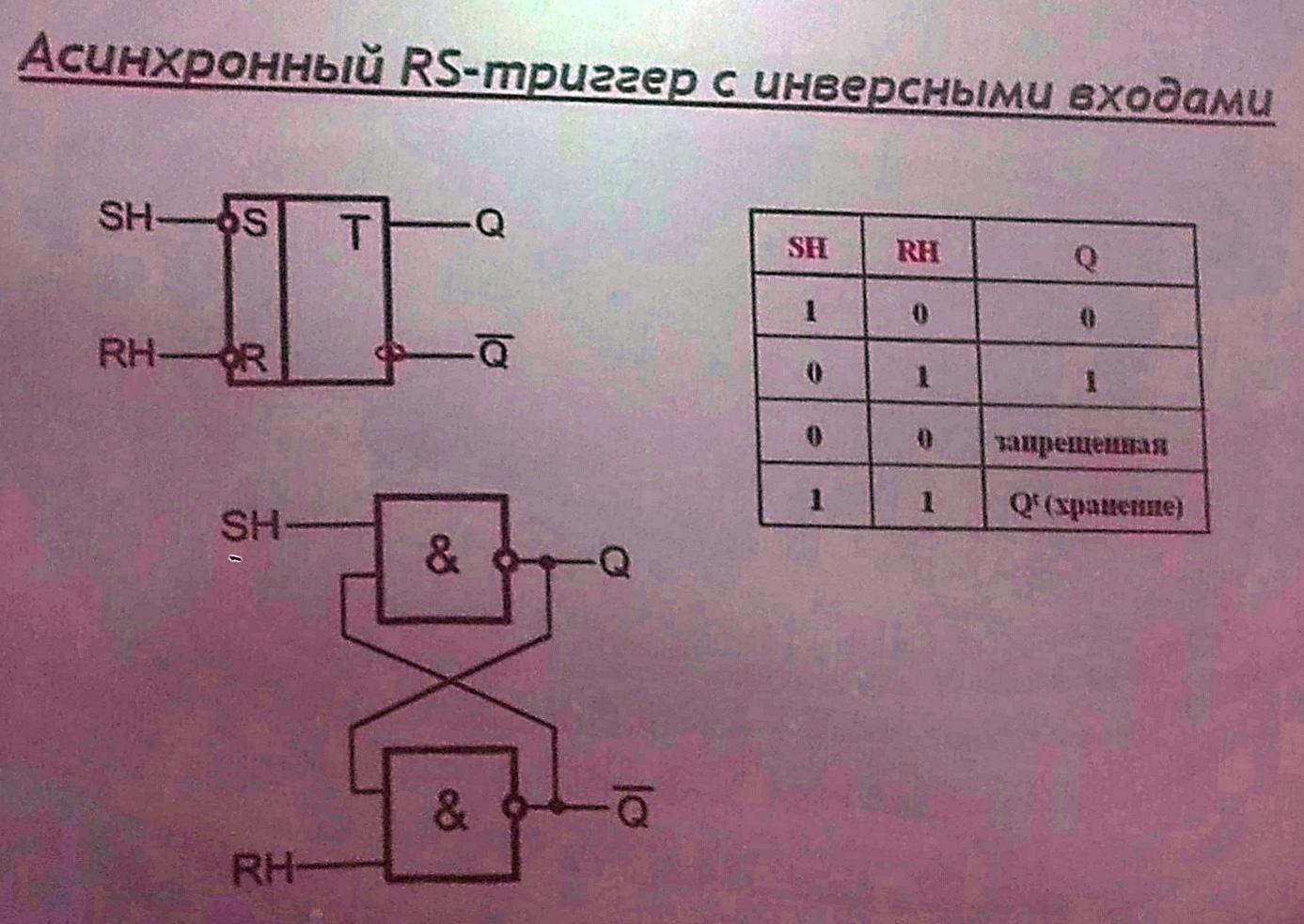

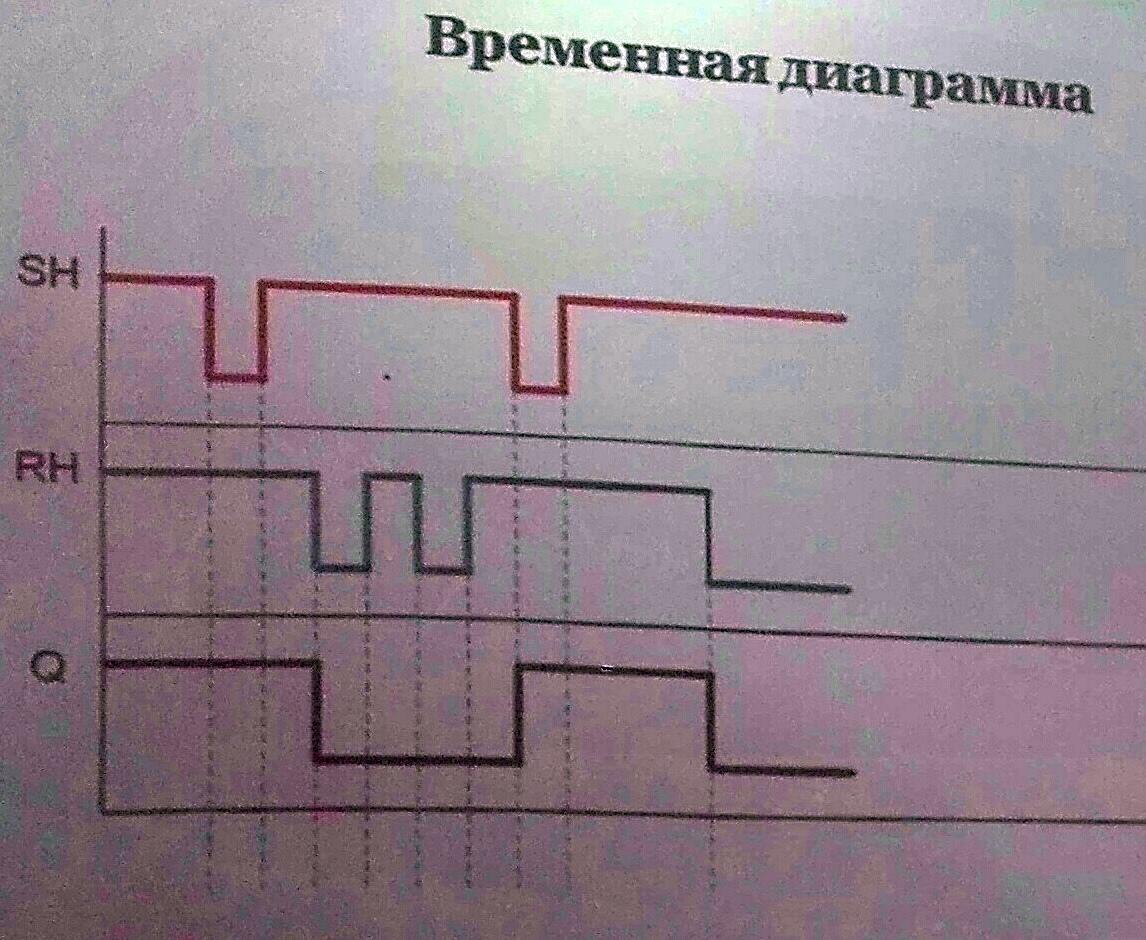

Асинхронный RS-триггер с инверсными входами

-

Синхронный одноступенчатый RS-триггер

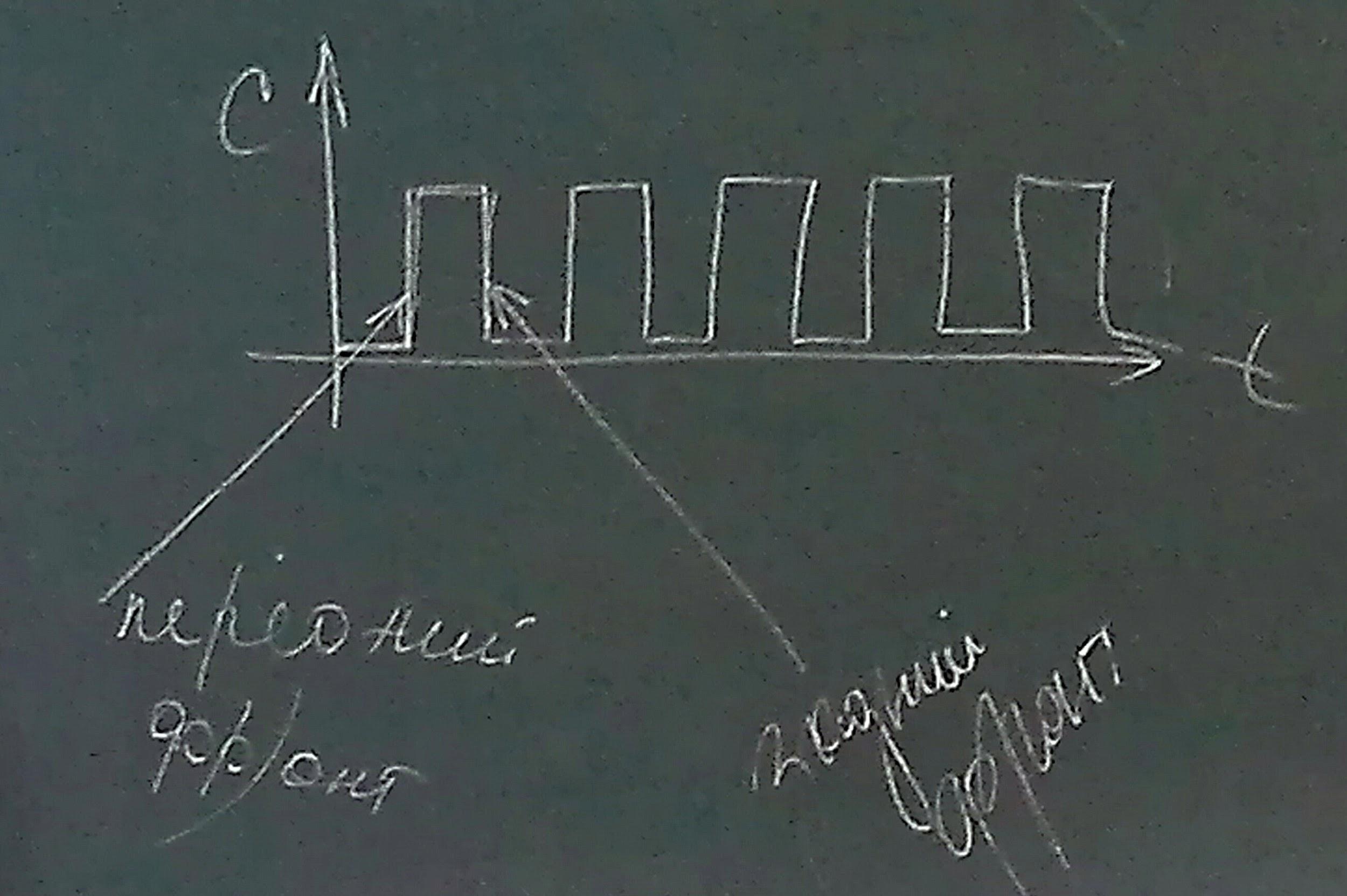

Синхронный триггер отличается наличием ещё одного входа — входа синхронизации (тактового входа) — C. Последовательность синхроимпульсов выглядит следующим образом:

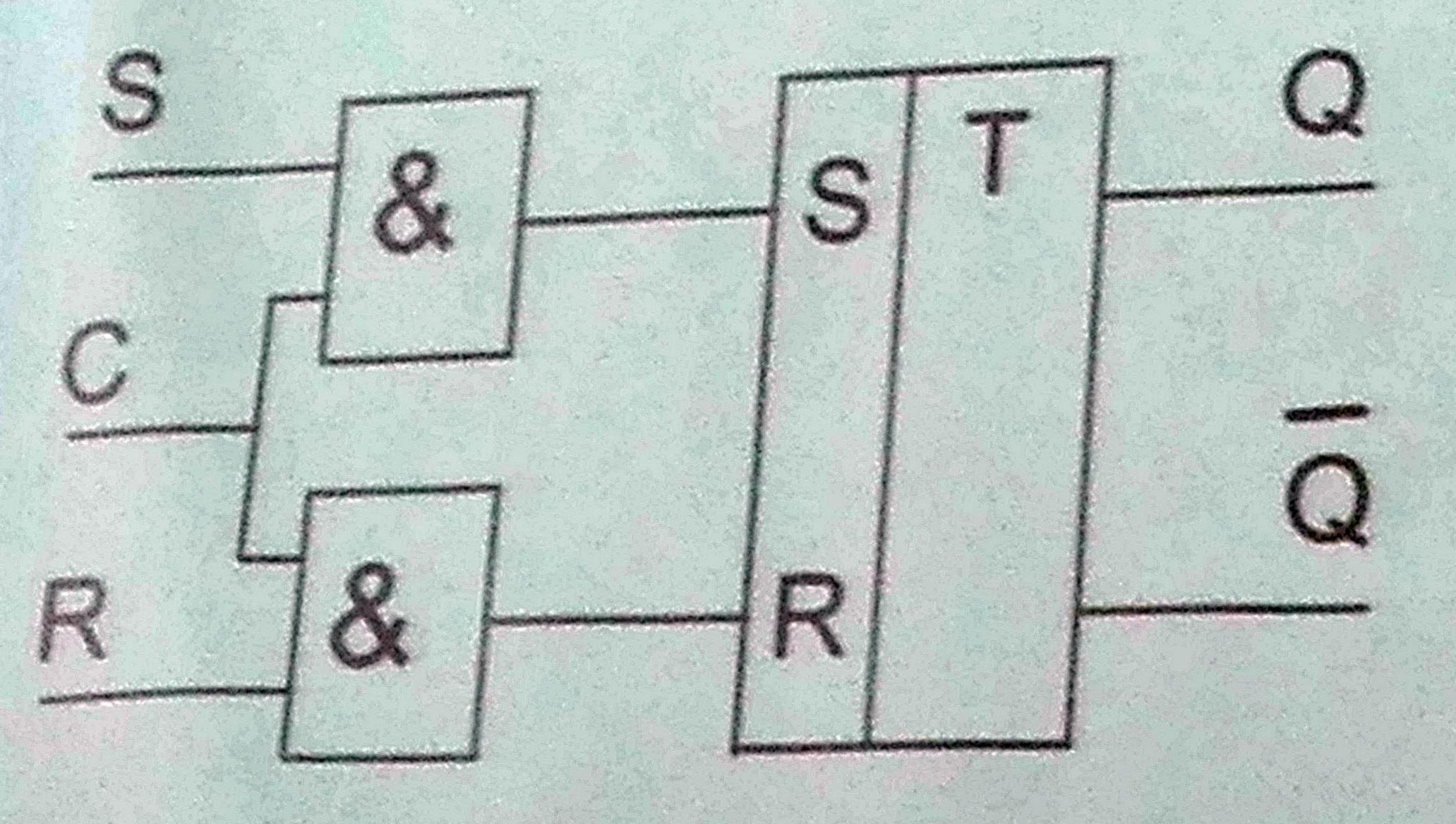

Структура синхронного одноступенчатого RS-триггера:

αS = S*C

αR = R*C

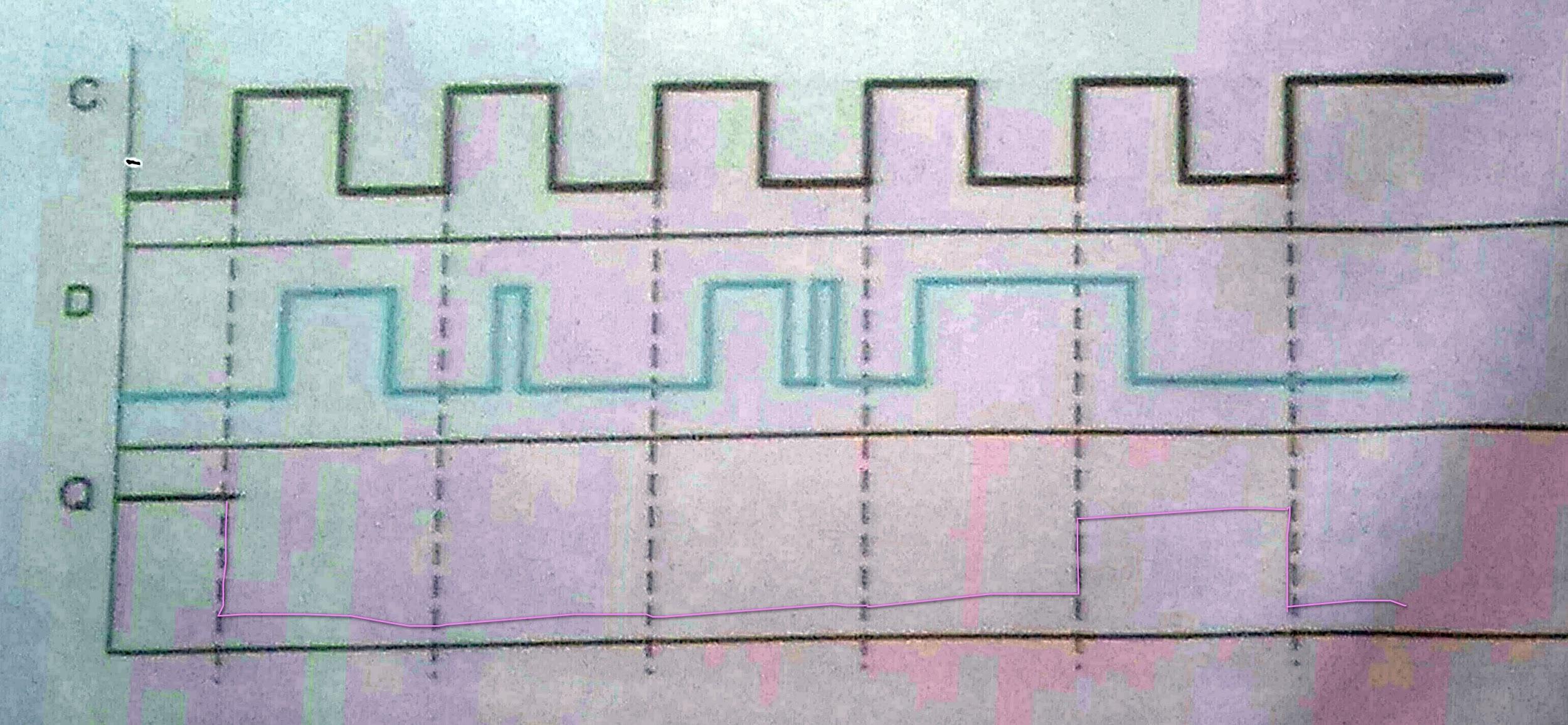

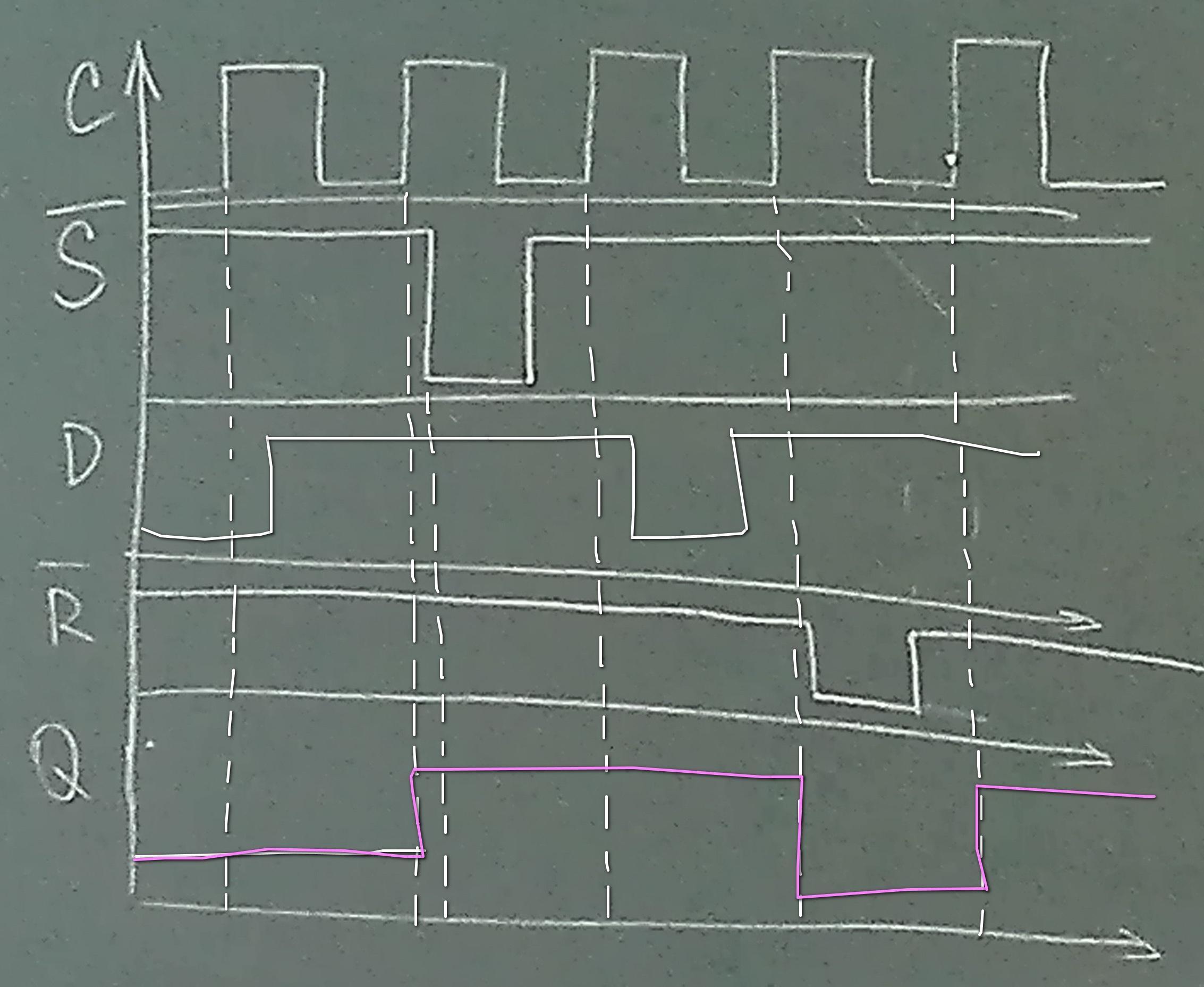

Временная диаграмма:

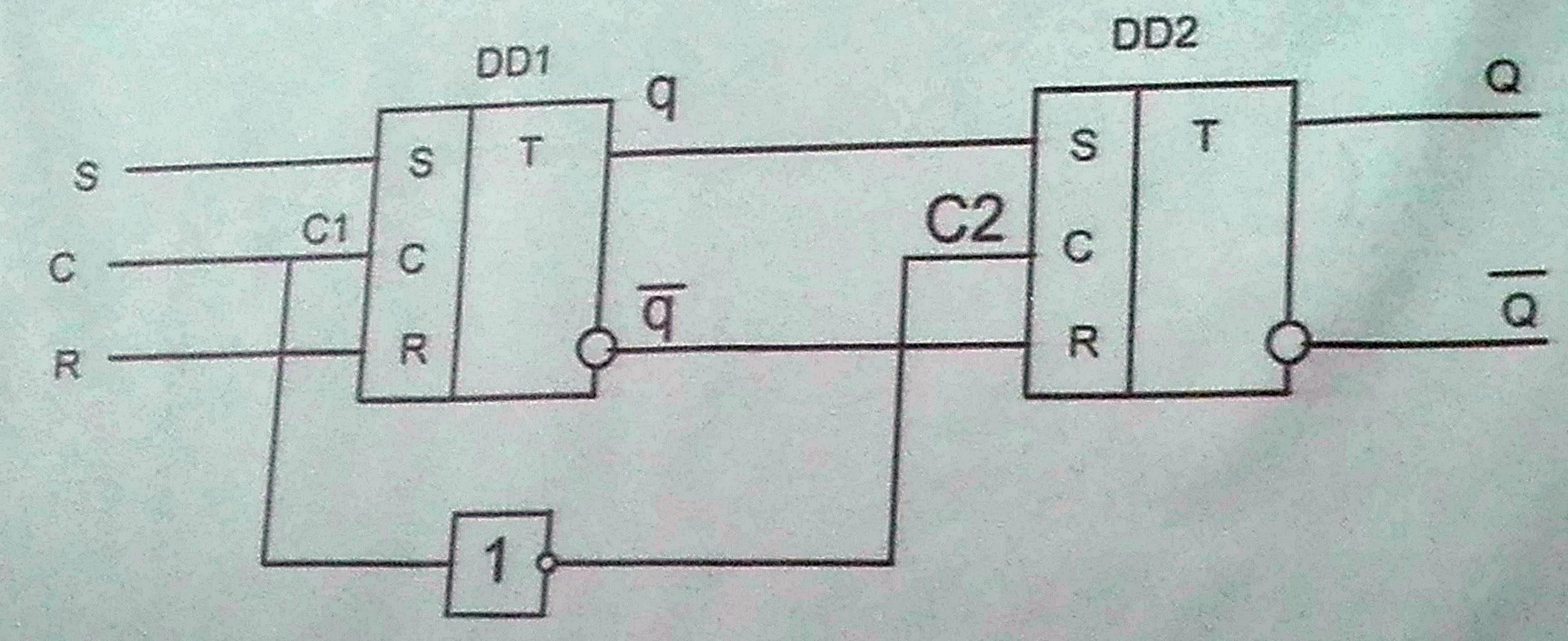

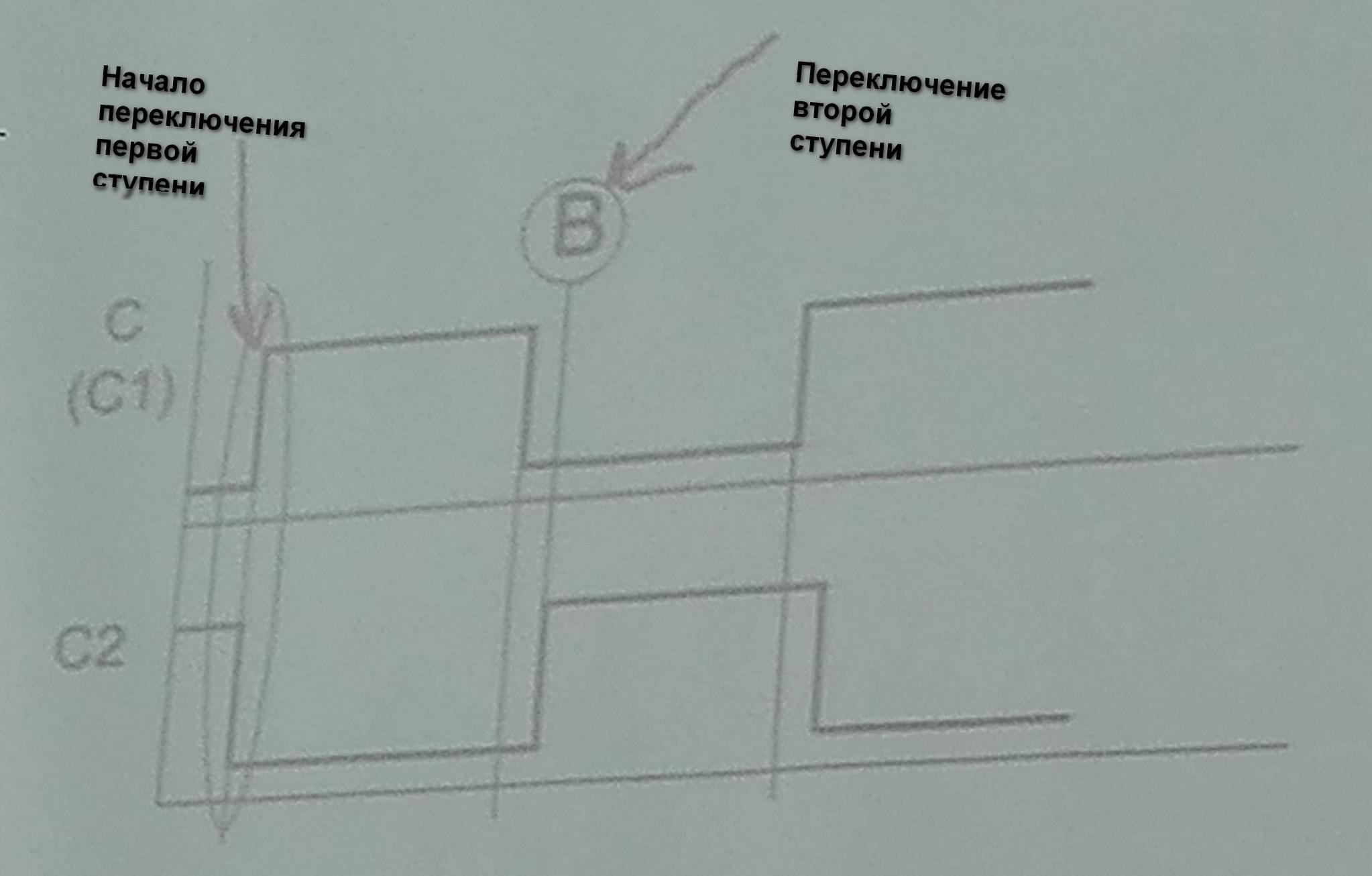

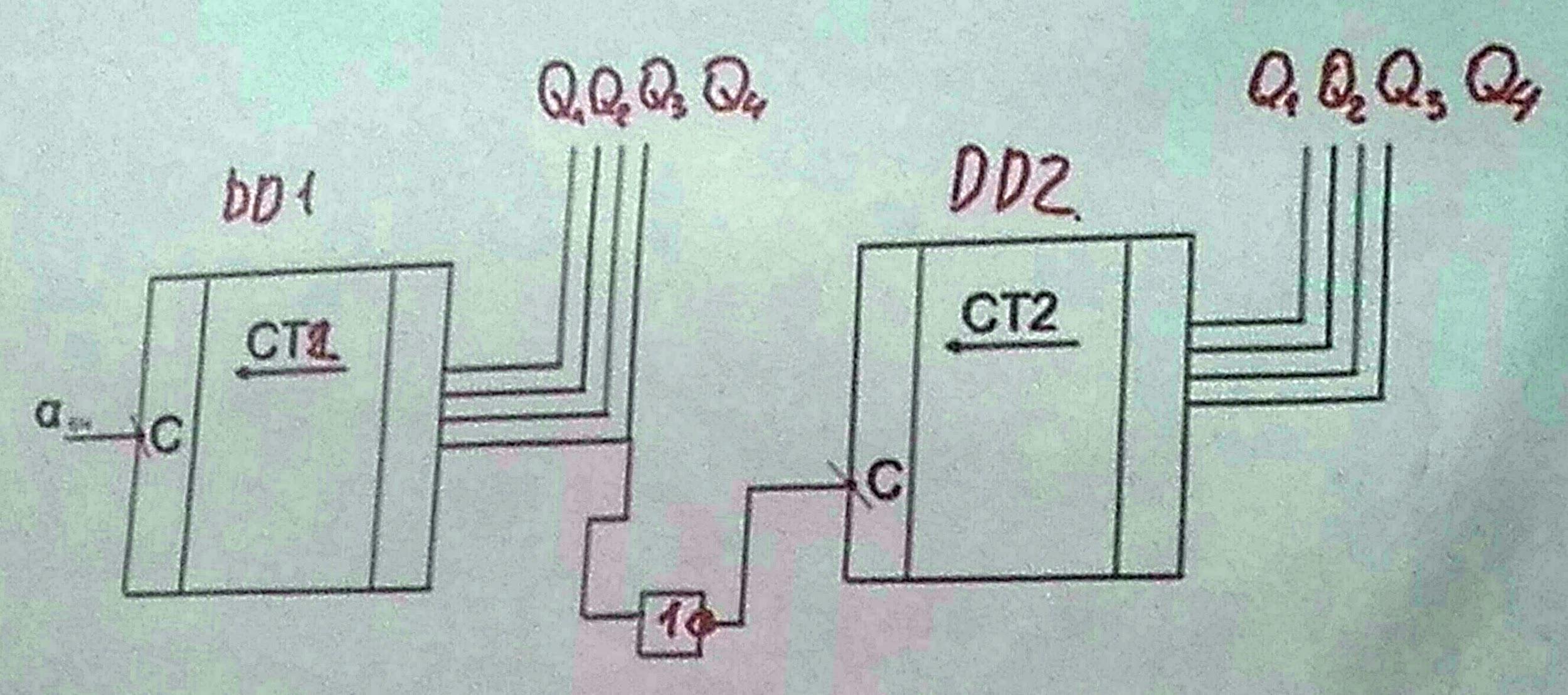

Двухступенчатый синхронный RS-триггер

Двухступенчатый

синхронный RS-триггер состоит из двух

одноступенчатых синхронных RS-триггеров,

объединённых по принципу «ведущий-ведомый».

При подаче синхроимпульса C переключается

первый триггер в соответствии с таблицей

функционирования одноступенчатого

синхронного RS-триггера. На вход C2

синхроимпульс C подаётся в инверсном

виде и таким образом, пока на входе

первого триггера синхроимпульс равен

«1», на входе второго он равен «0». И

второй триггер переключается после

того как переключился первый, т. е.

информация из первого триггера (первой

ступени) переписывается во второй

триггер (вторую ступень). Таким образом,

первая ступень переключается всегда,

пока C=1; вторая ступень переключается

по заднему фронту сигнала C, переписывая

информацию из первой ступени.

Временная диаграмма:

Временная диаграмма:

-

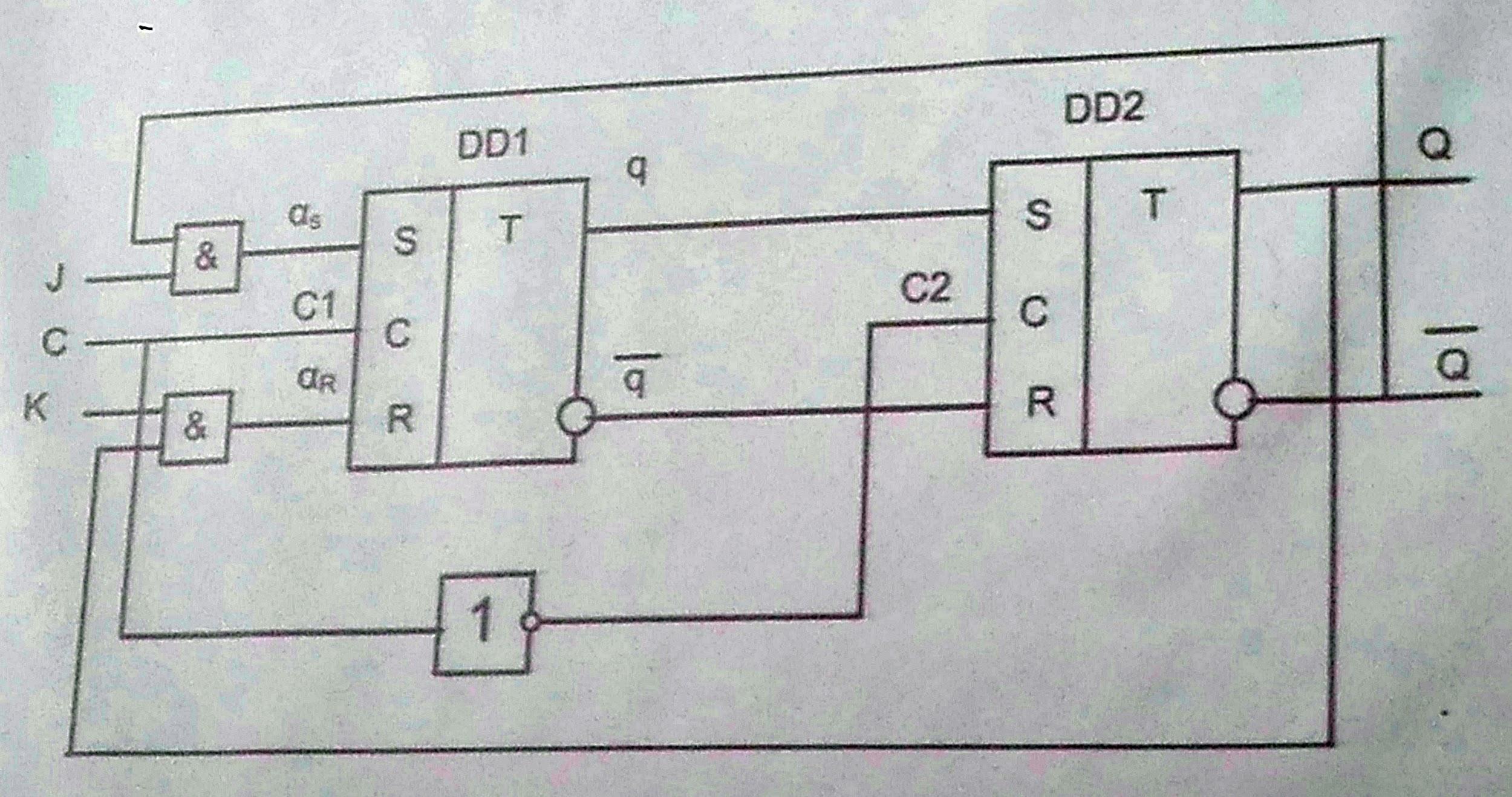

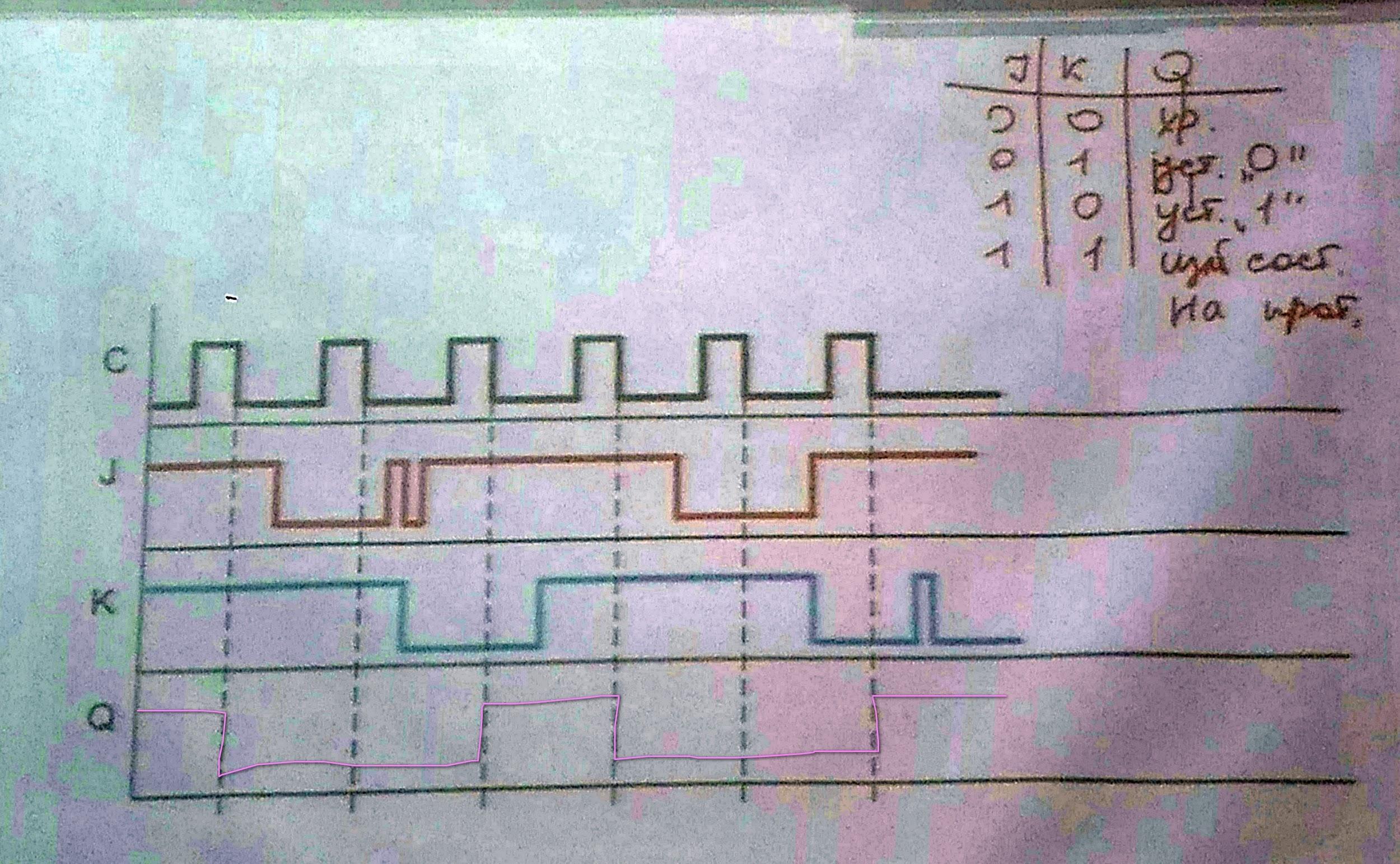

JK-триггер

|

J |

K |

Qt |

Qt+1 |

|

|

1 |

0 |

- |

1 |

независимо от Qt |

|

0 |

1 |

- |

0 |

независимо от Qt |

|

0 |

0 |

- |

Qt |

(хранение) |

|

1 |

1 |

Qt |

Qt+1 = !Qt |

изменение состояния на противоположное |

αS = J!Q

αR = KQ

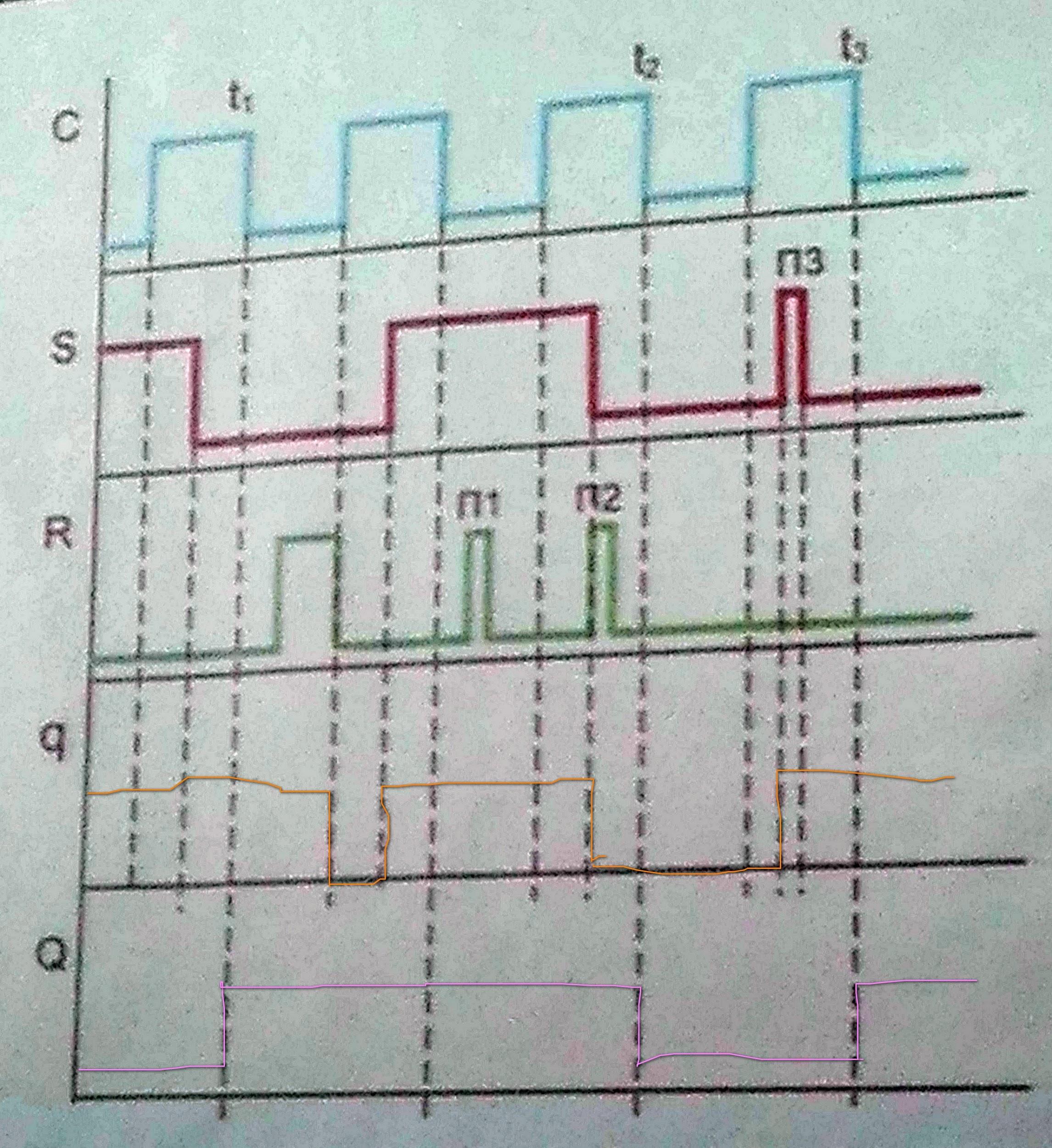

Временная диаграмма:

Первая ступень такого триггера переключается по сигналам αS и αR.

Вторая ступень переключается по заднему фронту синхроимпульса, переписывая информацию из первой ступени.

Данный триггер обладает наивысшей помехозащищённостью, но при этом, если помеха приходит при C=1, она переходит на выход как первой, так и второй ступени.

Для увеличения помехозащищённости лучше всего информацию на входах J и K менять в момент C=0. В этом случае можно сразу строить сигнал на выходе второй ступени.

При смене сигналов на входах J и K при C=1 строим сначала первую, затем вторую ступени.

Временная диаграмма:

-

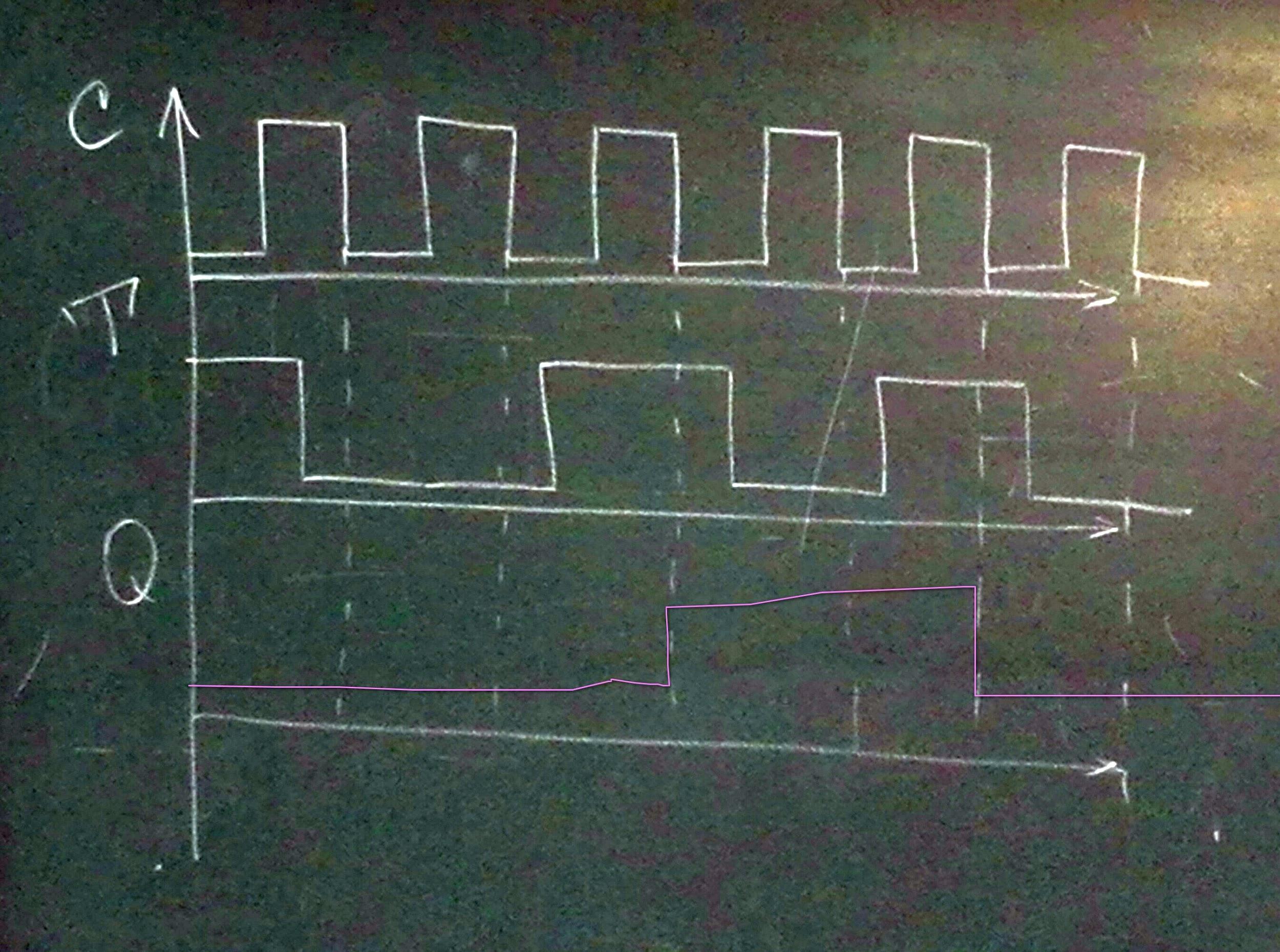

T-триггер

Временная диаграмма:

-

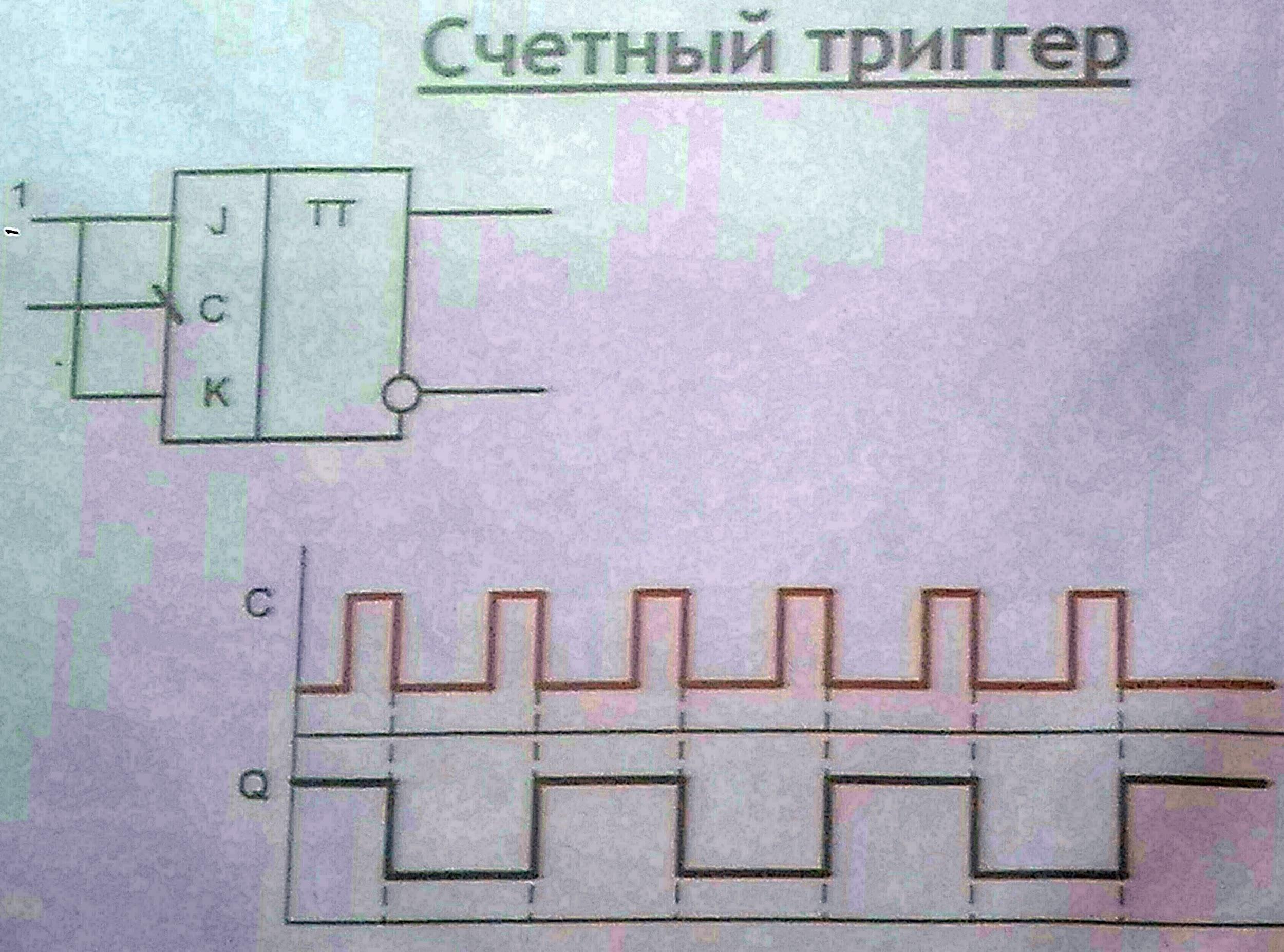

Счётный триггер

-

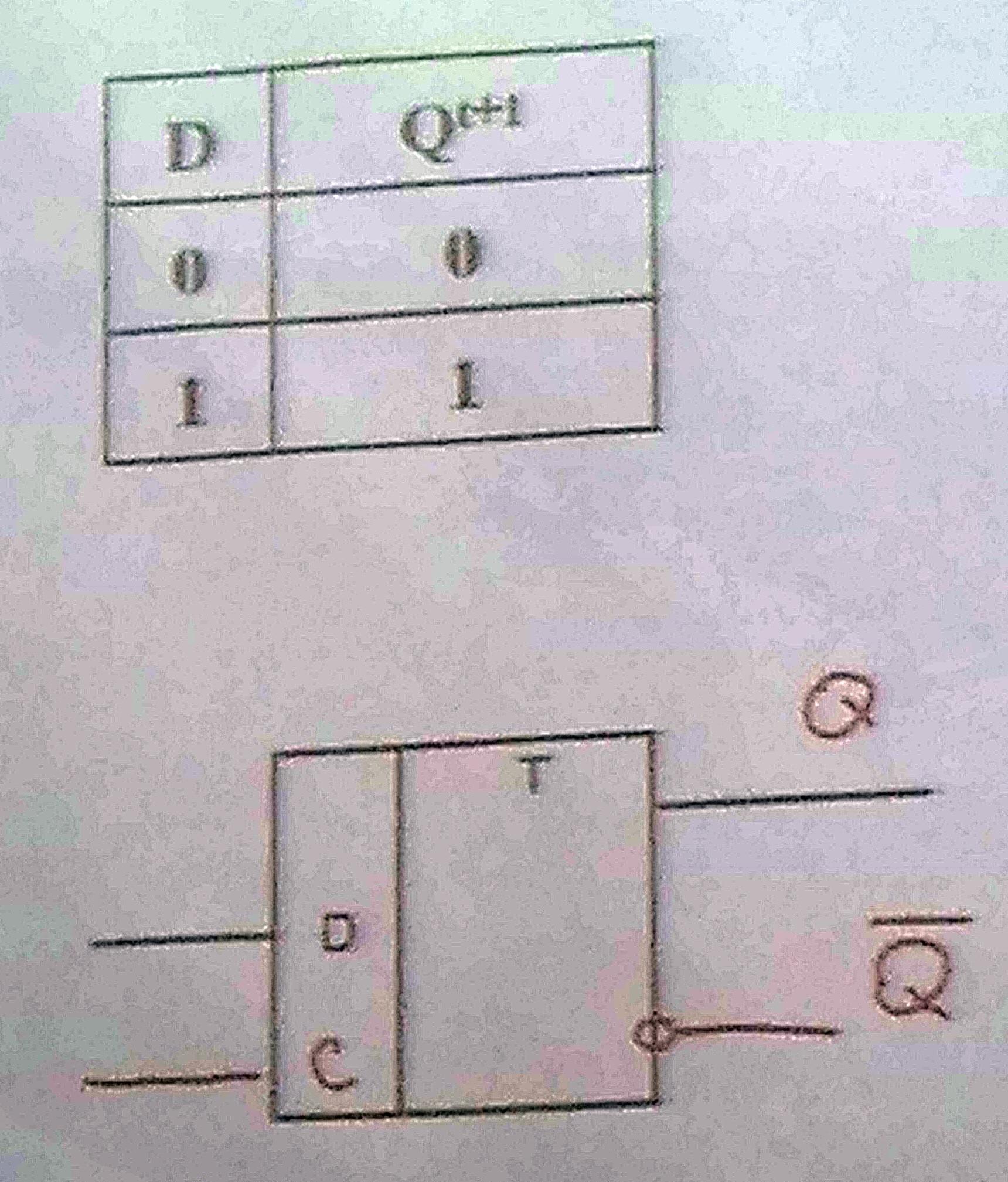

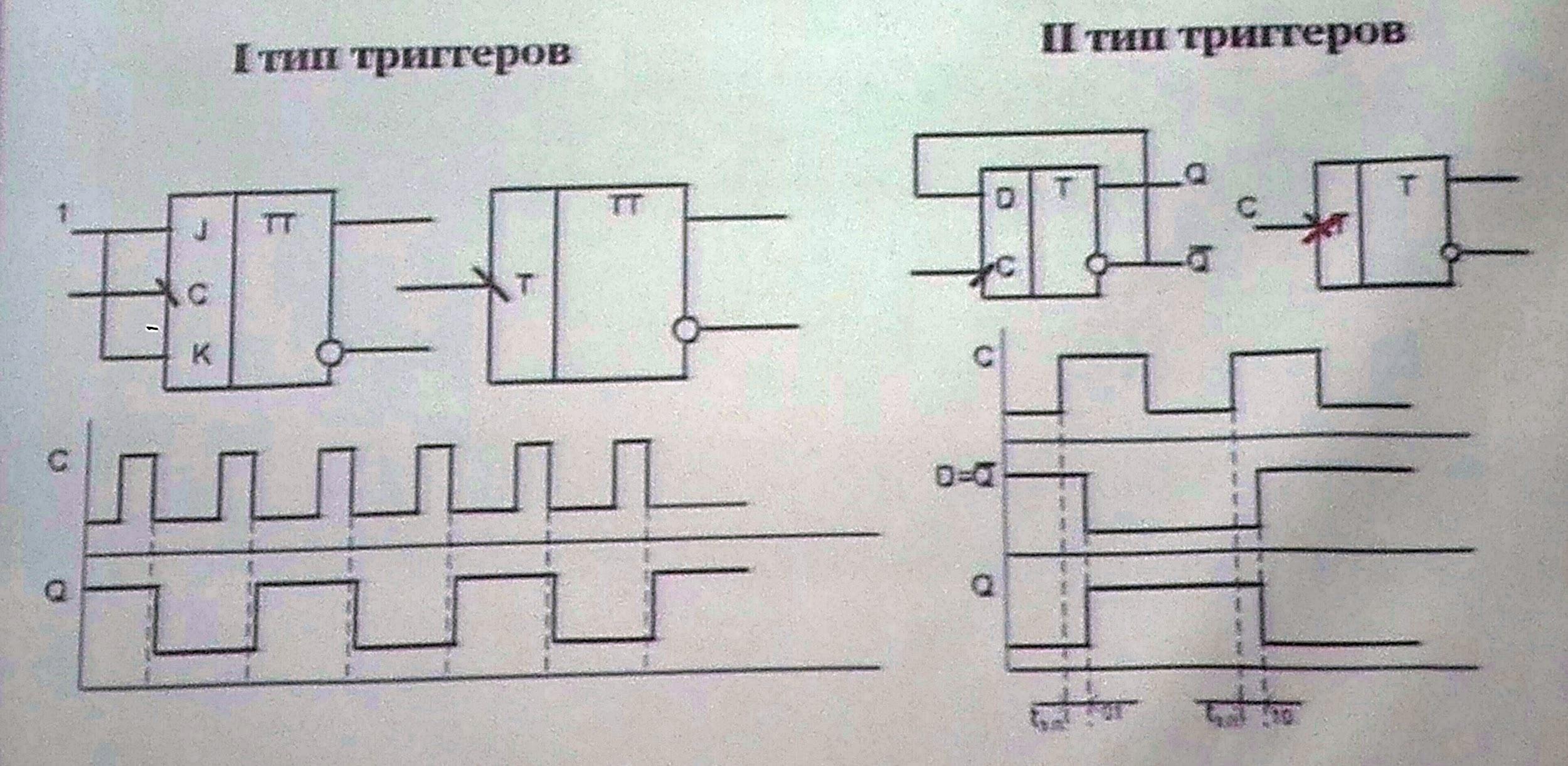

D-триггер

D-триггер со статическим управлением

Переключается при C=1.

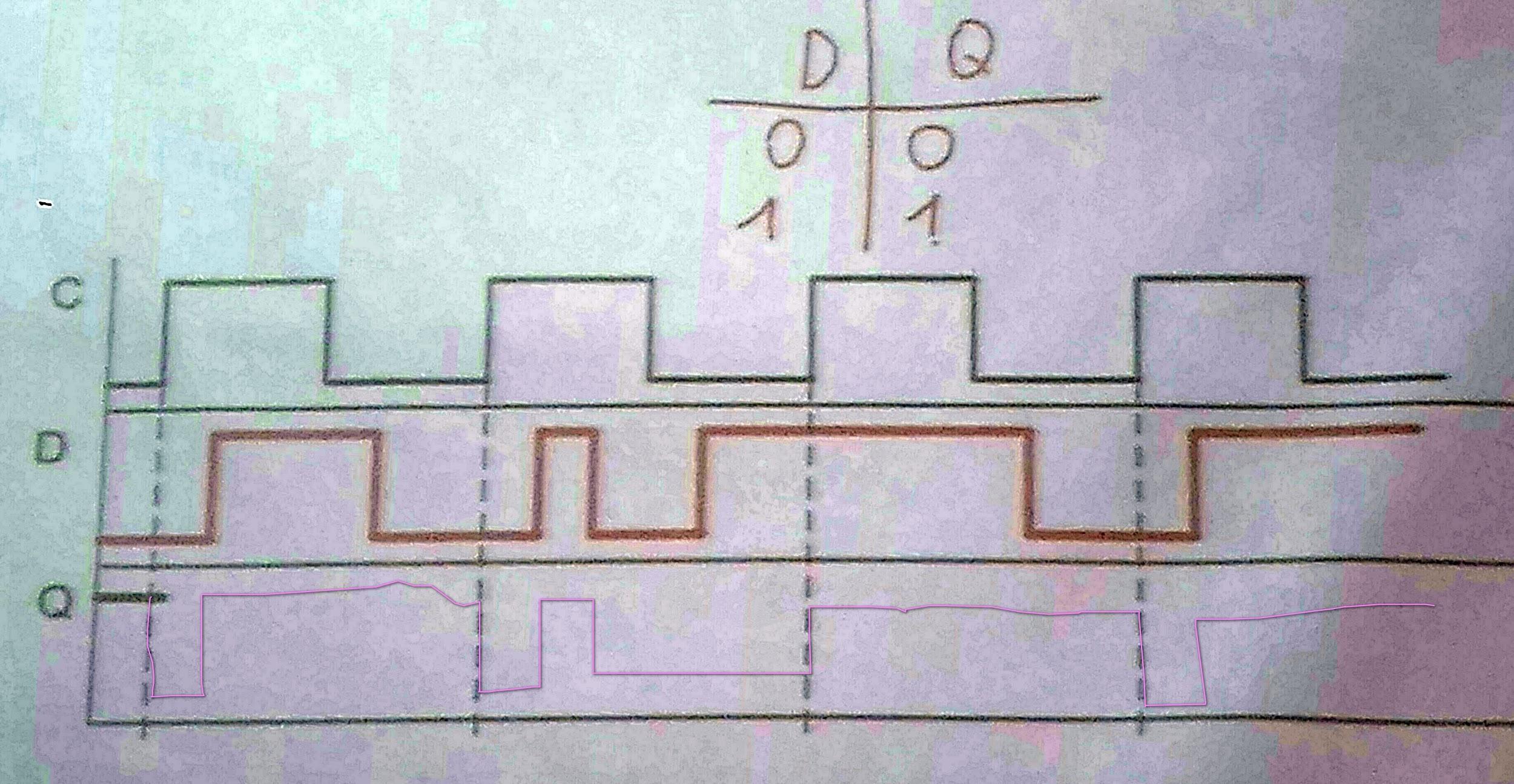

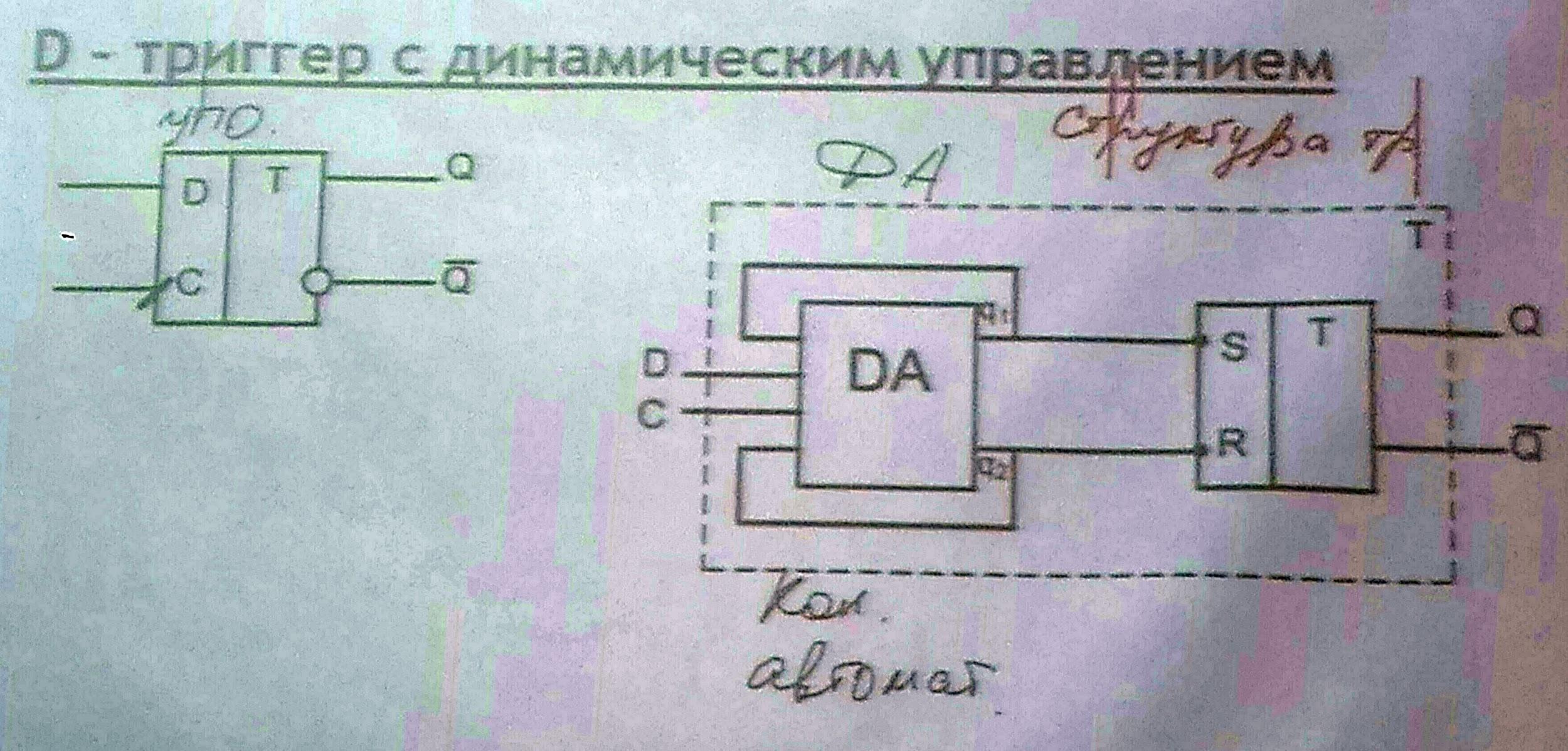

D-триггер с динамическим управлением

Переключается по переднему фронту синхроимпульса

Временная диаграмма

-

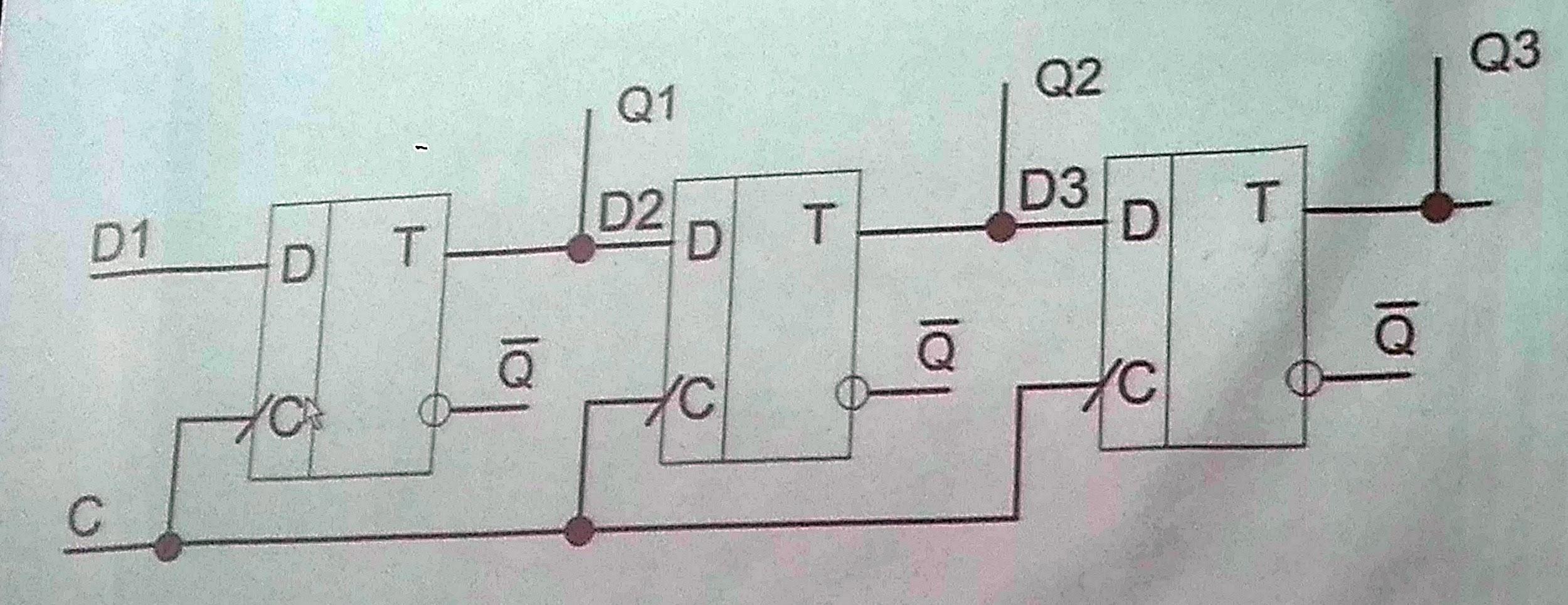

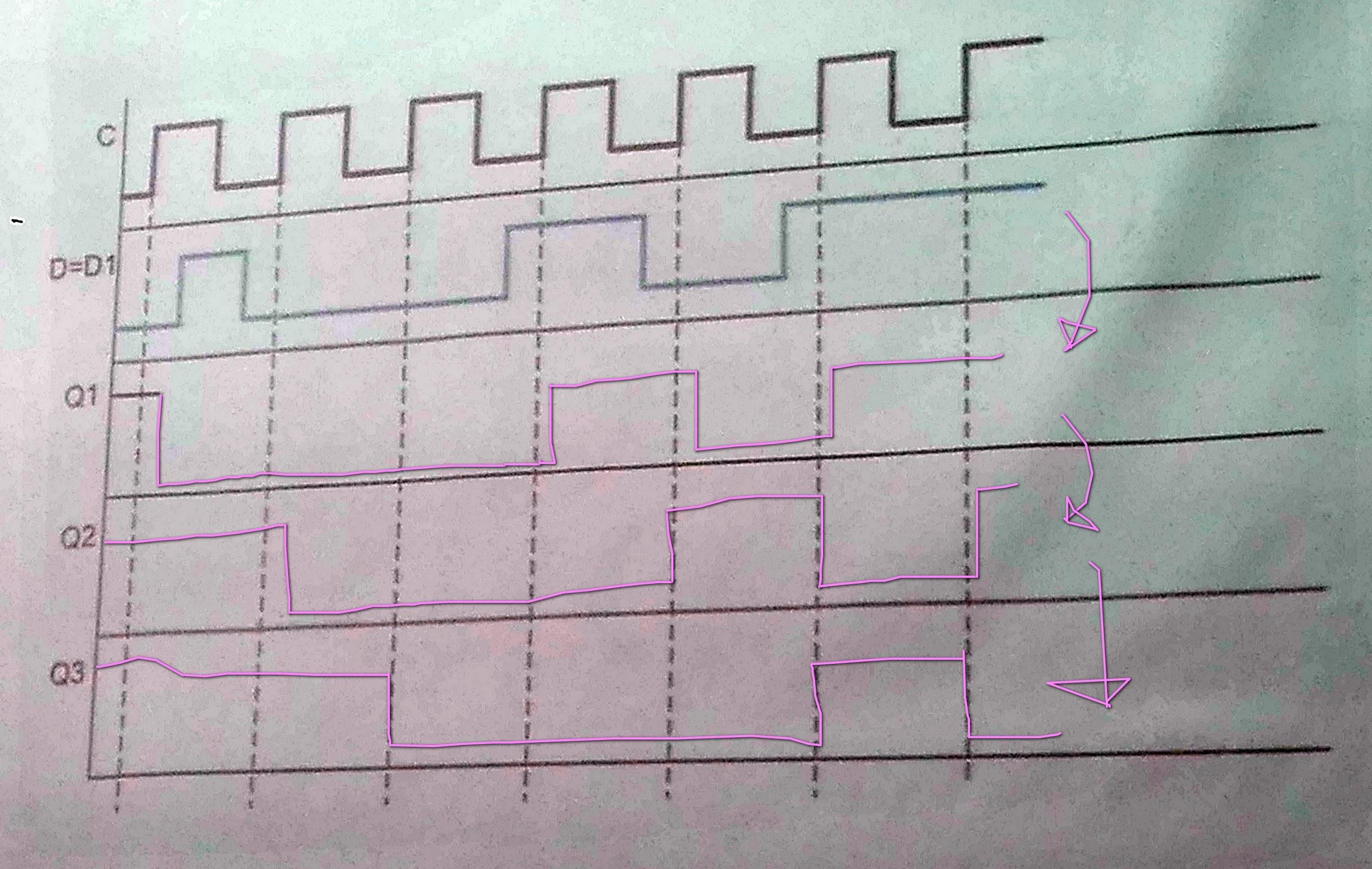

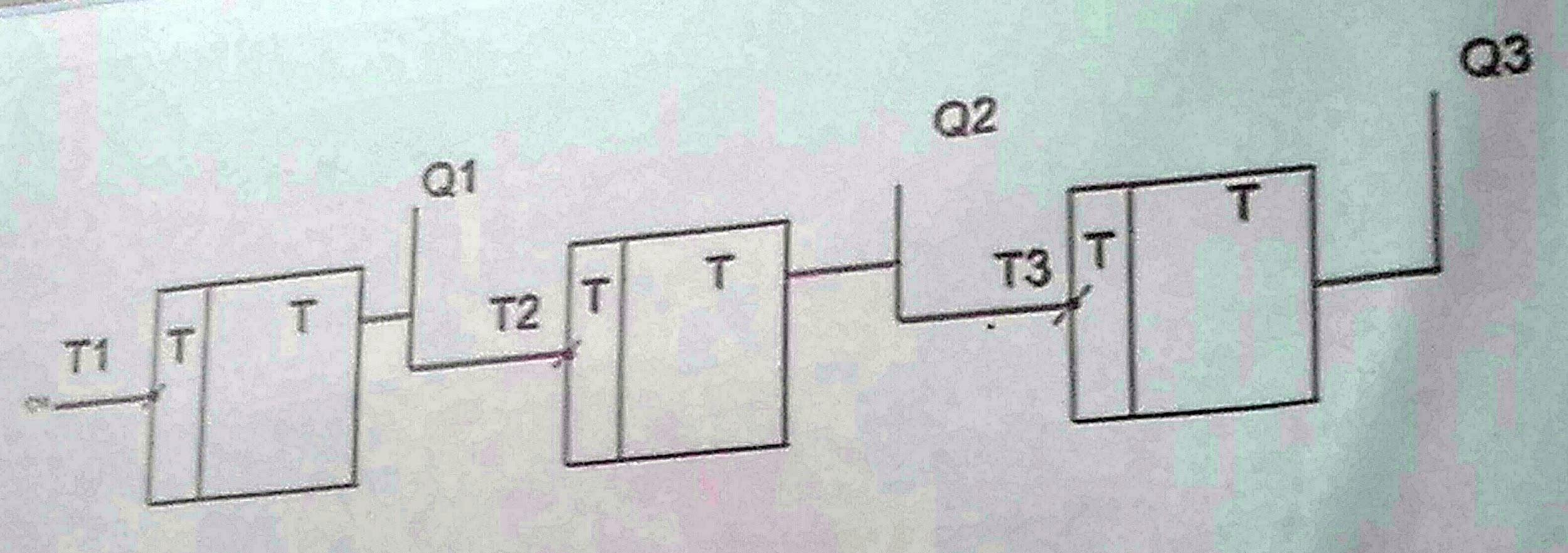

Последовательный регистр

Последовательный

регистр построен на D-триггерах с

динамическим управлением, соединённых

последовательно, т. е. сначала

переключается первый триггер, за ним

переключается второй, третий и т. д.

При этом сигнал подаётся на входы всех

триггеров одновременно.

При

построении временной диаграммы рассмотрим

и будем учитывать задержки переключения

каждого из триггеров в отдельности.

Каждый из триггеров последовательной цепочки сдвигает на один такт вправо входной импульс. Для построения этой схемы используются триггеры с большими задержками переключения.

-

Триггеры в интегральном исполнении

-

RS-триггеры

-

RS-триггеры обладают низкой помехозащищённостью, в результате этого они редко применяются при построении цифровых схем, но имеется небольшой набор микросхем, которые могут быть использованы при построении цифровых схем.

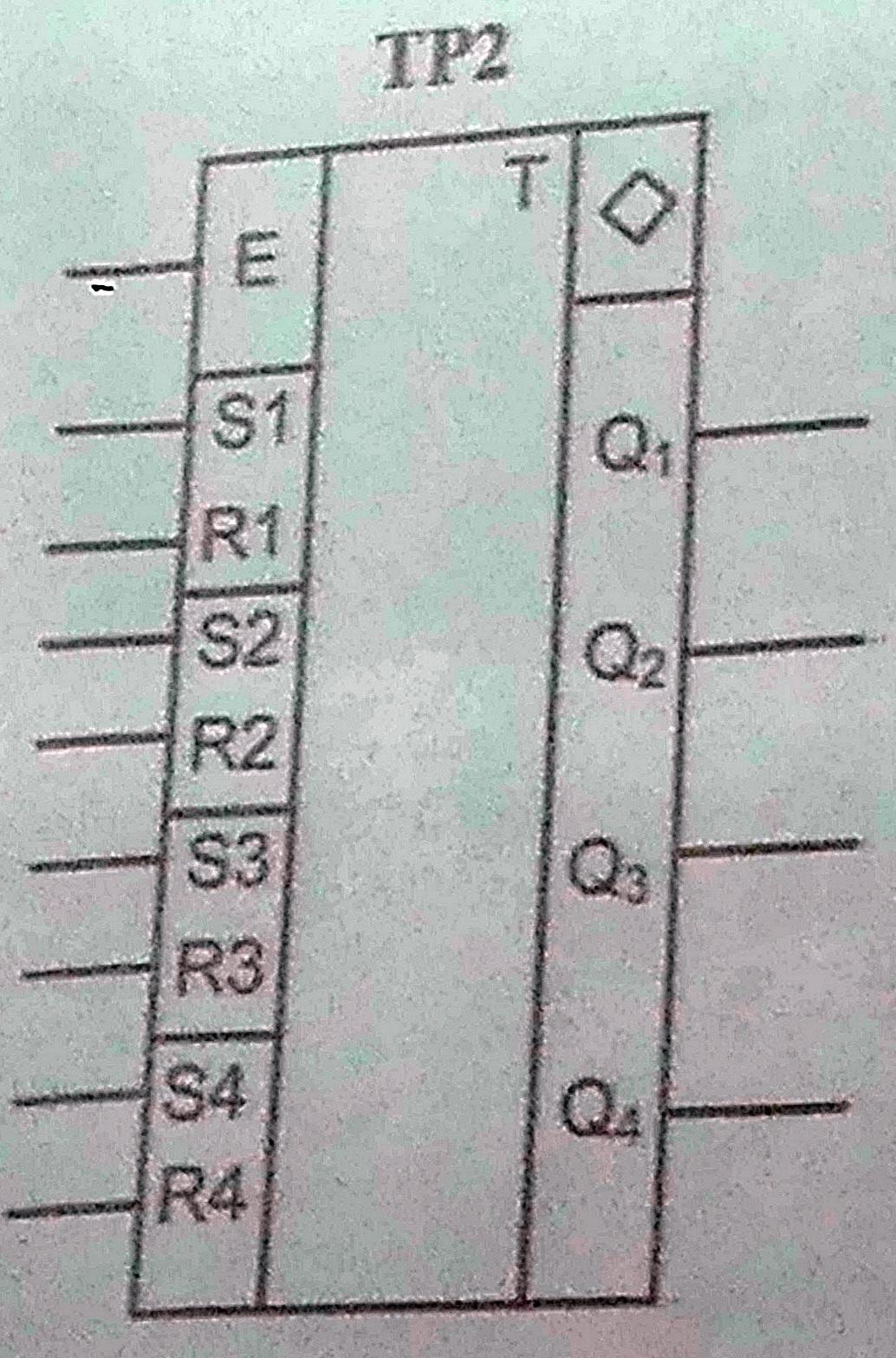

Микросхема

представляет собой четыре асинхронных

RS-триггера. Микросхема имеет три состояния

выхода: «0», «1», высокоимпедансное

(высокое сопротивление на выходе)

состояние. То есть выход при E=1 отключён

от входа, при E=0 — отключён от входа (?).

-

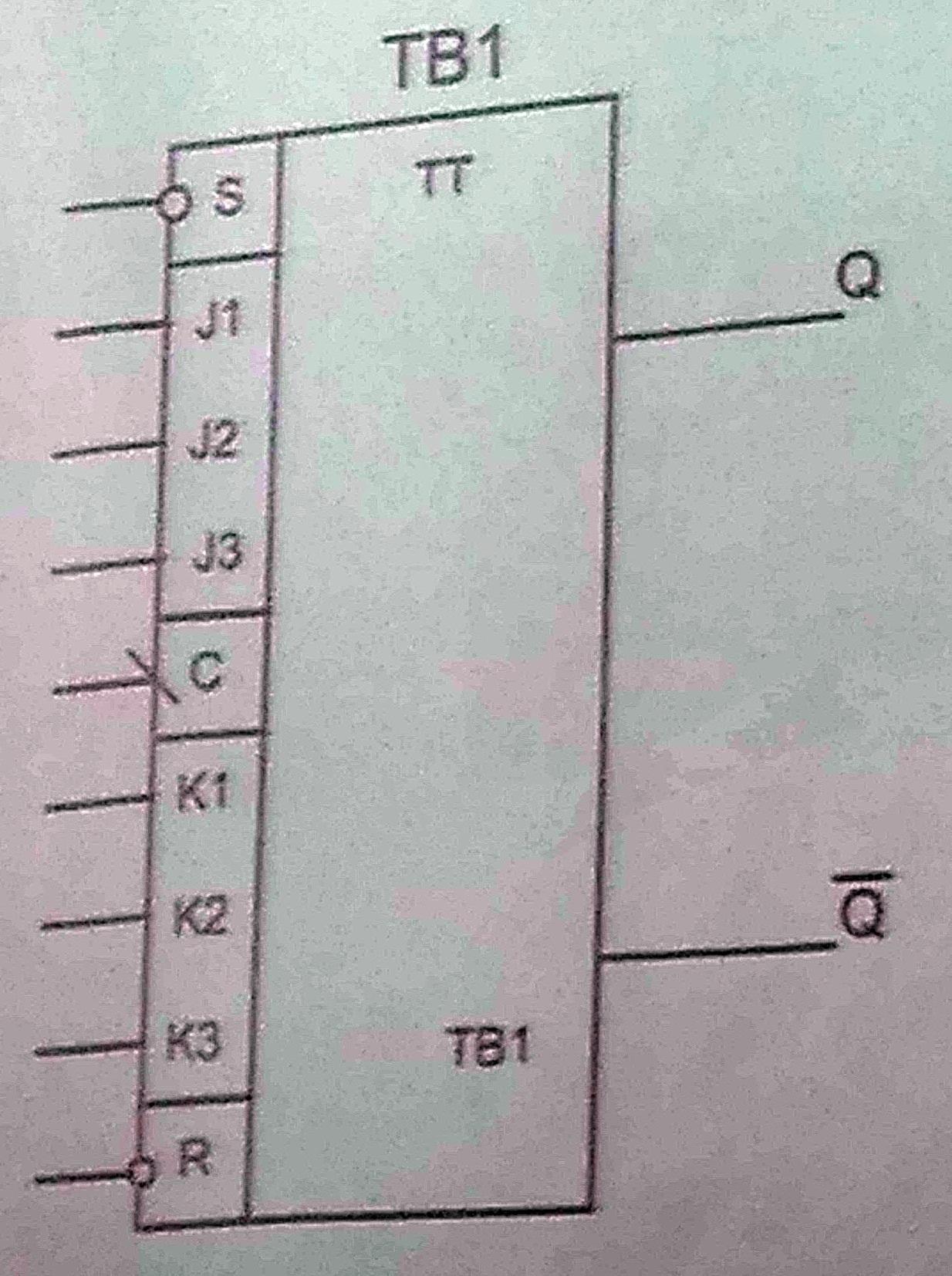

JK-триггер

Входы J1, J2, J3 соединены между собой операцией умножения. Аналогично организовано для входа K. В микросхеме имеются входы S-инверсное и R-инверсное, которые обладают наивысшим приоритетом.

S=0, R=1 – триггер переключается в единицу, независимо от информации на входах J и K.

S=1, R=0 – триггер переключается в ноль, независимо от J и K.

S=1, R=1 – триггер переключается по входам J и K.

-

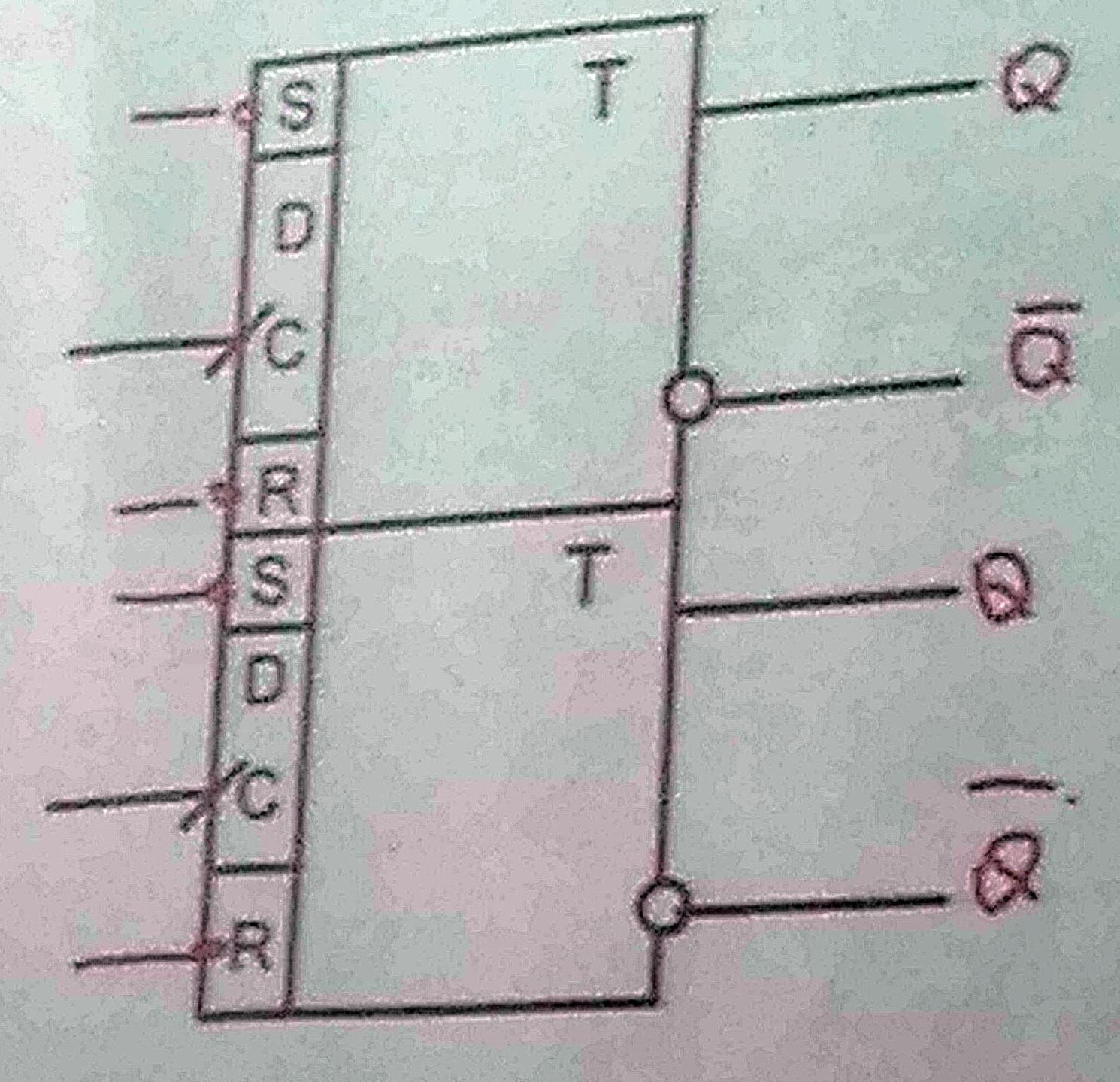

D-триггеры

Микросхема ТМ5:

...также объединены для C3 и C4.

Микросхема ТМ2:

|

SH |

RH |

Qt+1 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

1 |

1 |

хранение (работа по входу D) |

Микросхема состоит из двух динамических D-триггеров, абсолютно самостоятельных, т. е. могут использоваться либо один, либо два триггера одновременно, каждый из триггеров имеет асинхронные входы предустановки S-инверсное и R-инверсное.

-

Узлы цифровых устройств (ЦУ)

1. Комбинационные (преобразование кодов, шифраторы, дешифраторы, коммутаторы, сумматоры, устройства сравнения).

2. Последовательные (счётчики, делители частоты, формирователи интервалов времени, устройство временной привязки, регистры).

-

Счётчики

Счётчик — узел ЦУ, выполняющий операцию подсчёта входных импульсов.

Классификация счётчиков

1. В зависимости от способа организации:

* асинхронные

* синхронные

2. В зависимости от направления счёта:

* суммирующие

* вычитающие

* реверсивные

3. В зависимости от перерабатываемого кода:

* двоичные

* двоично-десятичные

* прочие

4. По способу организации цепей переноса между разрядами счётчика:

* последовательные

* параллельные

* комбинированные

Модуль счёта (М) — число состояний счётчика.

Модуль счёта двоичного n-разрядного счётчика:

M = 2n.

Модуль счёта десятично-десятичного n-разрядного счётчика:

M = 10n.

-

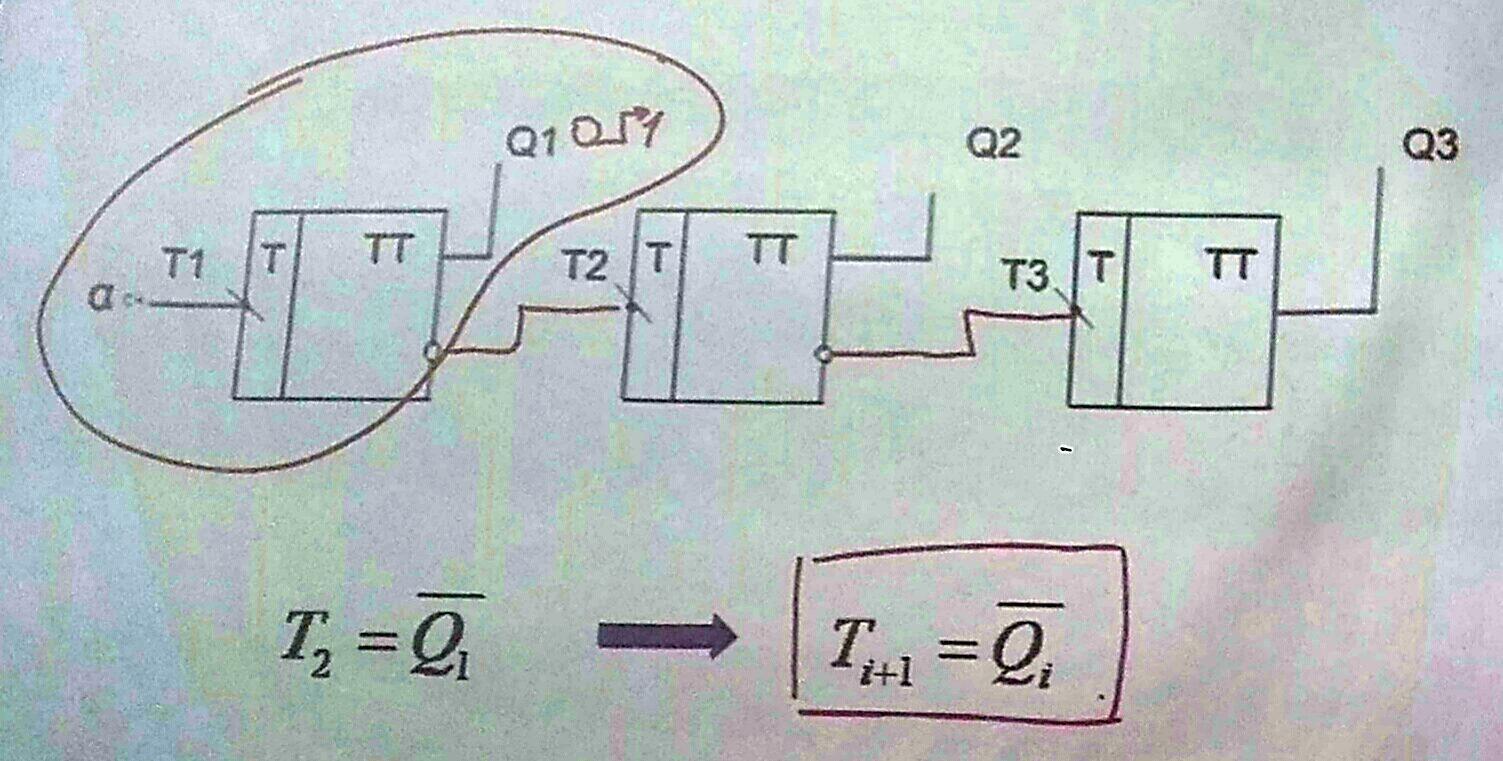

Асинхронные двоичные счётчики (АДС)

АДС могут быть построены на триггерах двух типов:

-

Асинхронный двоичный суммирующий счётчик

Рассмотрим принцип построения 3-разрядного счётчика.

Модуль счёта такого счётчика:

M = 23 = 8

То есть он считает от 0 до 7.

Таблица функционирования такого счётчика:

|

t |

N |

Q3 |

Q2 |

Q1 |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

2 |

2 |

0 |

1 |

0 |

|

3 |

3 |

0 |

1 |

1 |

|

4 |

4 |

1 |

0 |

0 |

|

5 |

5 |

1 |

0 |

1 |

|

6 |

6 |

1 |

1 |

0 |

|

7 |

7 |

1 |

1 |

1 |

|

8 |

0 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

Ti+1 = Qi

-

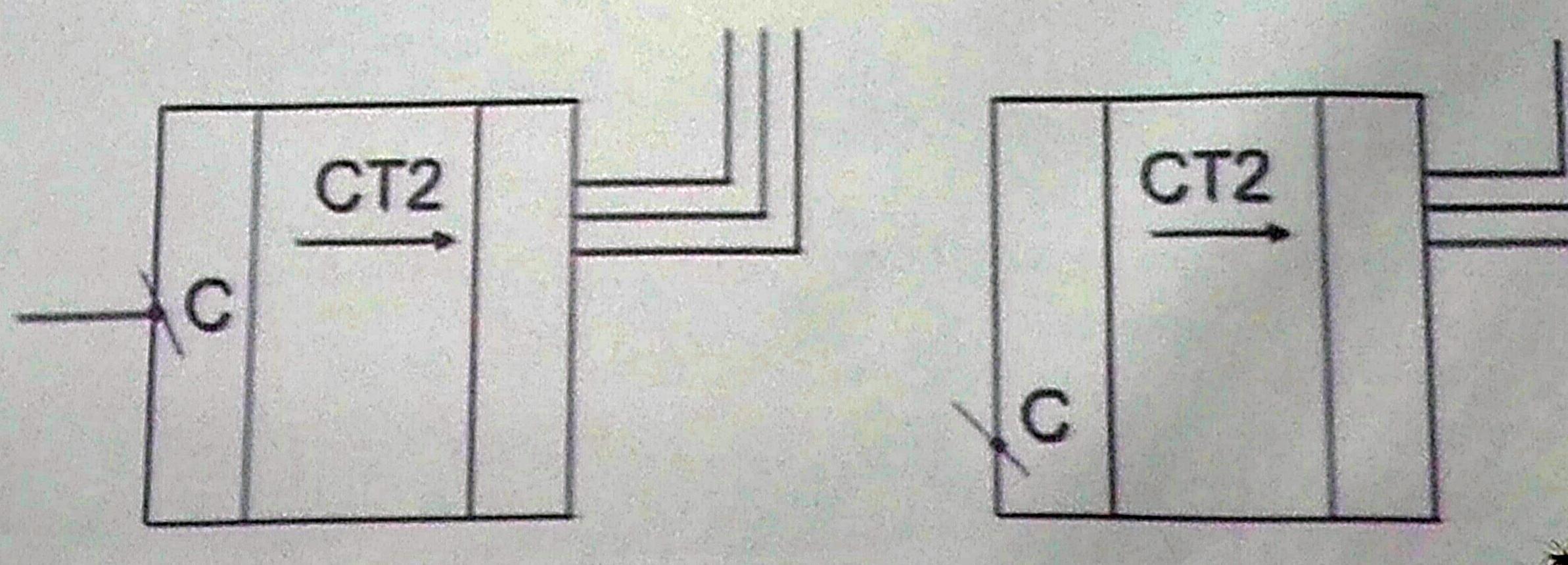

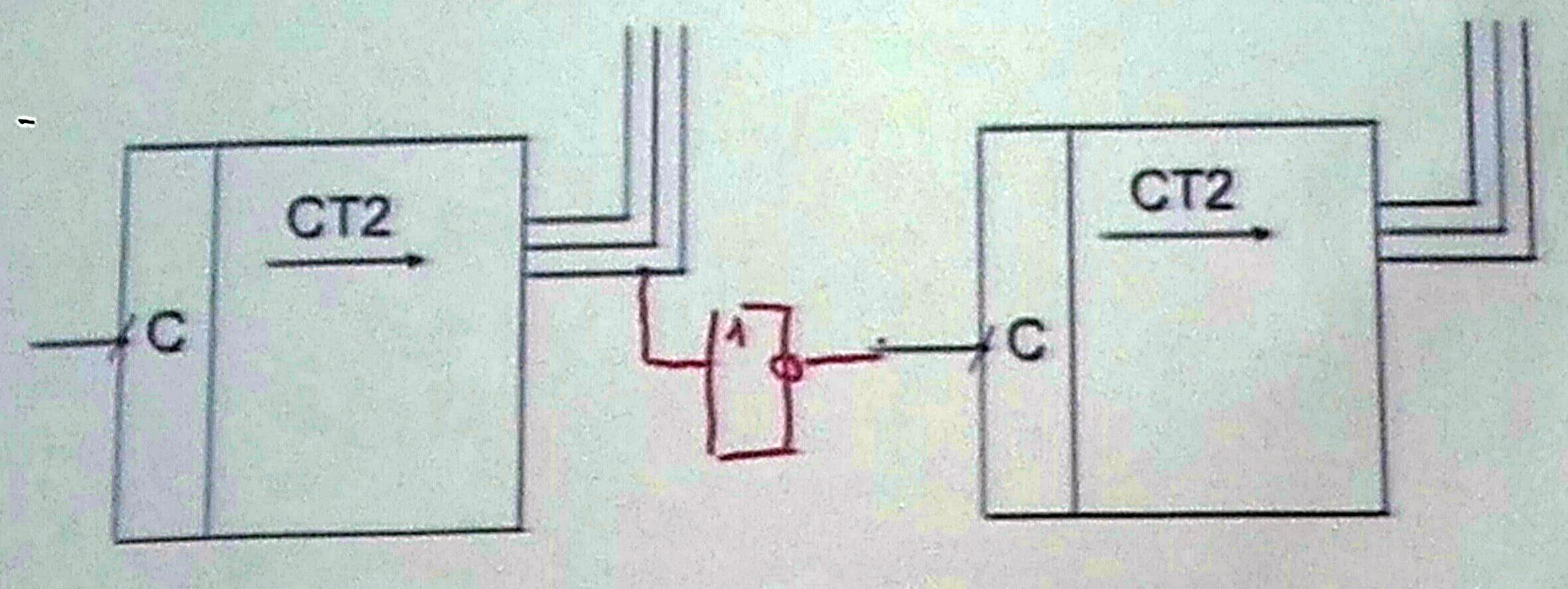

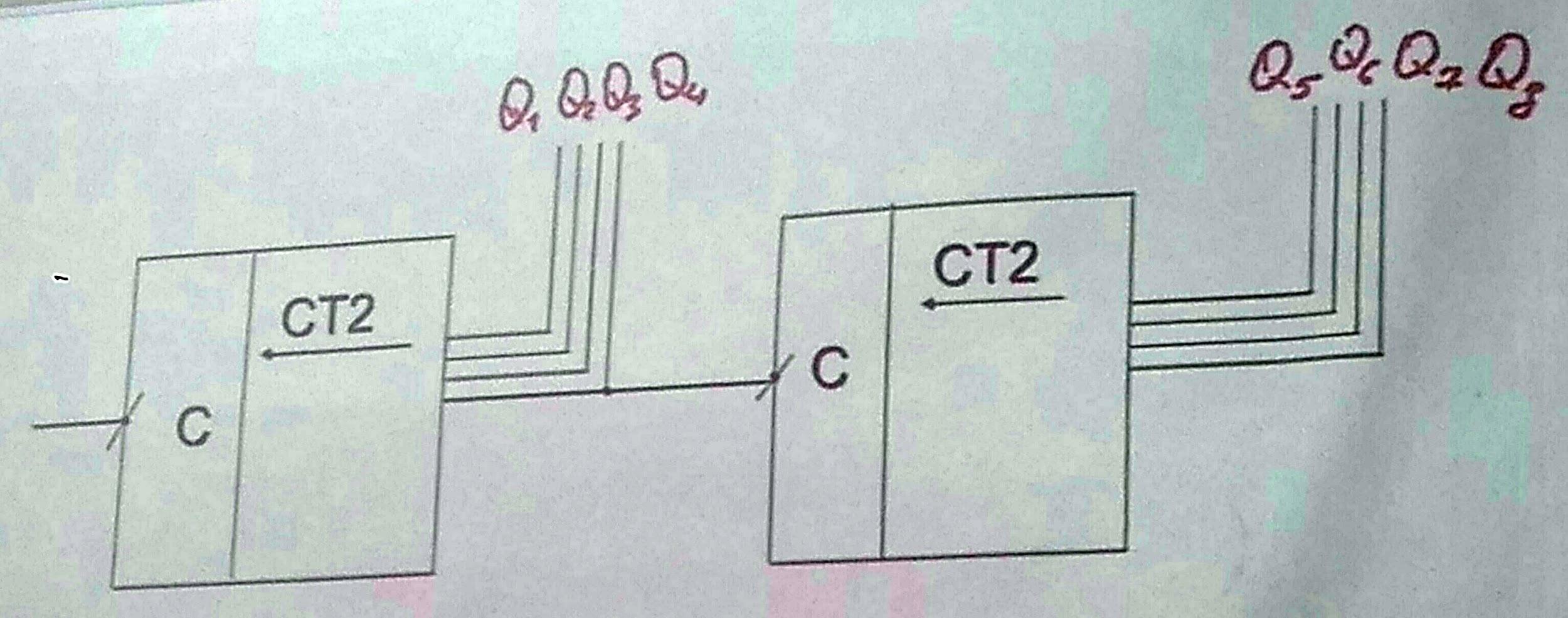

Каскадное соединение счётчиков

Ti+1 = !Qi

-

Асинхронный двоичный вычитающий счётчик

|

t |

Q3 |

Q2 |

Q1 |

|

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

0 |

|

2 |

1 |

0 |

1 |

|

3 |

1 |

0 |

0 |

|

4 |

0 |

1 |

1 |

|

5 |

0 |

1 |

0 |

|

6 |

0 |

0 |

1 |

|

7 |

0 |

0 |

0 |

|

8 |

1 |

1 |

1 |

|

9 |

1 |

1 |

0 |

Трёхразрядный вычитающий асинхронный счётчик реализован на счётных триггерах, переключающихся по заднему фронту (счётный триггер реализован на JK-триггере).

Второй триггер переключается в тот момент, когда первый переключается из 0 в 1.

Следовательно, для переключения второго триггера, который переключается в перепад из 1 в 0, необходимо соединить с инверсным выходом первого триггера.

Второй триггер должен переключиться, согласно таблице функционирования счётчика, когда на выходе первого перепад из 0 в 1 (Q1). Тогда на !Q1 будет перепад из 1 в 0.

Второй триггер, согласно его УГО, переключается по заднему фронту, т. е. по перепаду из 1 в 0.

Следовательно, T2 = !Q1.

-

Каскадное соединение счётчиков, переключающихся по заднему фронту

Счётчик реализован на триггерах, переключающихся по переднему фронту.

Второй триггер, согласно таблице, должен переключиться перепадом из 0 в 1.

Второй триггер переключается по переднему фронту, то есть по перепаду из 0 в 1.

Следовательно необходимо Q1 соединить с T2, а Q2 – с T3.

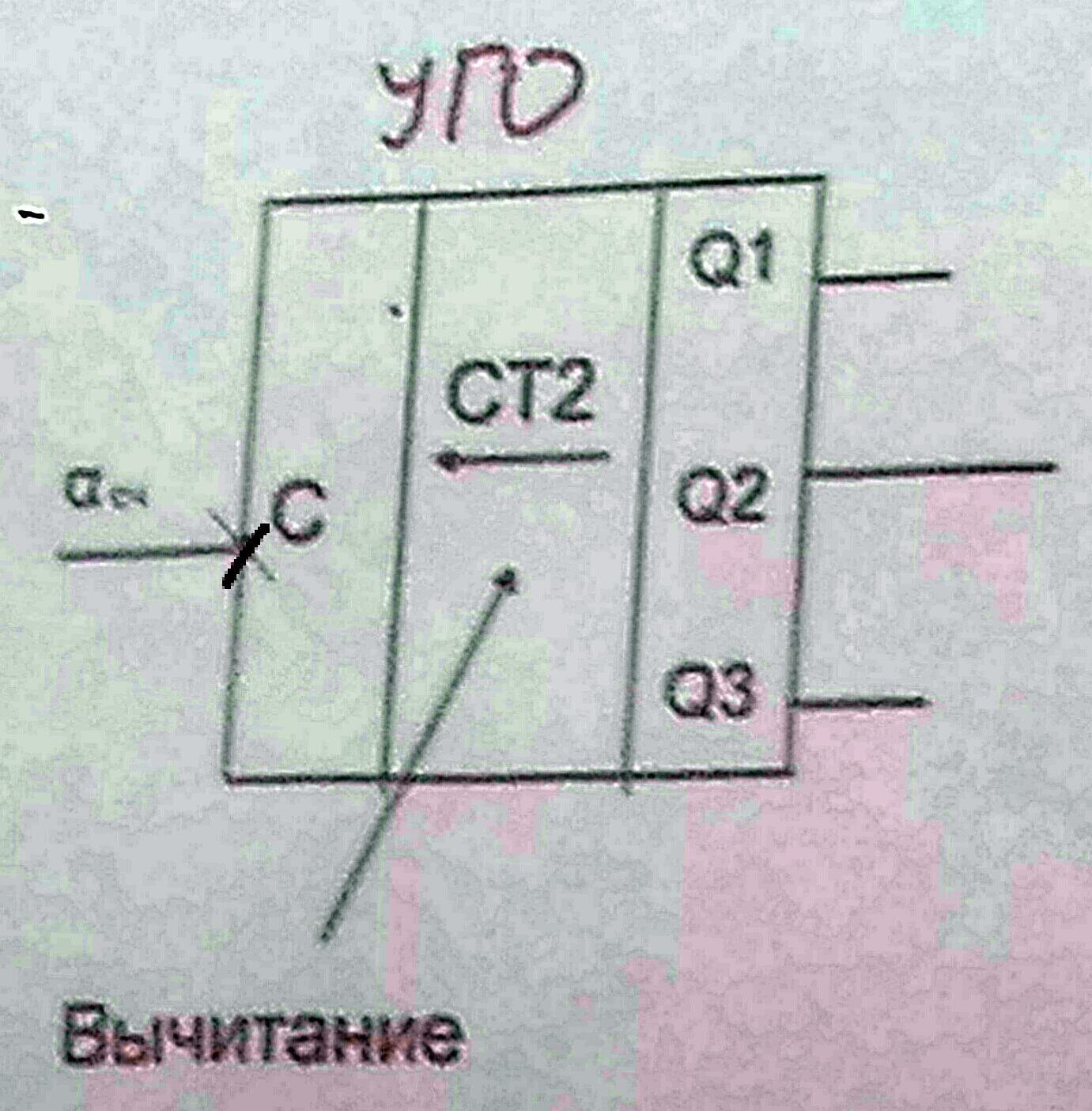

УГО вычитающего счётчика:

Каскадное соединение счётчиков, реализованных на триггерах, переключающихся по переднему фронту

-

Реверсивные асинхронные счётчики

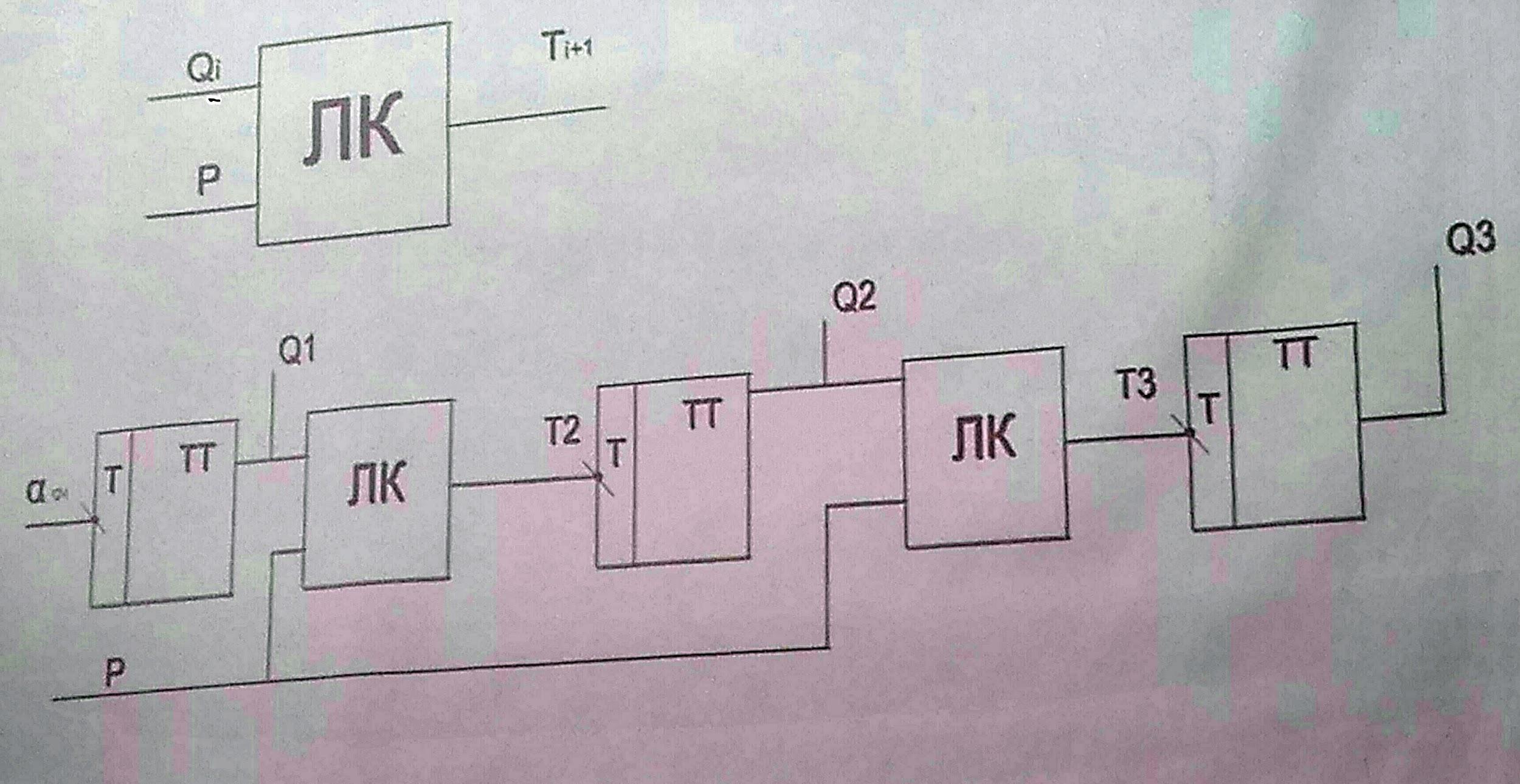

Для построения реверсивных счётчиков используются логические коммутаторы (ЛК), которые выполняют функцию подключения прямого выхода или инверсного ко входу последующего триггера.

На один из входов ЛК подаётся Qi, на другой — сигнал реверса (Р), указывающий на направление счёта:

R = 1 – суммирование;

R

= 0 – вычитание.

-

Реверс асинхронных счётчиков «на ходу»

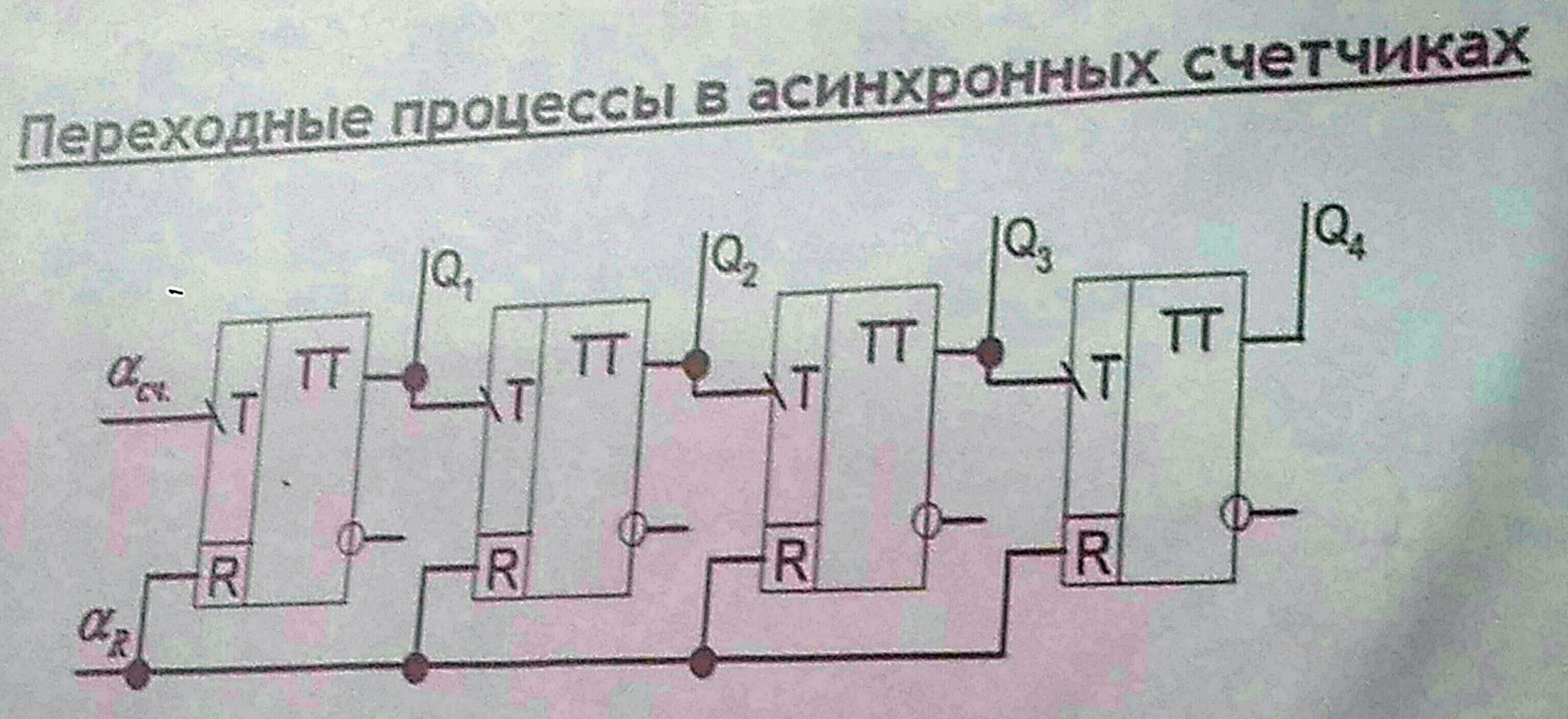

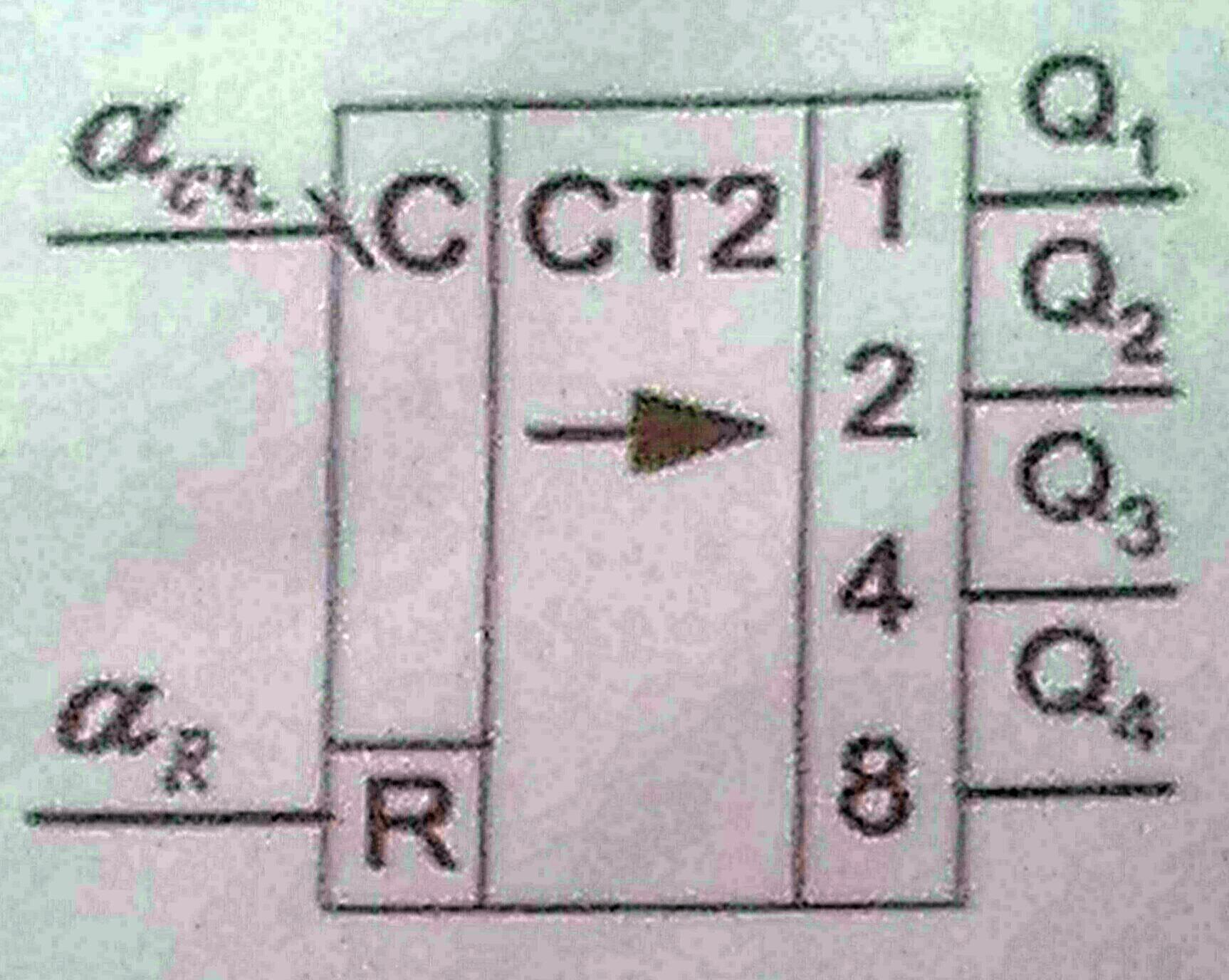

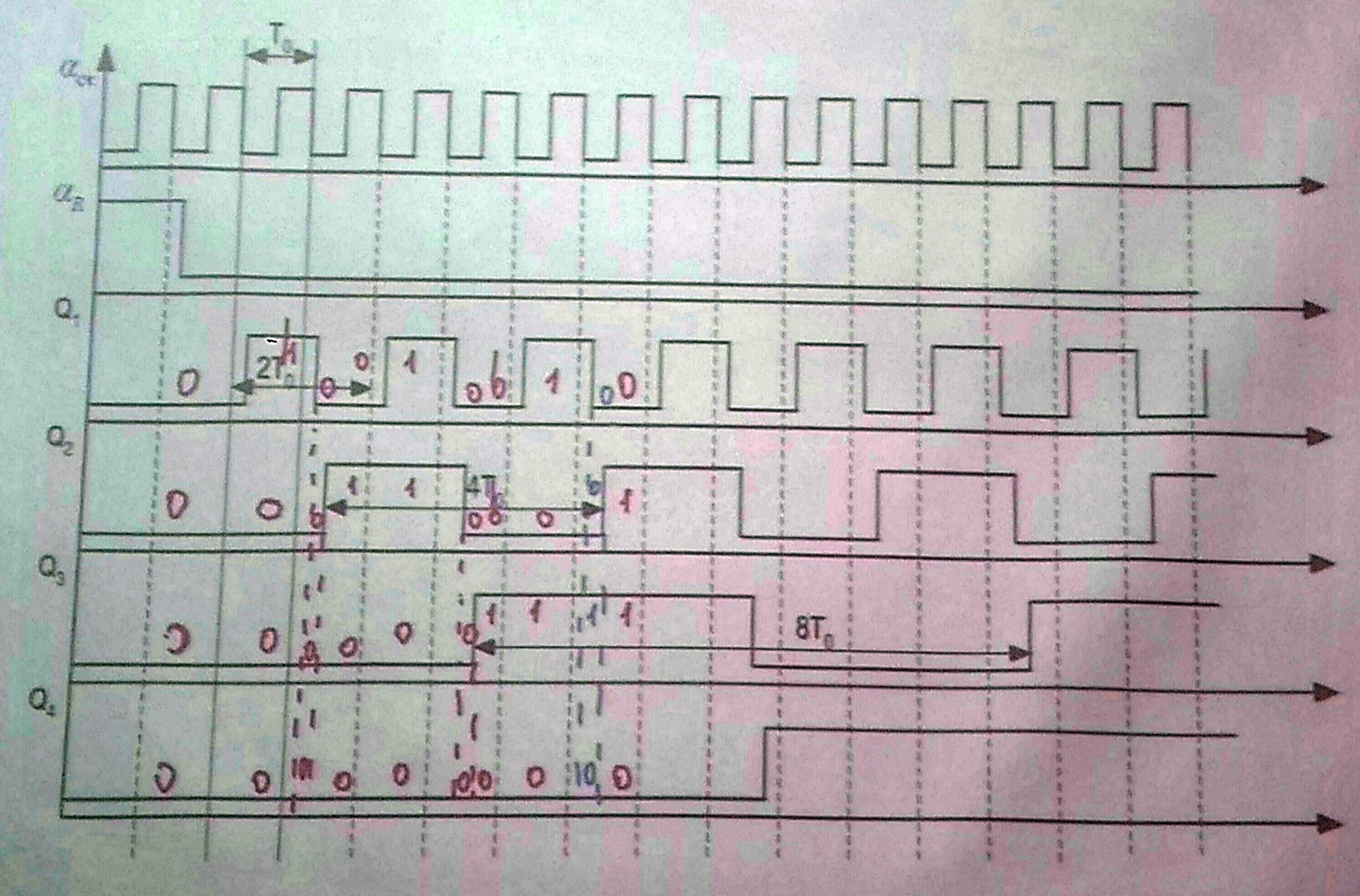

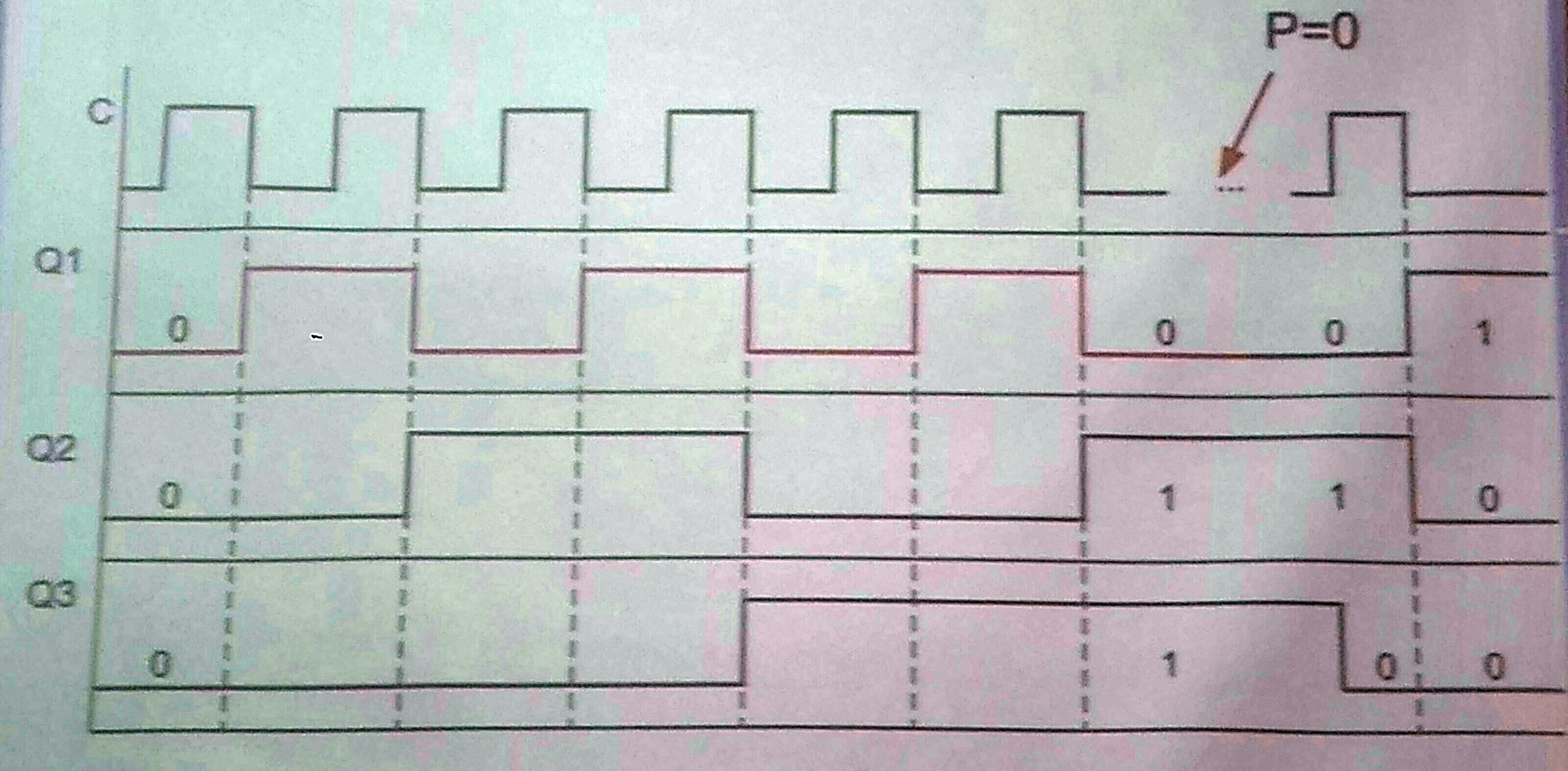

Для определения возможности переключения режима счёта в тот момент, когда счётчик ещё не достиг своего конечного состояния, рассмотрим временные диаграммы функционирования четырёхразрядного реверсивного счётчика, реализованного на триггерах, переключающихся по заднему фронту.

УГО:

Из временной диаграммы видно, что между моментами переключения счётчика по заднему фронту синхроимпульса, при этом на выходе формируются сигналы в соответствии с таблицей функционирования счётчика можно наблюдать кратковременные интервалы времени, при которых на выходе счётчика формируются сигналы, не соответствующие его таблице переключения.

Так, после состояния 0101 (5) на выходе формируется кратковременный сигнал 0100 (4).

И лишь затем на выходе формируется 0110 (6).

Эти кратковременные интервалы времени возникают из-за задержки в переключении триггеров.

Таким образом, для того чтобы с выхода счётчика не снять ложную информацию, необходимо чтобы внутри счётчика завершились все переходные процессы.

Так функционируют все суммирующие и вычитающие счётчики.

Вернёмся к вопросу реверса асинхронных счётчиков на ходу.

Для этого рассмотрим временную диаграмму суммирующего счётчика, который в момент, когда значение на выходе 110 (6), переключается в режим вычитания, то есть приходит сигнал реверса R=0.

В момент, когда счётчик досчитал до 6, приходит сигнал реверса R=0.

Первый триггер на сигнал реверса не реагирует и переключается по заднему фронту следующего счётного импульса из “0” в “1”.

На входе T2 перепад из “0” в “1”, на который он не реагирует и сигнал на выходе сохраняется.

Переключение происходит опять же по заднему фронту синхроимпульса.

При подаче сигнала реверса на входе T3 формируется перепад из “1” в “0”, так как T3=!Q2 при R=0.

В результате третий триггер переключается из “1” в “0” и на выходе счётчика формируется сигнал 010 (2) вместо необходимой пятёрки (101) по приходе следующего счётного импульса на выходе счётчика 001 (1).

Таким образом, при подаче сигнала реверса, в момент когда счётчик не досчитал до своего конечного значения, выполнять нельзя, так как мы не знаем, в какое состояние перейдёт счётчик по приходе следующего счётного импульса. Как видно из примера, из состояния 6 счётчик переходит в 2, а затем - в 1, что говорит о неверном функционировании счётчика при выполнении реверса на ходу.

Достоинства и недостатки асинхронных счётчиков

Асинхронные счётчики имеют невысокое быстродействие и могут использоваться лишь в том случае, когда триггеры обладают малыми задержками переключений.

Их удобно строить лишь при небольшой разрядности счётчиков и на быстрых триггерах.

Могут использоваться в качестве делителей частоты, так как каждый разряд счётчика уменьшает частоту в два раза.

Низкая помехозащищенность, так как помеха, пришедшая на вход одного из триггеров проходит на все его выходы.

Недостаток: невозможность реверса счётчиков на ходу.

Асинхронный (суммирующий) двоично-десятичный счётчик

|

№ |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

|

10 |

1 |

0 |

1 |

0 |