ВУЗ: Сибирский государственный университет телекоммуникаций и информатики

Категория: Методичка

Дисциплина: Информатика

Добавлен: 06.11.2018

Просмотров: 412

Скачиваний: 14

Федеральное агенство связи

Бурятский филиал федерального государственного образовательного бюджетного учреждения высшего профессионального образования

«Сибирский государственный университет телекоммуникаций и информатики» в г. Улан Удэ

Факультет «Телекоммуникаций»

Кафедра «Высшей математики и общепрофессиональных дисциплин»

Домашняя контрольная работа (ДКР) и методические рекомендации

Дисциплины

Вычислительная техника и информационные технологии (ВТ и ИТ)

Название дисциплины

Форма обучения: заочная

Квалификация: «бакалавр»

Направление : Инфокоммуникационные технологии и системы связи «210700»

Курс: 2

ДКР разработала: Полещук Т.В.

Улан-Удэ

2014г.

Предисловие

Цель изучения дисциплины «ВТ и ИТ» состоит в формировании базовой подготовки студентов в области цифровых устройств и микропроцессорных систем для изучения профилирующих дисциплин, развития навыков практического использования цифровой техники в современных системах связи. Цифровые методы обработки информации и цифровые устройства широко применяются в системах передачи и распределения информации, в телевизионной и радиовещательной аппаратуре.

При изучении дисциплины используются материалы курсов: «Дискретная математика»; «Электроника»; «Информатика».

В свою очередь дисциплина «ВТ и ИТ» является базой для дисциплин, связанных с вопросами аппаратной реализации устройств систем связи.

Задания для ДКР

Разработать, используя микросхемы малой (ИМС) и средней (СИС) степени интеграции, распределитель импульсов, формирующий на выходе из каждых N входных импульсов поступающих от ГТИ на его вход, заданную последовательность импульсов. Привести спецификацию используемых ИМС. На построенной схеме поставить логические уровни «0» и «1» для указанного входного импульса с целью описания работы схемы построенного распределителя импульсов.

Исходные данные приведены в таблице 1.

Таблица 1. Варианты задания.

-

№ варианта

Серия ИМС

Число выходных импульсов N

Номера выходных импульсов распределителя

Входной импульс

0

К155

17

1; 6; 11; 16

3

1

К555

18

2; 7; 12; 17

6

2

КР1533

19

3; 8; 13; 18

9

3

К155

20

4; 9; 14; 19

13

4

КР1531

21

5; 10; 15; 20

15

5

К564

22

6; 11; 16; 21

18

6

530

23

7; 12; 17; 22; 1

19

7

К555

24

8; 13; 18; 23; 2

20

8

КР1533

25

9; 14; 19; 24; 3

21

9

КР1531

26

10; 15; 20; 25; 4

22

Методические рекомендации по выполнению ДКР

-

Поскольку в задании указана система элементов для построения распределителя импульсов, то необходимо по номеру серии ИМС назвать ее (ЭСЛ; ТЛЛ; ТТЛШ; КМОП), и дать краткую характеристику.

-

Кратко отметить особенности (достоинства и недостатки) указанной в задании серии ИМС. Привести основные параметры (напряжение питания (Uпит); быстродействие; потребляемая мощность (P); кодирование логических уровней «0» и «1»; базовый логический элемент и др.)

-

Возможны несколько схемных вариантов построения распределителя, например: двоичный счетчик с мультиплексором, двоичный счетчик с дешифратором, на основе сдвигового регистра и др.

Рассмотрим в качестве примера реализацию на основе двоичного счетчика и дешифратора.

План работы:

-

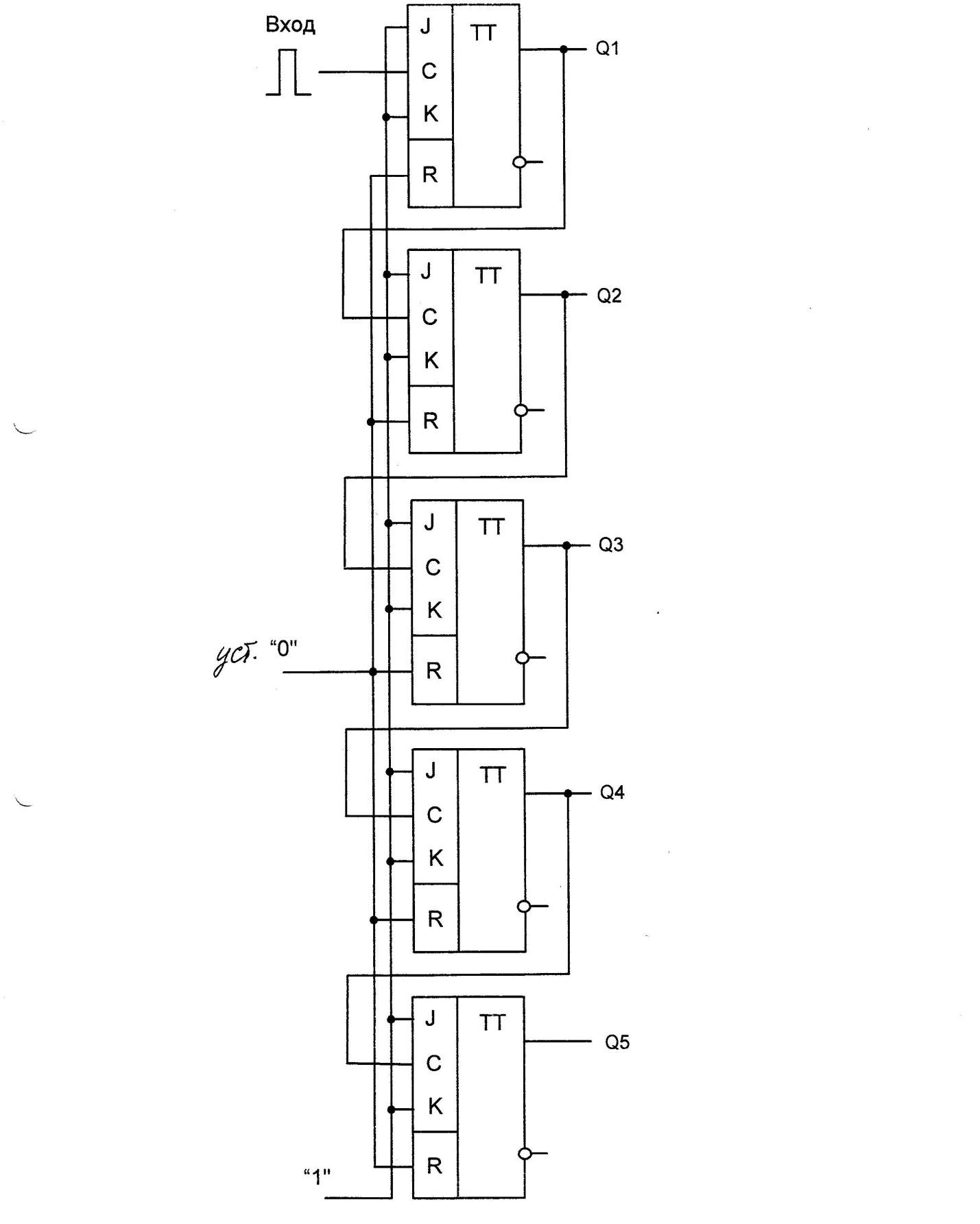

Выбрать ИМС JK-триггера и, учитывая что один триггер реализует один разряд счетчика, построить схему многоразрядного счетчика (рисунок1). Привести таблицу его работы.

-

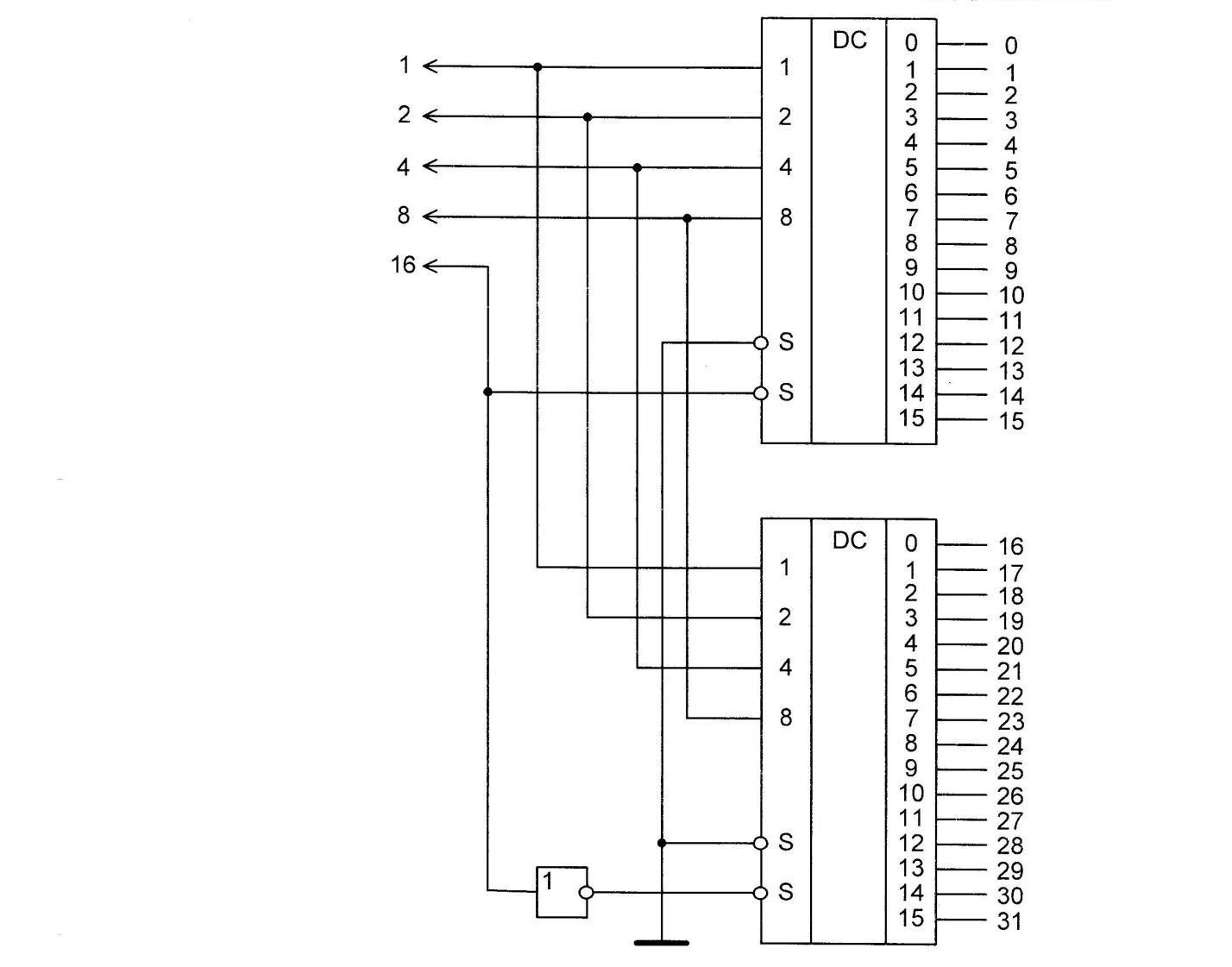

Выбрать ИМС дешифратора и построить дешифратор на 32 выхода (рисунок 2)

-

Построить схему распределителя импульсов, предусмотрев на его выходе выходную логику ( на базе логических элементов ), для обеспечения заданной выходной последовательности импульсов.

-

Описать работу схемы распределителя импульсов в соответствии с заданием.

-

Привести спецификацию используемых ИМС. Пример в таблице 3.

Отсюда, схема счётчика имеет вид:

Рис.1. Схема счётчика на JК-триггерах

К выходам счётчика подключается дешифратор, состоящий из двух дешифраторов по 16 выходов в каждом (рис.2.)

Рис. 2. Схема дешифратора

Каждый дешифратор выполнен на микросхеме К155ИДЗ, которая имеет четыре адресных входа 1, 2, 4, 8, два инверсных входа стробирования S, и 16 выходов 0-15. Если хотя бы на одном из входов стробирования S лог. 1, то независимо от состояний входов на всех выходах микросхемы формируется лог.1. По входам стробирования S дешифраторы соединены элементом ИЛИ (DD4.1) К155ЛН1. Наличие двух входов стробирования существенно расширяет возможности использования микросхем. Из двух микросхем К155ИДЗ, дополнительным одним инвертором, можно собрать дешифратор на 32 выхода, на четырех микросхемах можно собрать дешифратор на 64 выхода.

Спецификация

Таблица 3.

-

№ п/п

Обозначение

Наименование

1

DD1

К555ТВ6

2

DD2

3

DD3

4

DD4

К155ЛН1

5

DD5

К155ИДЗ

6

DD6

7

DD7

КР531ЛЕ7

8

DD8

К155ЛЕЗ

Перечень литературы

Таблица 4

|

Авторы |

Наименование |

Год издания |

|

Калабеков Б.А. |

Цифровые устройства и микропроцессорные системы. М. «Горячая линия- Телеком» |

2005 |

|

Калабеков Б.А. |

Микропроцессоры и их применение в системах передачи и обработки сигналов М. «Радио и связь» |

1998 |

|

Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. |

Аналоговая и цифровая электроника М. «Горячая линия- Телеком» |

2005 |

|

Под редакцией Якубовского С.В. |

Интегральные микросхемы М. «Радио и связь» |

1989 |

|

Нефедов А.В. |

Справочник интегральные микросхемы и их зарубежные аналоги М. КУБК-а |

1996 |