Добавлен: 30.06.2023

Просмотров: 112

Скачиваний: 4

СОДЕРЖАНИЕ

1.2 Архитектура симметричных мультипроцессоров UMA с общей шиной

1.3 Мультипроцессоры UMA с координатными коммутаторами

1.4 Мультипроцессоры UMA c многоступенчатые коммутаторными сетями

2 Архитектура многопроцессорных вычислительных систем

2.1 Векторно-конвейерные суперкомпьютеры

2.2 Симметричные мультипроцессорные системы

2.3 Системы с массовым параллелизмом

3. Разработка имитационной модели мультипроцессорной системы

1.5 Мультипроцессоры NUMA

Для мультипроцессоров UMA с единственной общей шиной пределом является несколько десятков CPU, в то время как мультипроцессорам с координатным коммутатором или коммутирующей сетью требуется большое количество (дорогого) аппаратного обеспечения, и количество CPU в них не намного больше. Чтобы создать мультипроцессор с числом CPU, превосходящем 100, нужно чем-то пожертвовать.[15]

Обычно в жертву приносится идея одинакового времени доступа ко всем модулям памяти. Таким образом, получается концепция мультипроцессоров NUMA (NonUniform Memory Access — неоднородный доступ к памяти). Как и UMA, мультипроцессоры NUMA предоставляют единое адресное пространство для всех CPU, но в отличие от UMA-машин доступ к локальной памяти у них быстрее, чем к удаленным модулям. Таким образом, все программы, написанные для UMA, будут работать и на мультипроцессорах NUMA, но их производительность будет ниже, чем на машинах UMА при той же тактовой частоте CPU.

У машин NUMA есть три ключевые характеристики, которые, взятые вместе, отличают их от других мультипроцессоров.

1. Для всех нейтральных CPU имеется единое адресное пространство.

2. Доступ к удаленным модулям памяти осуществляется при помощи специальных команд CPU.

3. Доступ к удаленным модулям памяти медленнее, чем к локальной памяти.

В том случае, если доступ к удаленной памяти не является скрытым (то есть кэширование не применяется), система называется NC-NUMA (No Caching NUMА — система NUMA без кэширования). При наличии когерентных кэш-модулей система называется CC-NUMA (Cache-Coherent NUMA — система NUMA с когерентным кэшированием).

Наиболее популярным подходом при построении больших мультипроцессоров CC-NUMA в настоящий момент является каталоговый мультипроцессор - поддержание БД, в которой содержится информация о том, где располагается каждая строка кэша и ее состояние. При обращении к строке кэша БД получает запрос на поиск этой строки и выдает ее состояние («чистая» или «грязная»). Поскольку запросы этой БД направляются на каждой команде CPU, обращающейся к памяти, эта база должна храниться в крайне быстром специальном аппаратном устройстве, способном выдавать ответ за долю цикла шины.[16]

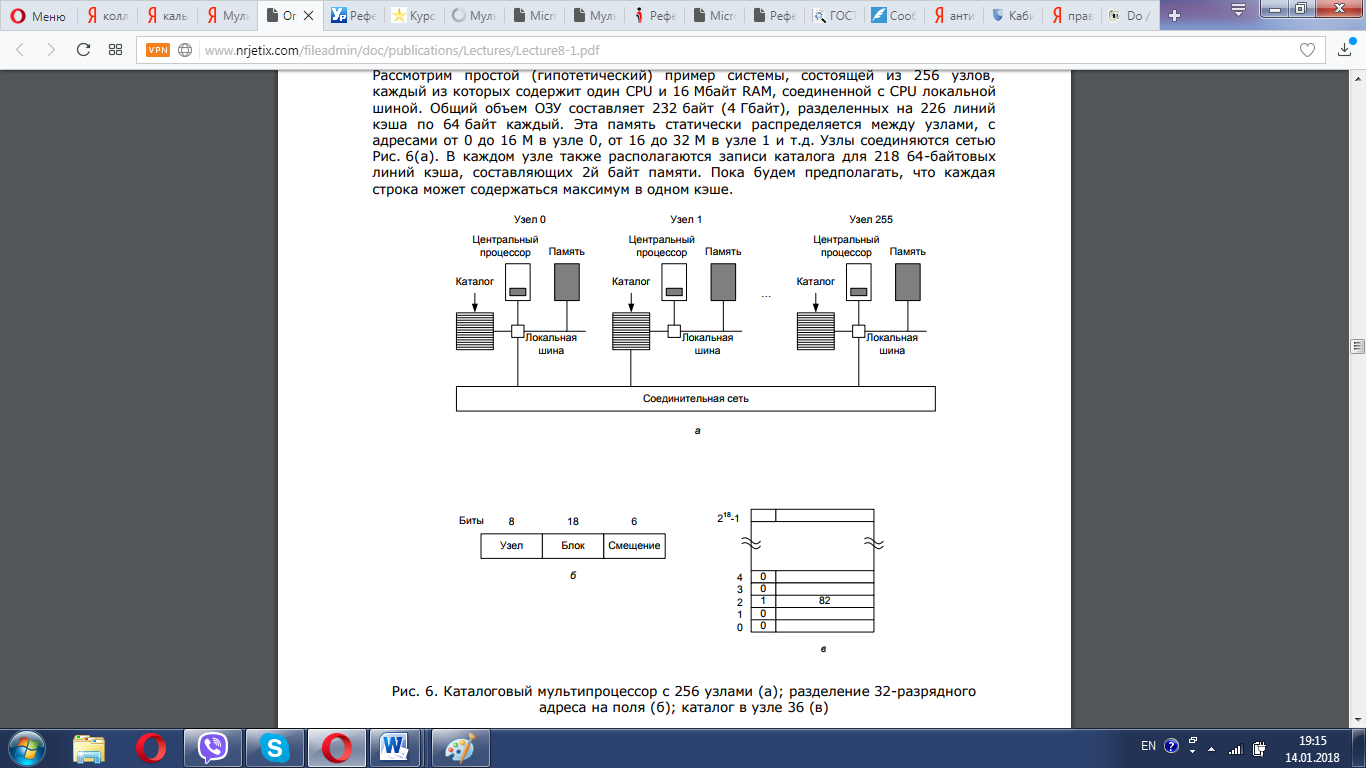

Рассмотрим простой (гипотетический) пример системы, состоящей из 256 узлов, каждый из которых содержит один CPU и 16 Мбайт RAM, соединенной с CPU локальной шиной. Общий объем ОЗУ составляет 232 байт (4 Гбайт), разделенных на 226 линий кэша по 64 байт каждый. Эта память статически распределяется между узлами, с адресами от 0 до 16 М в узле 0, от 16 до 32 М в узле 1 и т.д. Узлы соединяются сетью рис. 5(а). В каждом узле также располагаются записи каталога для 218 64-байтовых линий кэша, составляющих 2й байт памяти. Пока будем предполагать, что каждая строка может содержаться максимум в одном кэше.

Рисунок 5 - Каталоговый мультипроцессор с 256 узлами (а); разделение 32-разрядного адреса на поля (б); каталог в узле 36 (в)

Чтобы понять, как работает каталог, рассмотрим выполнение команды LOAD CPU 20 с обращением к строке кэша. Сначала CPU, издающий команду LOAD, передает ее аргумент своему диспетчеру памяти (MMU), который преобразует его в физический адрес, например 0x24000108. MMU расщепляет этот адрес на три части, показанные на рис. 5(б). В десятичном виде эти части выглядят как узел 36, строка 4 и смещение 8. MMU видит, что CPU обращается к слову памяти в узле 36, а не в узле 20, поэтому он посылает узлу 36 по соединительной сети сообщение с запросом, находится ли эта строка в кэше, и если да, то где.[17]

Когда запрос приходит по соединительной сети на узел 36, он направляется к аппаратуре каталога. Это аппаратное обеспечение обращается по индексу в свою таблицу, состоящую из 218 записей, по одной для каждой строки кэша, и достает из нее запись 4. Как видно на рис. 6(в), эта строка не является кэшированной, поэтому аппаратное обеспечение достает ее из локальной памяти, отправляет узлу 20 и отмечает в таблице, что теперь эта строка кэширована в узле 20.

Теперь рассмотрим пример другого запроса. На этот раз у узла 36 запрашивается строка 2. Как показано на рис. 6(в), эта строка кэширована в узле 82. При этом аппаратное обеспечение изменяет запись, отмечая, что теперь эта строка находится в узле 20, и посылает узлу 82 команду переслать эту строку узлу 20, а также пометить свою строку кэша как недействительную. Обратите внимание, что даже так называемый «мультипроцессор с общей памятью» вынужден пересылать большое количество сообщений незаметно для верхнего уровня.

Посчитаем, сколько памяти занимают каталоги, У каждого узла есть 16 Мбайт ОЗУ и 218 9-битовых записей для учета этой памяти. Таким образом, накладные расходы на содержание каталога составляют около 9x2 18 бит, что составляет около 1,76 % от 16 Мбайт. Эта величина не так уж велика и должна быть приемлемой (хотя для каталога должна использоваться высокоскоростная память, что увеличивает ее стоимость). Даже при 32-байтовых строках кэша накладные расходы на содержание каталога будут около 4 %. При 128-байтовых строках кэша накладные расходы не будут превышать 1 %.[18]

Ограничение такой схемы заключается в том, что строка может быть кэширована только в одном узле. Чтобы позволить кэшировать строку одновременно в нескольких узлах, нам потребуется какой-то способ обнаружения всех этих строк чтобы, например, пометить их все как недействительные или чтобы обновить их при записи.

2 Архитектура многопроцессорных вычислительных систем

2.1 Векторно-конвейерные суперкомпьютеры

Первый векторно-конвейерный компьютер Cray-1 появился в 1976 году. Архитектура его оказалась настолько удачной, что он положил начало целому семейству компьютеров. Название этому семейству компьютеров дали два принципа, заложенные в архитектуре процессоров:

- конвейерная организация обработки потока команд;

- введение в систему команд набора векторных операций, которые позволяют оперировать с целыми массивами данных.[19]

Длина одновременно обрабатываемых векторов в современных векторных компьютерах составляет, как правило, 128 или 256 элементов. Очевидно, что векторные процессоры должны иметь гораздо более сложную структуру и по сути дела содержать множество арифметических устройств. Основное назначение векторных операций состоит в распараллеливании выполнения операторов цикла, в которых в основном и сосредоточена большая часть вычислительной работы. Для этого циклы подвергаются процедуре векторизации с тем, чтобы они могли реализовываться с использованием векторных команд. Как правило, это выполняется автоматически компиляторами при изготовлении ими исполнимого кода программы. Поэтому векторно-конвейерные компьютеры не требовали какой-то специальной технологии программирования, что и явилось решающим фактором в их успехе на компьютерном рынке. Тем не менее, требовалось соблюдение некоторых правил при написании циклов с тем, чтобы компилятор мог их эффективно векторизовать.[20]

Исторически это были первые компьютеры, к которым в полной мере было применимо понятие суперкомпьютер. Как правило, несколько векторно-конвейерных процессоров (2-16) работают в режиме с общей памятью (SMP), образуя вычислительный узел, а несколько таких узлов объединяются с помощью коммутаторов, образуя либо NUMA, либо MPP систему.[21] Типичными представителями такой архитектуры являются компьютеры CRAY J90/T90, CRAY SV1, NEC SX-4/SX-5. Уровень развития микроэлектронных технологий не позволяет в настоящее время производить однокристальные векторные процессоры, поэтому эти системы довольно громоздки и чрезвычайно дороги. В связи с этим, начиная с середины 90-х годов, когда появились достаточно мощные суперскалярные микропроцессоры, интерес к этому направлению был в значительной степени ослаблен. Суперкомпьютеры с векторно-конвейерной архитектурой стали проигрывать системам с массовым параллелизмом.[22] Однако в марте 2002 г. корпорация NEC представила систему Earth Simulator из 5120 векторно-конвейерных процессоров, которая в 5 раз превысила производительность предыдущего обладателя рекорда – MPP системы ASCI White из 8192 суперскалярных микропроцессоров. Это, заставило многих по-новому взглянуть на перспективы векторно-конвейерных систем.

2.2 Симметричные мультипроцессорные системы

Характерной чертой многопроцессорных систем SMP архитектуры является то, что все процессоры имеют прямой и равноправный доступ к любой точке общей памяти. Первые SMP системы состояли из нескольких однородных процессоров и массива общей памяти, к которой процессоры подключались через общую системную шину. Однако очень скоро обнаружилось, что такая архитектура непригодна для создания сколь либо масштабных систем. Первая возникшая проблема – большое число конфликтов при обращении к общей шине. Остроту этой проблемы удалось частично снять разделением памяти на блоки, подключение к которым с помощью коммутаторов позволило распараллелить обращения от различных процессоров. Однако и в таком подходе неприемлемо большими казались накладные расходы для систем более чем с 32-мя процессорами.[23]

Современные системы SMP архитектуры состоят, как правило, из нескольких однородных серийно выпускаемых микропроцессоров и массива общей памяти, подключение к которой производится либо с помощью общей шины, либо с помощью коммутатора (рис. 6).

Рисунок 6 - Архитектура симметричных мультипроцессорных систем

Наличие общей памяти значительно упрощает организацию взаимодействия процессоров между собой и упрощает программирование, поскольку параллельна программа, работая в едином адресном пространстве. Однако за этой кажущейся простотой скрываются большие проблемы, рисующие системам этого типа. Все они так или иначе, связаны с оперативной памятью. Дело в том, что в настоящее время даже в однопроцессорных системах самым узким местом является оперативная память, скорость работы которой значительно отстала от скорости работы процессора. Для того чтобы сгладить этот разрыв, современные процессоры снабжаются скоростной буферной памятью (кэш-памятью), скорость работы которой значительно выше, чем скорость работы основной памяти. В качестве примера приведем данные измерения пропускной способности кэш-памяти и основной памяти для персонального компьютера на базе процессора Pentium III 1000 Мгц. В данном процессоре кэш-память имеет два уровне:

- L1 (буферная память команд) – объем 32 Кб, скорость обмена 9976 Мб/сек;

- L2 (буферная память данных) – объем 256 Кб, скорость обмена 4446 Мб/сек.

В тоже время скорость обмена с основной памятью составляет всего 255 к. Это означает что для 100% согласованности со скоростью работы процессора (1000 Мгц) скорость работы основной памяти должна быть в 40 раз выше. [24]

Очевидно, что при проектировании многопроцессорных систем эти проблемы еще более обостряться. Помимо хорошо известной проблемы конфликтов при обращении к общей шине памяти возникла и новая проблема, связанная с иерархической структурой организации памяти современных компьютеров. В многопроцессорных системах, построенных на базе микропроцессоров со встроенной кэш-памятью, нарушается принцип равноправного доступа к любой точке памяти.[25] Данные, находящиеся в кэш-памяти некоторого процессора, недоступны для других процессоров. Это означает, что осе каждой модификации копии некоторой переменной, находящейся в кэш-памяти какого-либо процессора, необходимо производить синхронную модификацию самой этой переменной, расположенной в основной памяти. С большим или меньшим успехом эти проблемы решаются в рамках общепринятой в настоящее время архитектуры ccNUMA (cache coherent Non Uniform Memory Access). В этой архитектуре память физически распределена, но логически общедоступна.[26] Это, с одной стороны, позволяет работать с единым адресным пространством, а, с другой, увеличивает асштабируемось систем. Когерентность кэш-памяти поддерживается на апаратном уровне, что не избавляет, однако, от накладных расходов на ее поддержание. В тличие от классических SMP систем память становится трехуровневой:

- кэш-память процессора;

- локальная оперативная память;

- удаленная оперативная память.

Время обращения к различным уровням может отличаться на порядок, что сильно усложняет написание эффективных параллельных программ для таких систем.

Перечисленные обстоятельства значительно ограничивают возможности по наращиванию производительности ccNUMA систем путем простого увеличения числа процессоров. Тем не менее, эта технология позволяет в настоящее время создавать системы, содержащие до 256 процессоров с общей производительностью порядка 200 млрд. операций в секунду. Системы этого типа серийно производятся многими компьютерными фирмами как многопроцессорные серверы с числом процессоров от 2 до 128 и прочно удерживают лидерство в классе малых суперкомпьютеров.[27] Типичными представителями данного класса суперкомпьютеров являются компьютеры SUN StarFire 15K, SGI Origin 3000, HP Superdoe. Хорошее описание одной из наиболее удачных систем этого типа – компьютера Superdome фирмы Hewlett-Packard можно найти в книге [3]. Неприятным свойством SMP систем является то, что их стоимость растет быстрее, чем производительность при увеличении числа процессоров в системе. Кроме того, из-за задержек при обращении к общей памяти неизбежно взаимное торможение при параллельном выполнении даже независимых программ.