ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 28.07.2024

Просмотров: 357

Скачиваний: 0

СОДЕРЖАНИЕ

Государственный Комитет Российской федерации

Общие требования к выполнению лабораторных работ

1.2. Осциллограф (Oscilloscope)

1.3. Измеритель ачх и фчх (Bode Plotter)

1.4. Функциональный генератор (Function Generator)

Лабораторная работа № 1. Полупроводниковые диоды

Рабочие схемы, таблицы и порядок выполнения работы

Рабочие схемы, таблицы и порядок выполнения работы

Исследование вольт-амперных характеристик

Биполярного транзистора в схеме с

Общим эмиттером и полевого транзистора в схеме с общим истоком.

Лабораторная работа 4. Исследование тиристоров и управляемых выпрямителей

Лабораторная работа №5 Исследование работы усилительного каскада на биполярном транзисторе

Типовая амплитудно-частотная характеристика приведена на рис.5

Лабораторная работа №9 Исследование работы избирательных усилителей в цепи обратной связи

Исследование работы комбинационных логических схем Теоретическое введение

Задание

Исследовать логические элементы со следующим соответствием сигналов:

0В – сигнал 0 – низкий потенциал

1В – сигнал 1 – высокий потенциал

По соответствующим схемам заполнить таблицы истинности

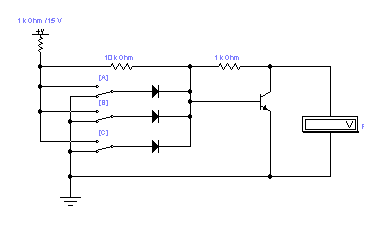

Рабочие схемы

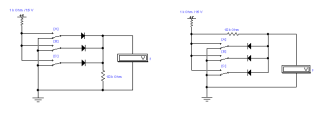

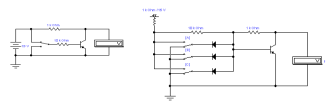

Логический элемент ИЛИ Логический элемент И

Логический элемент НЕ Логический элемент ИЛИ-НЕ

Логический

элемент И-НЕ

Порядок выполнения работы

1. Ознакомиться с теоретическим введением, законспектировать в лабораторную тетрадь, нарисовать исследуемые схемы и заготовить таблицы.

2. Для схем И, ИЛИ, И-НЕ, ИЛИ-НЕ – таблица 1

|

С |

В |

А |

F |

|

1 |

1 |

1 |

|

|

1 |

1 |

0 |

|

|

1 |

0 |

1 |

|

|

1 |

0 |

0 |

|

|

0 |

1 |

1 |

|

|

0 |

1 |

0 |

|

|

0 |

0 |

1 |

|

|

0 |

0 |

0 |

|

Для схемы НЕ таблица 2

|

А |

F |

|

1 |

0 |

|

0 |

1 |

Таблица 1 Таблица 2

Соберите схему согласно заданию.

Подавайте входные сигналы на точки А,В, С в соответствии с таблицей, запишите получившееся значение функции.

Подготовьте ответы на контрольные вопросы

Контрольные вопросы и задания

Что такое Булева алгебра

Основные логические операции

Логическое умножение, таблица истинности

Логическое сложение, таблица истинности

Логическое отрицание

Найти значения выражений: (А+В)*С, где А=В=1, С=0

(А+В)+С,

(А+В)*(В*С), где А=1, В=С=0

(А+В)*(А+С), где А=С=1, В=0

А+(В*А)+(В*С), где В=С=1, А=0

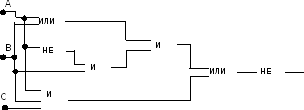

Построить таблицу истинности для приведенных выше выражений, построить электронные схемы.

Для приведенных выходных значений функции вывести исходную ФАЛ, построить электронные схемы (табл. 4).

Табл. 4

|

№ |

Значения функции |

|||||||

|

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

|

2 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

3 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

4 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

5 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

Выведите ФАЛ по приведенной схеме (рис. 3).

Единицы измерения информации

Два подхода к измерению информации, отличия

Как представляется информация на ПК

Почему ПК работает в двоичной системе

Для чего нужна восьмеричная, шестнадцатеричная системы счисления

Формулы перевода из различных систем счисления

ЛАБОРАТОРНАЯ РАБОТА №12

Исследование работы комбинационных логических схем Теоретическое введение

Комбинационной схемой называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов. В комбинационных схемах используются логические элементы, выпускаемые в виде интегральных схем. В этот класс входят интегральные схемы дешифраторов, шифраторов, мультиплексоров, демультиплексоров и сумматоров.

Шифратором или кодером называется комбинационное логическое устройство для преобразования чисел из десятичной системы счисления в двоичную. Основное применения шифратора в цифровых системах – это введение первичной информации с клавиатуры.

Дешифратором

или декодером называется комбинационное

логическое устройство для преобразования

чисел из двоичной системы счисления в

десятичную. Дешифратор имеет

информационных входов, которым

соответствует

информационных входов, которым

соответствует выходов. Каждой комбинации логических

уровней на входах будет соответствовать

активный уровень на одном из

выходов. Каждой комбинации логических

уровней на входах будет соответствовать

активный уровень на одном из выходов. Обычно число входов равно 2, 3

или 4. Если числу входов

выходов. Обычно число входов равно 2, 3

или 4. Если числу входов соответствует

соответствует выходов, то дешифратор называют

полным, если меньше, то неполным. На рис.

1 де-шифратор имеет три входа, активным

уровнем является уровень логического

нуля. На входыС,

В, А можно

подать такие комбинации уровней:

000,001,010,011, ... 111, всего 8 комбинации.

выходов, то дешифратор называют

полным, если меньше, то неполным. На рис.

1 де-шифратор имеет три входа, активным

уровнем является уровень логического

нуля. На входыС,

В, А можно

подать такие комбинации уровней:

000,001,010,011, ... 111, всего 8 комбинации.

Рис. 12.1

Схема

имеет восемь выводов ( ,

, ,

, ,

, ,

, ,

, ,

, ,

, ),

на одном из них формируется низкий

потенциал или логический нуль, на

остальных – высокий или логическая

единица. Номер

),

на одном из них формируется низкий

потенциал или логический нуль, на

остальных – высокий или логическая

единица. Номер этого выхода определяется по известной

формуле перехода от системы счисления

с меньшим основанием к системе счисления

с большим основанием, где произвольное

число

этого выхода определяется по известной

формуле перехода от системы счисления

с меньшим основанием к системе счисления

с большим основанием, где произвольное

число в позиционной системе счисления с

основанием

в позиционной системе счисления с

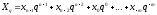

основанием можно представить в виде полинома:

можно представить в виде полинома:

так

как мы имеем три входа – А,

В, С, то есть

,

то

,

то

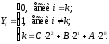

Например,

если на входы подана логическая комбинация

011, что соответствует в десятичной

системе счисления числу 3, то сигнал

логического нуля установится на выходе

номер три ( ),

что можно подсчитать по формуле:

),

что можно подсчитать по формуле: ,

а все остальные выходы будут иметь

сигнал логической единицы. Этот принцип

формирования выходного сигнала можно

описать следующим образом:

,

а все остальные выходы будут иметь

сигнал логической единицы. Этот принцип

формирования выходного сигнала можно

описать следующим образом:

Уровень

сигнала на выходе

можно описать выражением ФАЛ:

можно описать выражением ФАЛ:

ФАЛ для остальных выходов:

Кроме информационных входов А, В, С, дешифраторы имеют дополнительные управляющие входы G. Сигналы на этих входах разрешают работу дешифратора или переводят его в пассивное состояние, при котором, независимо от сигналов на информационных входах, на выходе все сигналы имеют уровень логической единицы.

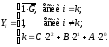

Разрешающий вход дешифратора может быть прямым и инверсным. У дешифраторов с прямым входом разрешения активным является уровень логической единицы, дешифраторов с инверсным входом разрешения активным является уровень логического нуля. На рис. 1 представлен дешифратор с одним инверсным управляющим входом. Принцип формирования выходного сигнала в этом дешифраторе с учетом сигнала управления описывается следующим образом:

У

дешифраторов с несколькими входами

управления функция разрешения

представляет собой логическое произведение

всех разрешающих сигналов управления.

Например, для дешифраторов 74138 с одним

прямым входом управления

и двумя инверсными

и двумя инверсными и

и (рис. 2) функция разрешения имеет вид:

(рис. 2) функция разрешения имеет вид: .

.