Файл: 1. Контактные явления в полупроводниковых приборах, p n переход, виды полупроводниковых диодов 3.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 29.10.2023

Просмотров: 132

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

Устройство биполярного транзистора, его характеристики и схемы включения

Устройство полевого транзистора с p – n переходом, его характеристики и схемы включения

Установка режимов работы транзисторов

Работа транзисторного усилителя в режиме А, его достоинства и недостатки

Влияние ООС на примере усилителя, охваченного последовательной ООС по напряжению

Примеры применения ОУ для выполнения математических операций

RC – генераторы синусоидальных сигналов

Структурная схема и описание работы источника вторичного электропитания

Сумматор. Сумматор параллельного типа

Сумматор. Сумматор параллельного типа

Р

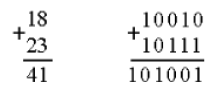

ассмотрим принцип работы сумматора, для чего вначале сравним суммирование двух десятичных и двоичных чисел А + В:

ассмотрим принцип работы сумматора, для чего вначале сравним суммирование двух десятичных и двоичных чисел А + В:По внешнему виду правила одинаковы:

-

Сложение производится поразрядно - от младшего разряда к старшему (справа налево); -

В младшем разряде вычисляется сумма младших разрядов слагаемых А{) и В(). Эта сумма в данной системе счисления может быть записана однозначным числом S(), либо двухзначным числом P0S0. Число Р{) называют переносом в старший разряд или просто переносом. -

Во всех последующих разрядах находится сумма этих разрядов слагаемых Ai и Bi при Рi-1≠0 к этой сумме добавляется перенос: результат сложения в i-м разряде записывается в виде Si или РiSi,.

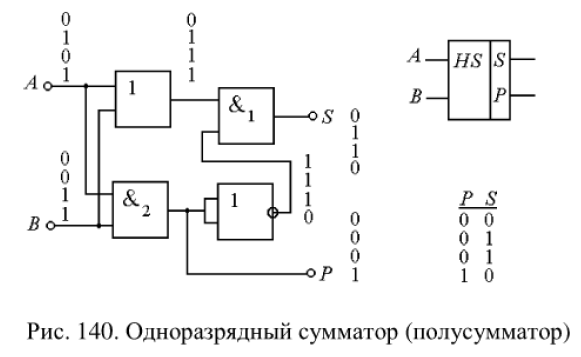

Сумматор - это устройство, которое разряд за разрядом (начиная с младшего разряда) складывает «единицы» и «нули» первого и второго слагаемых. Таблица истинности для сложения двух одноразрядных двоичных чисел имеет вид:

| А | В | р | 5 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Первые три операции может выполнить один элемент ИЛИ. Что же касается четвертого сочетания слагаемых (1 + 1), то здесь необходим перенос «единицы» в следующий разряд. Это реализуется с помощью нескольких логических элементов.

Работу одноразрядного сумматора иллюстрирует рис. 140.

Оба слагаемых подаются не только на элемент ИЛИ, но одновременно еще и на элемент И2, а с него на элемент НЕ. На рис. 140 показаны в столбик все возможные варианты суммирования двух одноразрядных чисел. В первых трех случаях (0+0, 0+1, 1+0) элемент И2 не переключается, так как на его входе нет двух единичных импульсов. А значит, в этих случаях на выходе инвертора будут логические единицы. Если на вход сумматора одновременно поступают два единичных импульса (1 + 1), то на выходе сумма (5) будет ноль, а перенос Р примет значение логической единицы.

Рассмотренная схема может использоваться только для суммирования в младшем разряде и называется поэтому полусумматором. Полусумматор обозначается на схемах буквами HS.

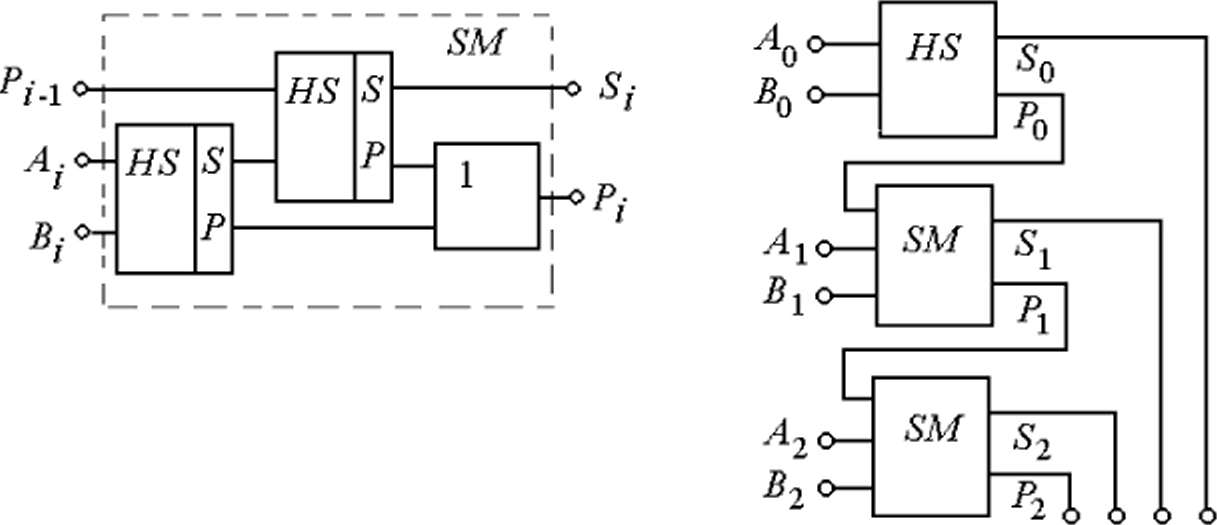

При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса. Такое устройство называется полным сумматором (рис. 141).

Соединяя полусумматоры и полные сумматоры определенным образом, получают устройства для сложения нескольких разрядов двоичных чисел. Например, трехразрядный сумматор показан на рис. 142.

На выходах Sq — S2 формируется двоичный код суммы двух трехразрядных чисел А2А1А0 и В2В1В0, а на выходе Р2 формируется сигнал переноса, так как при сложении двух трехразрядных двоичных чисел может получиться четырехразрядное число.

Одноразрядные, двухразрядные и четырехразрядные сумматоры выпускают в виде интегральных микросхем. С целью наращивания разрядности суммируемых чисел микросхемы соединяют последовательно, для чего выход переноса соединяют с входом переноса микросхем, принадлежащим более высоким разрядам. У микросхемы, суммирующей младшие разряды чисел, вход переноса следует соединить с общим проводом

Рис. 141. Полный сумматор Рис. 142. Трехразрядный сумматор

Приведенный на рис. 142 сумматор называется параллельным, поскольку информационные сигналы поступают на все входы одновременно. В параллельном сумматоре для каждого двоичного разряда нужен отдельный сумматор.

- 1 ... 6 7 8 9 10 11 12 13 14

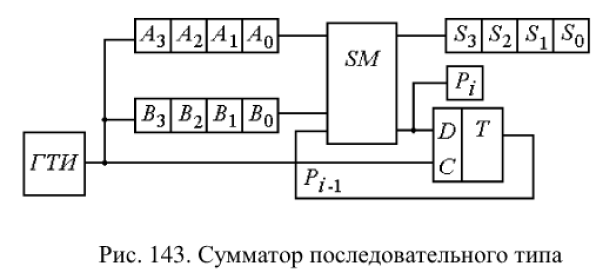

Сумматор последовательного типа

Другой способ сложения используется в последовательном сумматоре. Четырехразрядное суммирующее устройство последовательного действия, использующее регистры сдвига, можно представить в виде, показанном на рис. 143

В этой схеме имеются два регистра сдвига, в которые предварительно записываются значения суммируемых чисел А и В. Выходная сумма S накапливается в сдвиговом регистре суммы.

Н

а первом тактовом импульсе, поступающем с генератора тактовых импульсов (ГТИ) складываются значения младшего разряда (A0 и В0), сумма S0 появляется в регистре суммы, а на выходе переноса Р; появляется сигнал (символ) переноса Р{) («1» или «О»). На втором тактовом импульсе складываются значения следующего разряда и перенос Р0, поступающий на вход Рi-1 сумматора от D -триггера, обеспечивающего задержку сигнала переноса на время прихода очередного разряда. Результат S1, записывается в регистр суммы, а на выходе переноса формируется новый сигнал Р1. На третьем тактовом импульсе складываются разряды A2, В2 и перенос Р1. На четвертом (последнем) тактовом импульсе процесс суммирования завершается.

а первом тактовом импульсе, поступающем с генератора тактовых импульсов (ГТИ) складываются значения младшего разряда (A0 и В0), сумма S0 появляется в регистре суммы, а на выходе переноса Р; появляется сигнал (символ) переноса Р{) («1» или «О»). На втором тактовом импульсе складываются значения следующего разряда и перенос Р0, поступающий на вход Рi-1 сумматора от D -триггера, обеспечивающего задержку сигнала переноса на время прихода очередного разряда. Результат S1, записывается в регистр суммы, а на выходе переноса формируется новый сигнал Р1. На третьем тактовом импульсе складываются разряды A2, В2 и перенос Р1. На четвертом (последнем) тактовом импульсе процесс суммирования завершается.-

Мультиплексоры и демультиплексоры

Мультиплексором называется комбинационное устройство, имеющее несколько входов и один выход. Причем выход соединяется с одним из входов (Х(), X1...) в зависимости от двоичного кода на отдельных адресных входах (А, В).

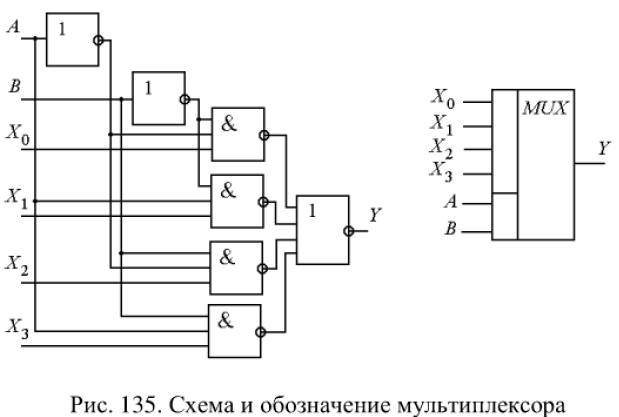

Пример мультиплексора на 4 входа показан на рис. 135. На схемах он обозначается буквами MUX.

При А = В = 0 двоичная информация на выход У поступает с информационного входа Х0, при А = 1, В

= 0 - со входа Х1 и т.д.

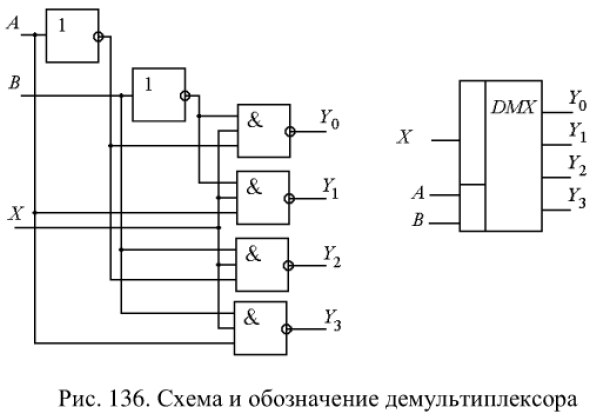

Обратная задача решается с помощью демультиплексора, подключающего один вход к одному из нескольких информационных выходов. Пример демультиплексора на 4 выхода показан на рис. 136.

С помощью адресного кода, подаваемого на входы А В, вход X подключается к одному из выходов Y{) - Y3

-

Шифраторы и дешифраторы

Шифратор - это комбинационное устройство, преобразующее единичный сигнал на одном из входов в двоичный код, соответствующий номеру входа.

Пример построения шифратора для преобразования десятичных чисел от 0 до 9 в двоичный код на логических элементах ИЛИ приведен на рис. 137.

На любой из входов шифратора Х0...Х9 через контакты можно подать напряжение, соответствующее логической единице. При этом на выходе шифратора формируется цифровой код, соответствующий номеру замкнутого контакта. На схемах шифратор обозначается буквами CD (от английского слова coder).

Дешифратором называют комбинационное устройство, преобразующее двоичный код на входе в единичный сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. На схемах дешифратор обозначается буквами DC (от английского слова decoder).

Дешифратор широко используется в качестве преобразователя двоичного кода в десятичный. Рассмотрим примера его применения в схеме распределителя импульсов.

На основе счетчика и дешифратора строится распределитель импульсов, который поочередно формирует импульсы на его выходах. Схема распределителя импульсов на 7 выходов и временные диаграммы его работы приведены на рис. 138. Тактовые импульсы поступают на вход трехразрядного двоичного счетчика СТ. Двоичный код на выходе счетчика преобразуется дешифратором DC в импульс на одном из его выходов.