Файл: Курсовой проект по дисциплине Электроника тема работы Проектирование аналогоцифрового преобразователя.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 05.12.2023

Просмотров: 149

Скачиваний: 4

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

1. Расчет преобразователя уровней (ПУ).

1.3. Принцип действия базовых логических элементов

1.7. Выбор биполярного транзистора для ПУ

1.9. Расчёт мощности, потребляемой преобразователем уровней от источника питания

1.10. Расчёт передаточной характеристики преобразователя уровней для номинальных параметров

1.11. Схема преобразователя уровней и его временная диаграмма

1.12. Интегральный аналог преобразователя уровней

2. АЦП двойного интегрирования

2.1. Схема АЦП двойного интегрирования К572ПВ2

3. Расчёт генератора тактовых импульсов для АЦП

3.4. Описание работы генератора тактовых импульсов

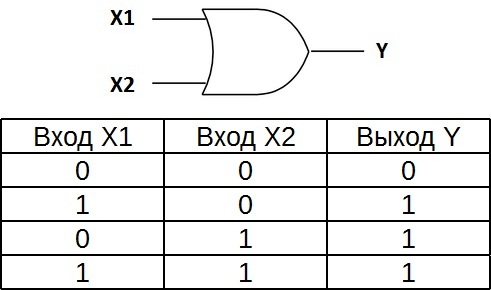

Рис. 8 – Таблица истинности для элемента «2ИЛИ»

Таблица истинности для элемента «2ИЛИ» показывает, что для появления на выходе логической единицы, достаточно чтобы логическая единица была на первом входе ИЛИ на втором входе. Если логические единицы будут сразу на двух входах, на выходе также будет единица.

На западных схемах значок элемента «ИЛИ» имеет закругление на входе и закругление с заострением на выходе. На отечественных схемах — прямоугольник с символом «1».

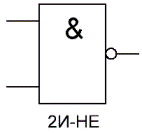

Логический элемент «И-НЕ» - конъюнкция (логическое умножение) с отрицанием, NAND

Рис. 8 – Логический элемент «И-НЕ»

«И-НЕ» - логический элемент, выполняющий над входными данными операцию логического сложения, и затем операцию логического отрицания, результат подается на выход. Другими словами, это в принципе элемент «И», дополненный элементом «НЕ». На рисунке приведено условное обозначение логического элемента «2И-НЕ».

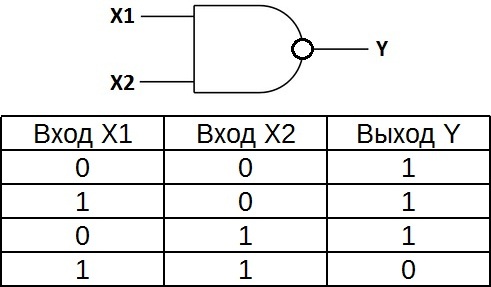

Рис. 9 – Таблица истинности для элемента «И-НЕ»

Таблица истинности для элемента «И-НЕ» противоположна таблице для элемента «И». Вместо трех нулей и единицы — три единицы и ноль. Элемент «И-НЕ» называют еще «элемент Шеффера» в честь математика Генри Мориса Шеффера, впервые отметившего значимость этой логической операции в 1913 году. Обозначается как «И», только с кружочком на выходе.

На основе указанных типов элементов и элемента «отрицание» (НЕ, NOT), можно построить логическую схему практически любого уровня сложности.

1.4. Логические элементы КМОП серии К561 (К1561)

КМОП – микросхемы на комплементарных полевых транзисторах структуры МОП (металл-оксид-полупроводник)

Тип логики: КМОП (комплементарные МОП структуры)

Состав серии: более 100 типов микросхем комбинационной и последовательностной логики

Напряжение питания: Uип = 3…15В

Входной ток уровня логического нуля:

Входной ток уровня логической единицы:

Выходной ток уровня логического нуля:

Выходной ток уровня логической единицы:

Выходное напряжение логического нуля (при напряжении питания 10В):

Выходное напряжение логической единицы (при напряжении питания 10В):

Время задержки переключения с нуля на единицу:

Время задержки переключения с единицы на ноль:

Коэффициент разветвления по выходу:

Температурный диапазон:

Зарубежный аналог: серия CD4000

1.5. Логические элементы ТТЛШ серии К1533.

ТТЛШ – (транзисторно-транзисторная логика с диодами Шоттки) – разновидность цифровых логических микросхем, построенных на основе биполярных транзисторов и резисторов.

Тип логики: ТТЛШ.

Состав серии: более 150 типов микросхем комбинационной и последовательностной логики

Напряжение питания: ????и.п.= 5В ±5%

Входной ток уровня логического нуля: ????ВХ0 ≤ -0,2 мА

Входной ток уровня логической единицы: ????ВХ1 ≤ 20 мкА

Выходной ток уровня логического нуля: ????ВЫХ0 ≤ 8 мА

Выходной ток уровня логической единицы: ????ВЫХ1 ≤ 0,4 мА

Выходное напряжение логического нуля: ????ВЫХ0 ≤ 0,5 В

Выходное напряжение логической единицы: ????ВЫХ1 ≥ 2,5 В

Время задержки переключения на вентиль: ????зд ≤ 4.5нс

Коэффициент разветвления по выходу: ????раз=20

Температурный диапазон: ????= −10…+70℃

Зарубежный аналог: серия 74(54)ALS

1.6. Выбор схемы преобразователя уровней.

На рис. 10 представлена простейшая схема преобразования уровней элемента ТТЛ-типа в уровни элемента КМОП-типа (ТТЛ->КМДП). Первый каскад (на транзисторе VT1) выполняет функции обычного инвертора-усилителя. Второй каскад (на транзисторах VT2 и VT3) представляет собой обычный комплементарный МОП – каскад (вход КМОП ЛЭ).

Чтобы этот каскад работал нормально, значения пороговых напряжений Uпор транзисторов VT2 и VT3 должны удовлетворять условию:

Uпор VT2 + Uпор VT3 ≤ Е

Рис. 10 – Схема ПУ из ТТЛ в КМДП

Схема ПУ работает следующим образом. При Uвх = U0ттл транзистор VT1 находится в отсечке, и на выходе первого каскада U= +E. Транзистор VT2 заперт, а VТ3 открыт, на выходе схемы Uвых ≈ 0 ≤ U0кмоп.

При Uвх = U1ТТЛ транзистор VT1 отпирается до насыщения благодаря базовому току, равному (UBX — eэб)/Rб, где eэб — напряжение на прямосмещенном р-n-переходе база-эмиттер насыщенного транзистора (для кремниевых транзисторов eэб

0,6…0,8 В). Остаточное напряжение между коллектором и эмиттером насыщенного

транзистора Uкэн близко к нулю (для кремниевых транзисторов Uкэн составляет 0,15… 0.3 В), и транзистор VT2 открыт, a VT3 заперт. Следовательно, Uвых ≈ + E > U0кмоп.

Недостаток схемы — одновременное использование и биполярных, и полевых транзисторов в одной микросхеме, что затрудняет ее изготовление в виде интегральной полупроводниковой схемы, хотя эту схему ПУ можно изготовить в виде гибридной микросборки либо в дискретном виде.

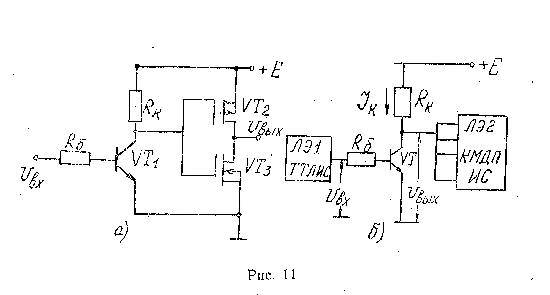

В случае, когда ставится задача спроектировать ПУ ТТЛ - КМОП для расположенных на одной и той же плате конкретных ТТЛ ИС и КМОП ИС с заданными нагрузочной способностью ПУ, частотой переключения ПУ и температурным диапазоном работы ПУ, схема преобразователя может быть упрощена и содержать только один биполярный транзистор VT и резисторы RK и Rб (рис 11).

Рис. 11 – Структура ПУ с одним биполярным транзистором

Если Uвх = U0ттл < eэб, то VT находится в режиме отсечки и напряжение на его коллекторе (равное напряжению на выходе ПУ), получается практически равным напряжению питания +Е и заведомо выше уровня лог. 1 КМОП - элементов, т. е. Uкмоп:

Uвых= E - (nI1вх КМОП + Iкб о)*Rk ≥ U1 КМОП

где п — нагрузочная способность ПУ;

I1вх КМОП – ток, обусловленный в основном защитными диодами, подключенными к затворным входам транзисторов (р—n - переходы, смещенные в обратном направлении);

Iкб о – обратный ток коллекторного перехода транзистора VT.

Токи I1вх КМОП, Iкб о - обычно очень малы и составляют десятые доли микроампера.

Если UBX = Uттл, то целесообразно обеспечить насыщение транзистора VT со степенью насыщения S=1,2÷2, при которой достигается компромисс между временами включения транзистора и временами рассасывания и спада, т. е.

Iб = S Iб н= S

Iк н - ток коллектора насыщенного транзистора VT.

Ток Iб, протекающий в цепи базы транзистора VT при условии, что UВX = U1ттл, равен

Iб =

Вычисленный по формуле ток Iб не должен превышать выходной ток

I1вых ттл, обеспечиваемый ТТЛ - элементом в состоянии логической 1, а также не должен быть больше максимально допустимого тока Iб макс выбранного транзистора VT, т. е.:

Iб ≤ I1вых ттл

Iб < Iб макс

В коллектор насыщенного транзистора VT втекает ток Iкн , который складывается из тока Iк, протекающего через резистор Rк, и n входных токов I°вхкмоп КМОП-элемента, т. е.:

Iкн=IRk + n I°вх кмоп=

Ток Iкн, найденный по формуле, должен быть меньше максимально допустимого тока I

кмакс выбранного транзистора VT, т. е.:

Iк н < Iк макс

Напряжение UВЫХ на выходе ПУ, равное потенциалу на коллекторе насыщенного транзистора VT UKэн не должно превышать уровня лог. 0 КМОП элемента U°кмоп:

UBых= UKэн ≤ U°кмоп