Файл: Курсовой проект по дисциплине Электроника тема работы Проектирование аналогоцифрового преобразователя.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 05.12.2023

Просмотров: 152

Скачиваний: 4

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

1. Расчет преобразователя уровней (ПУ).

1.3. Принцип действия базовых логических элементов

1.7. Выбор биполярного транзистора для ПУ

1.9. Расчёт мощности, потребляемой преобразователем уровней от источника питания

1.10. Расчёт передаточной характеристики преобразователя уровней для номинальных параметров

1.11. Схема преобразователя уровней и его временная диаграмма

1.12. Интегральный аналог преобразователя уровней

2. АЦП двойного интегрирования

2.1. Схема АЦП двойного интегрирования К572ПВ2

3. Расчёт генератора тактовых импульсов для АЦП

3.4. Описание работы генератора тактовых импульсов

5. Список использованной литературы

1. В. Л. Шило «Популярные цифровые микросхемы», Челябинск, «Металлургия», 1989

2. А-Й. К. Марцинкявичус и др. «Быстродействующие интегральные микросхемы ЦАП и АЦП», Москва, «Радио и Связь», 1988

3. С. В. Якубовский, Л.И. Ниссельсон Справочник «Цифровые и аналоговые интегральные микросхемы», Москва «РАДИО И СВЯЗЬ»1990г.

4. www.analog.com сайт компании Analog Devices

5. www.ti.com сайт компании Texas Instruments

6. www.mouser.com сайт компании Mouser

7. А.В.Шилейко « Электронные устройства железнодорожной автоматики, телемеханики и связи», Москва «транспорт» 1989г.

Дополнение

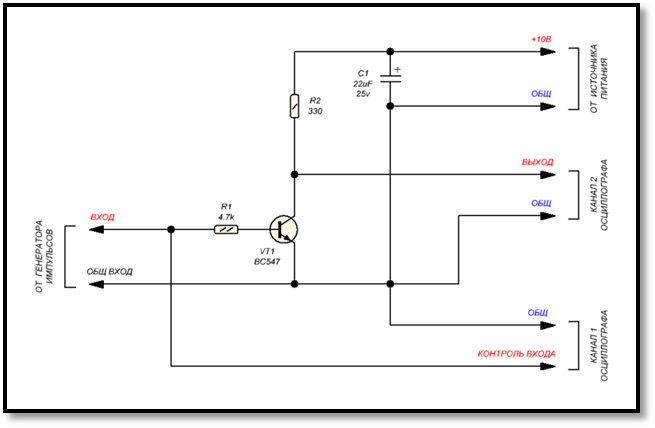

В процессе выполнения курсовой работы, мною было выполнено практическое макетирования схемы преобразователя уровня ТТЛ - КМОП на биполярном транзисторе в ключевом режиме. Принципиальная схема собранного макета приведена на рис. 1.

Рис. 1 - Принципиальная схема макета преобразователя уровня

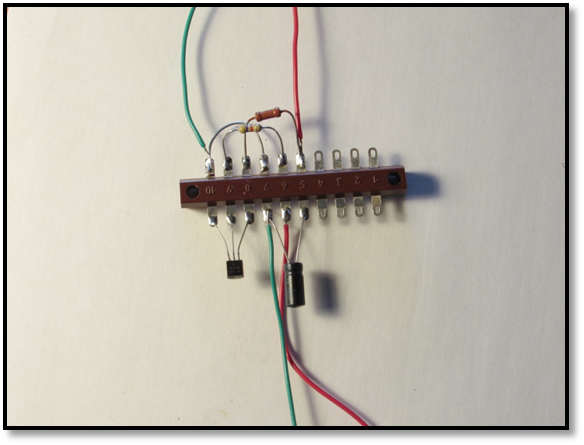

Внешний вид собранного макета приведен на рис.2

Рис. 2 - Вид макета преобразователя уровня

Для исследования работы макета применялись следующие приборы:

-

Стабилизированный источник питания HY3002 -

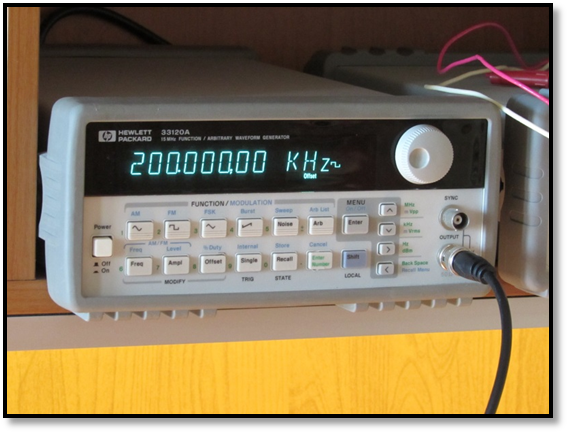

Генератор сигналов произвольной формы Hewlett Packard 33120A -

Многоканальный цифровой осциллограф Hewlett Packard 54645D

Сигнал на выходе генератора устанавливался в стандартных ТТЛ-уровнях (лог.0 = 0.4В, лог. 1 = 2.5В). Этот сигнал подавался одновременно на вход макета ПУ и на вход 1-го канала осциллографа. Сигнал с выхода ПУ подавался на вход 2-го канала осциллографа. Частота повторения импульсов устанавливалась согласно задания курсовой работы – 200 кГц, а скважность – равной 5 (рис. 3).

Рис. 3

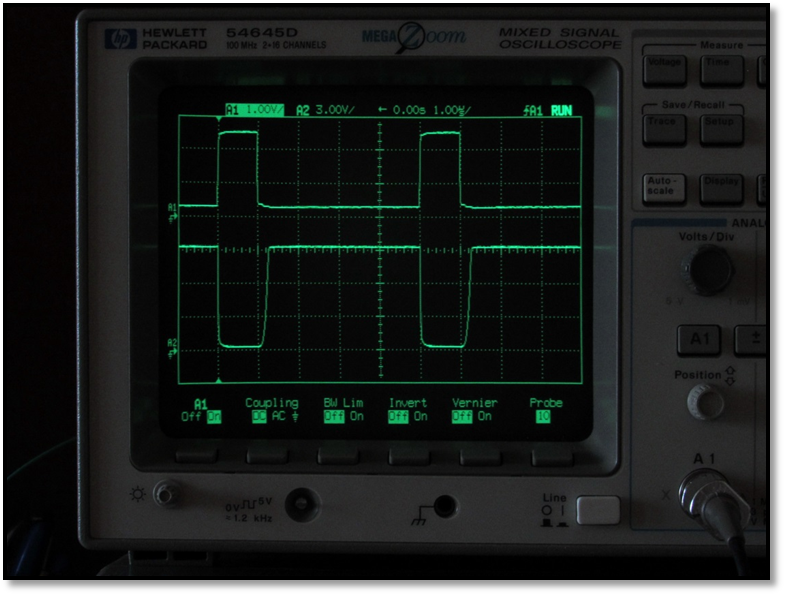

Осциллограммы сигналов на входе (верхний луч, канал 1) и на выходе (нижний луч, канал 2) приведены на рис. 4.

Рис. 4 – Осциллограммы входного и выходного сигналов ПУ

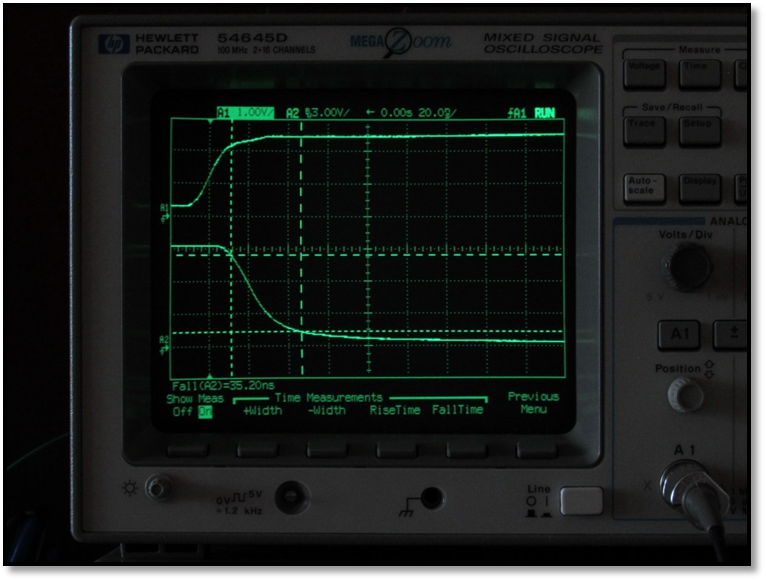

При исследовании работы макета были произведены измерения времен спада и нарастания импульса на выходе ПУ. Результат измерения времени спада импульса, т.е. перехода выхода ПУ из лог. 1 в лог. 0 приведен на осциллограмме на рис. 5. Длительность перехода составила 35 нс.

Рис. 5 – Измерение длительности перехода лог.1 – лог.0 на выходе ПУ

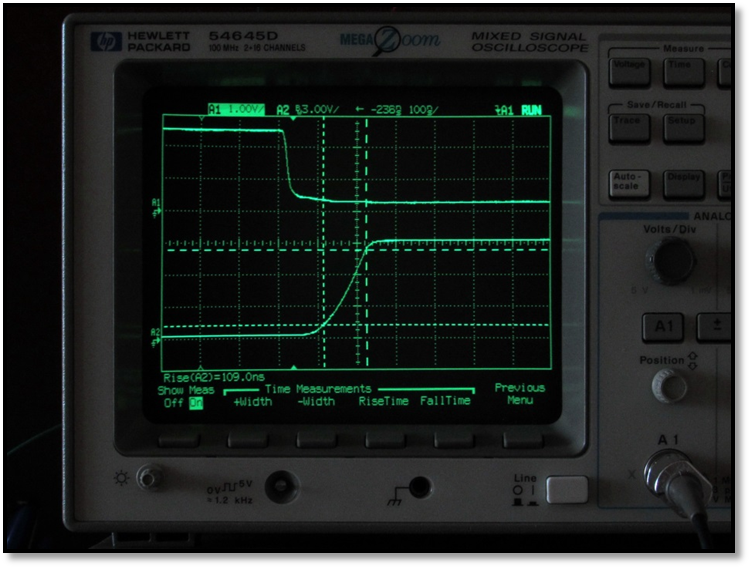

Результат измерения времени нарастания импульса, т.е. перехода выхода ПУ из лог. 0 в лог. 1 приведен на осциллограмме на рис. 6. Длительность перехода составила 109 нс. Также на осциллограмме хорошо видна задержка начала запирания транзистора, вызванная его выходом из режима насыщения.

Рис. 6 – Измерение длительности перехода лог.0 – лог.1 на выходе ПУ

Выполненное практическое макетирование и инструментальное исследование работы каскада преобразователя уровня показало достаточное практическое соответствие параметров физического устройства и результатов расчетов, а также более-менее приемлемое соответствие практических результатов результатам моделирования в Multisim.