Файл: 1. Структура внешнего интерфейса 2 Алгоритм производимых операций 3.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 25.10.2023

Просмотров: 33

Скачиваний: 3

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Содержание

1.Структура внешнего интерфейса 2

2.Алгоритм производимых операций 3

3.Структурная схема микроЭВМ 6

4.Функциональные схемы блоков микроЭВМ 9

5.Временные диаграммы 11

Заключение 16

-

Структура внешнего интерфейса

Рисунок 1 – Структура внешнего интерфейса

Пояснения к схеме представлены в таблице 1.

| Таблица 1 – Обозначения внешнего интерфейса | |

| Термин | Обозначение |

| ВС | внешняя среда |

| МЭВМ | микроЭВМ |

| ГОТ | готовность |

| ШД | шина данных |

| СС | слово сообщение |

| КОП | код операции в битах |

| СД | сопровождение данных |

| ПД | принятие данных |

| СП | сообщение передано |

| ПС | принятие сообщения |

| СПР | сопровождение результата |

| ПР | подтверждение результата |

-

Алгоритм производимых операций

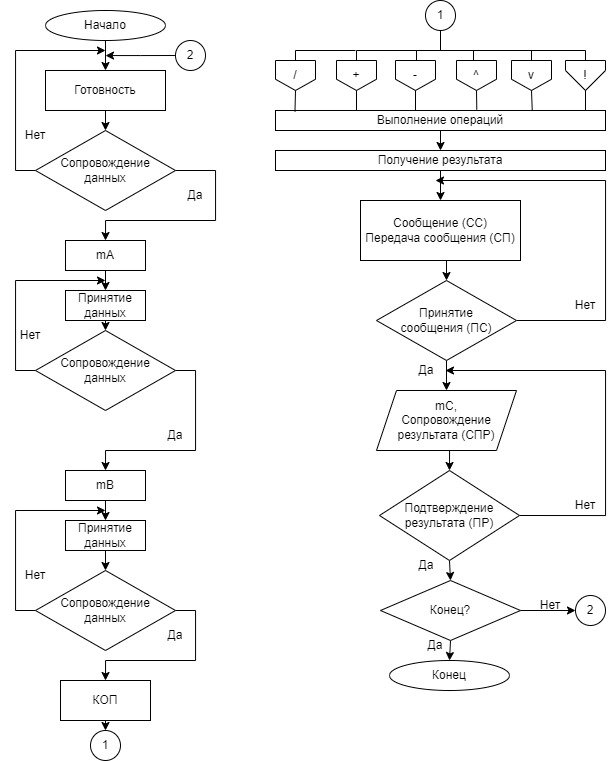

Рисунок 2 – Общая схема алгоритма

Рисунок 2 – Деление

Рисунок 4 – Сложение

Рисунок 5 – Вычитание

-

Структурная схема микроЭВМ

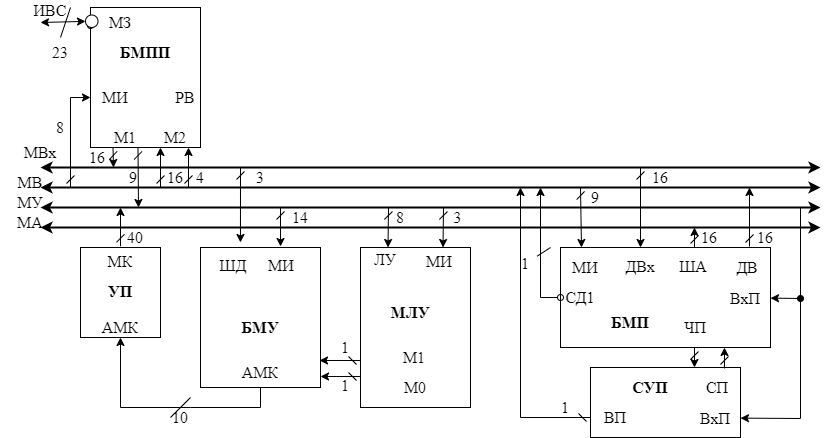

Рисунок 6 – Структурная схема микроЭВМ

Пояснения к структурной схеме представлены в таблице 2.

| Таблица 2 – Обозначения к структурной схеме микроЭВМ | |

| Термин | Обозначение |

| ИВС | интерфейс внешней системы |

| МВх | магистраль входа |

| МВ | магистраль выхода |

| МУ | магистраль управления |

| МА | магистраль адреса |

| БМП | блок микропроцессора |

| МИ | микроинструкция |

| ВхП | вход переноса |

| ЧП | частичный перенос |

| СД1 | сдвиг одинарного слова |

| ДВх | данные входные |

| ША | шина адреса |

| ДВ | данные выходные |

| СУП | схема ускоренного переноса |

| ВП | вход переноса |

| СП | секционный перенос |

| БМУ | блок микропрограммного управления |

| МЛУ | мультиплексор логических условий |

| ЛУ | логические условия |

| МК | микрокоманды |

| АМК | адрес микрокоманды |

| БМПП | блок магистральный приёмо-передатчиков |

| РВ | разрешение выдаче М3 |

На рисунке 6 представлена структурная схема микроЭВМ, где представлена операционная часть (ОЧ), включающая в себя блок микропроцессоров БМП со схемой ускоренного переноса СУП. Управляющая часть (УЧ) содержит блок микропрограммного управления БМУ, мильтиплексор логических условий МЛУ и управляющую память УП.

На базе блока магистральных приёмопередатчиков БМПП реализована интерфейсная часть, данный блок позволяет обеспечивать обмен между интерфейсом внешней системы ИВС и внутренним четырехмагистральным техническим интерфейсом. ИВС подключен к двунаправленной магистрали М3 БМПП. Выходная внутренняя магистраль М1 БМПП соединена с магистралями МВх и МУ, по ней осуществляется ввод данных, когда выполняется операция (передача сигнала) сопровождения данных СД. Входная внутренняя магистраль М2 в блоке БМПП подключена к магистралям МВ и МУ и предназначена для вывода данных, сигналов готовности ГТ и подтверждения данных ПД.

Блок БМП связан своими шинами входных данных ДВх, выходных данных ДВ, адреса ША, входа микроконструкции МИ с соответствующими магистралями МВх, МВ, МА, МУ. К магистрали управления МУ так же подключены выход инверсного сигнала сдвига одинарного слова !СД1 в качестве логического условия и вход переноса ВхП арифметико-логического устройства (АЛУ), который соединен и с аналогичным входом СУП. Выходной перенос ВП в данном блоке формируется на соответствующей выходной шине СУП и подключается в качестве второго логического условия к МУ. Вход переноса ВП вырабатывается на основе частичных переносов ЧП, которые поступают с процессорных секций блока БМП. Одновременно с ВП в СУП формируются и межсекционные переносы СП, которые ускоряют процесс суммирования в блоке БМП.

Функционирование управляющей части (УЧ) в микрокомандном цикле работы микроЭВМ осуществляется путем использования блока БМУ, где на выходной шине адреса микрокоманды АМК формирует код адреса текущей микрокоманды поступающий на одноименный вход УП. На выходную шину МК УП считывается соответсвующая микрокоманда. Данная микрокоманда содержит микроконструкции всех функциональных устройств и блоков, а так же сигналы взаимодействия с внешней средой при обмене через ИВС.

В таблице 3 приведен пример формата микрокоманды для рассматриваемой микроЭВМ.

| Таблица 3 – Пример форматов микрокоманд для микроЭВМ | |||||||||

| Формат микрокоманды | |||||||||

| 39 | 38 | 37 | 36 | 35 | 34…27 | 26…13 | 12…10 | 9…1 | 0 |

| СПР | СП | ПД | ГОТ | РВ | МИ БМПП | МИ БМУ | МИ МЛУ | МИ БМП | ВхП |

В таблице 4 представлена нумерация шин магистрали управления.

| Таблица 4 – Нумерация шин для магистрали управления | |

| № шины | Функциональное назначение |

| 1 | Сигнал входного переноса |

| 2-10 | Микроинструкция БМП |

| 11-13 | Микроинструкция МЛУ |

| 14-27 | Микроинструкция БМУ |

| 28-35 | Микроинструкция БМПП |

| 36 | Сигнал разрешения выдачи РВ |

| 37 | ГОТ |

| 38 | Сигнал подтверждения данных |

| 39 | Сигнал сообщения подтверждения |

| 40 | Сигнал сопровождения результата |

| 41 | Выход сдвига |

-

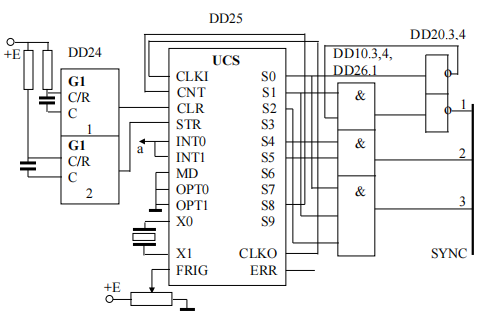

Функциональные схемы блоков микроЭВМ

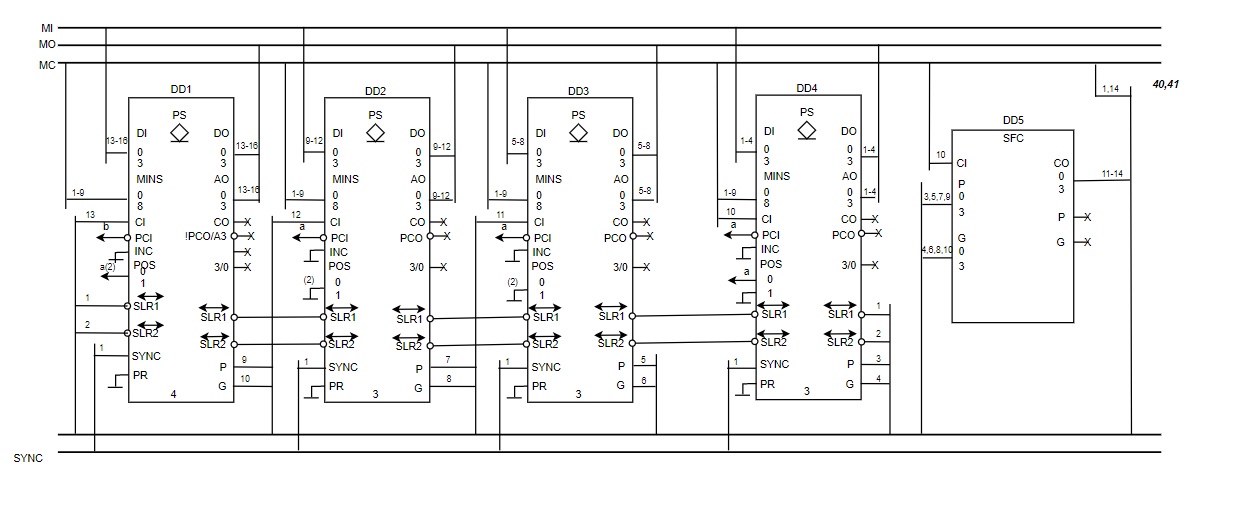

На рисунке 7 представлена функциональная схема АЛУ БМП

Рисунок 7 – Функциональная схема АЛУ БМП

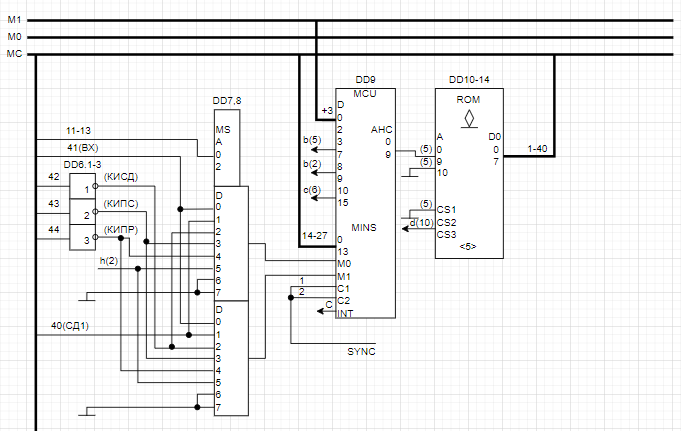

На рисунке 8 представлена функциональная схема управляющей части

Рисунок 8 – Функциональная схема БМУ

На рисунке 9 представлена функциональная схема интерфейсного блока БМПП.

Рисунок 9 – Функциональная схема БМПП

-

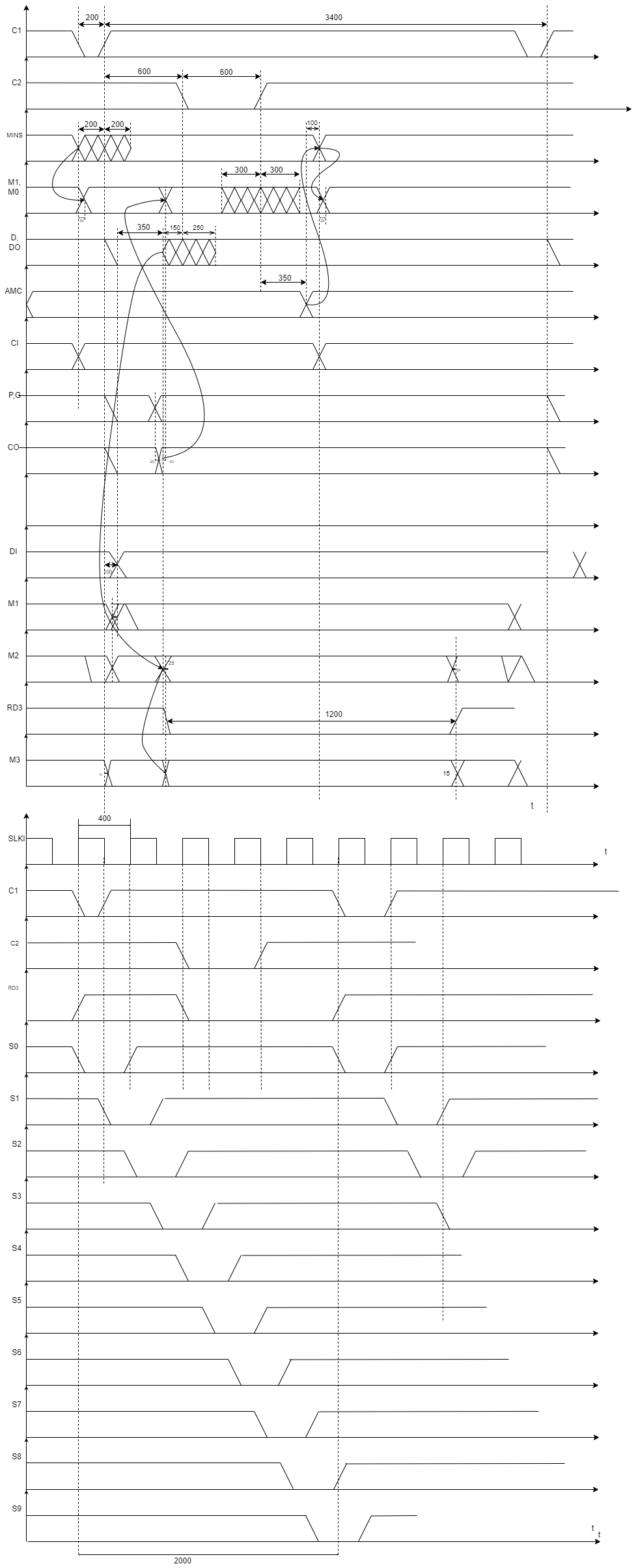

Временные диаграммы

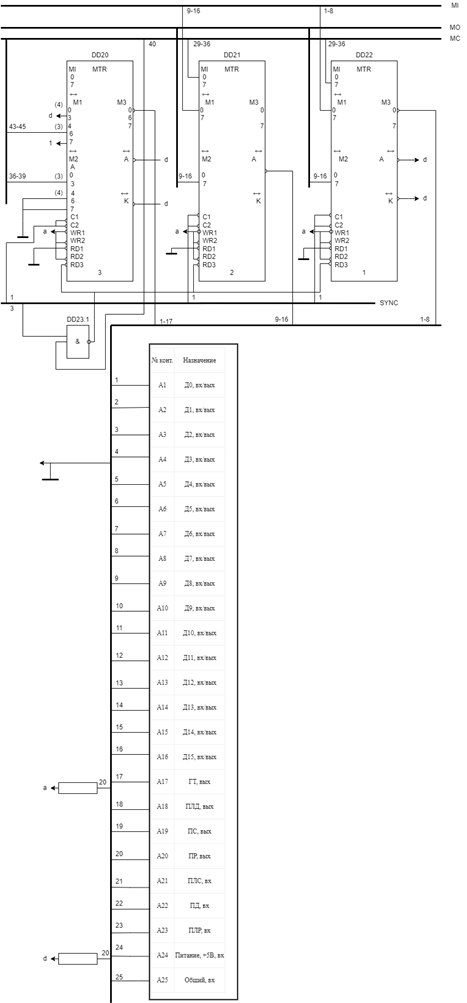

В таблице 5 представлены временные параметры БМУ, в таблице 6 временные параметры БМП и в таблице 7 временные параметры БМПП.

| Таблица 5 – Временные параметры БМУ | ||

| Параметр | Значение, нс | Описание |

| t1 | >=100 | Интервал действия низкого уровня синхроимпульса С1 |

| t2 | >=500 | Длительность микрокомандного цикла, период синхронизации |

| t3 | >=50 | Время дешифрации микроинструкции |

| t4 | >=310 | Интервал действия низкого уровня синхроимпульса С2 |

| t5 | >=40 | Интервал предустановки микроинструкции |

| t6 | >=50 | Интервал удержания микроинструкции |

| t9 | >=40 | Интервал предустановки кода данных |

| t10 | >=100 | Интервал удержания кода данных |

| t11 | >=200 | Время задержки выдачи адреса микрокоманды |

| Таблица 6 – Временные параметры БМП | ||

| Параметр | Значение, нс | Описание |

| T1 | >=100 | Интервал действия низкого уровня синхроимпульса СLK |

| T2 | >=500 | Длительность микрокомандного цикла, период синхронизации |

| T3 | >=50 | Интервал предустановки микроинструкции |

| T4 | >=310 | Интервал удержания микроинструкции |

| T5 | >=40 | Интервал удержания входных данных DI и входного переноса CI предыдущего цикла |

| | ||

| Продолжение таблицы 6 | ||

| T6 | >=50 | Время задержки формирования частичных переносов в процессорной секции |

| T7 | >=200 | Время задержки формирования выходных данных в процессорной секции |

| T8 | >=100 | Время задержки формирования сигналов на выходной шине сдвига |

| T9 | >=40 | Задержка выходного переноса в схеме ускоренного переноса SFC |

| T1 | >=100 | Интервал действия низкого уровня синхроимпульса СLK |

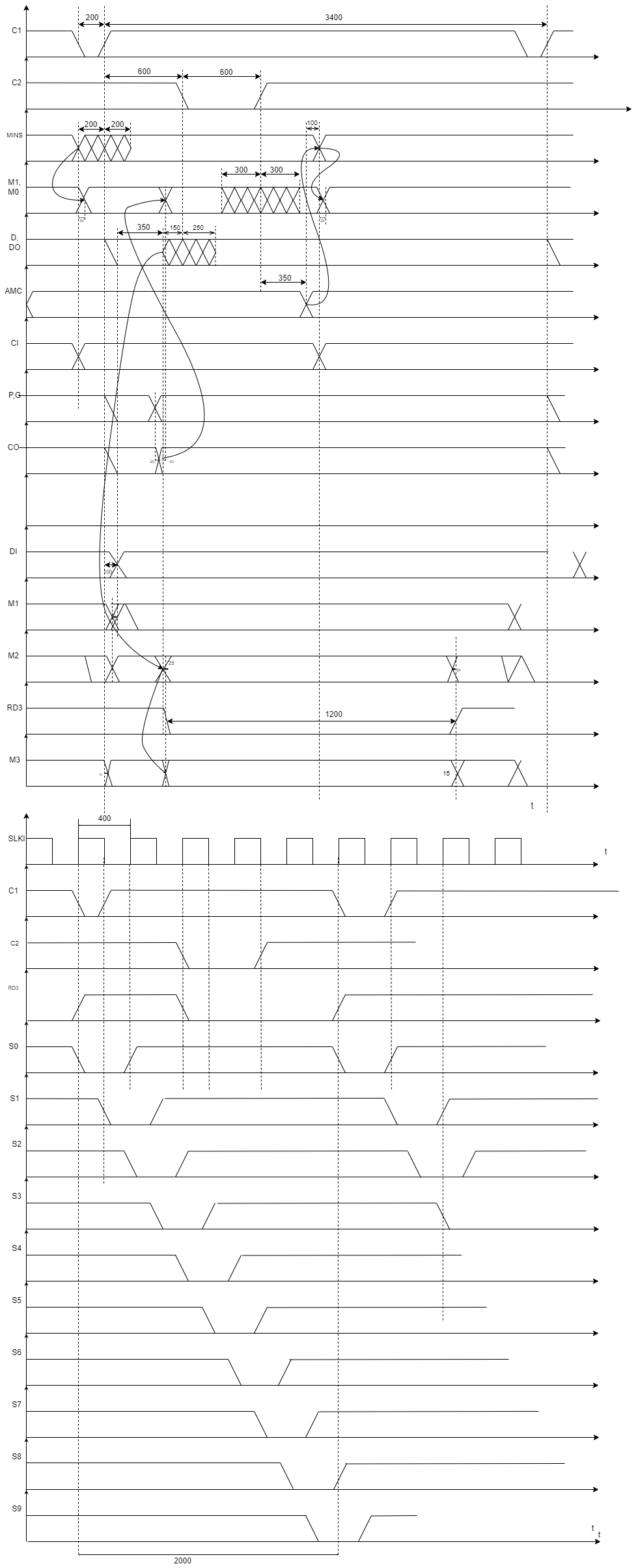

| Таблица 7 – Временные параметры БМПП | ||

| Параметр | Значение, нс | Описание |

| R1 | >=20 | Интервал действия низкого уровня синхроимпульса СLK |

| R2 | >=70 | Длительность микрокомандного цикла, период синхронизации |

| R3 | >=15 | Интервал предустановки микроинструкции |

| R4 | >=15 | Интервал удержания микроинструкции |

| R5 | 35 | Задержка дешифрации MINS |

| R6 | >=15 | Интервал предустановки данных |

| R7 | >=15 | Интервал действия низкого уровня синхроимпульса стробирования усилителей выходных магистралей |

| R8 | >=15 | Задержка установки выходных данных |

| R9 | >=25 | Задержка трансляции данных |

На рисунке 10 представлена временная диаграмма.

Рисунок 10 – Временная диаграмма

На рисунке 11 представлена диаграмма синхроимпульсов.

Рисунок 11 – Диаграмма синхроимпульсов

На рисунке 12 представлен блок синхронизации.

Рисунок 12 – Блок синхронизации

В таблице 8 представлена спецификация интегральных микросхем.

| Таблица 7 – Спецификация интегральных микросхем | |||

| Ячейка | Наименование | Описание | |

| DD1-DD4 | К584ВУ1А | Блок микропроцессоров | |

| DD20.3,4 | К155ЛИ1 КМ155ЛИ1 | Четыре логических элемента 2И | |

| DD27.1.1-4 | К155ЛН1 КМ155ЛН1 | Шесть логических элемента НЕ | |

| DD26.1.1,2 | К155ЛЛ1 КМ155ЛЛ1 |

| |

| DD26.1.3 | К155ЛЕ5 КМ155ЛЕ5 | Два логических элемента 3ИЛИ-НЕ | |

| DD11 DD12 | КР1533КП7 | Мультиплексор | |

| DD13 | К584ВМ1А | Микросхема БМУ | |

| DD20- DD26, DD14- DD19 | К541РУ1 | Микросхемы УП, ПЗУК | |

| DD27-DD29 | К584ВВ1 | Микросхемы БМПП | |

| DD5 | К155ИП4 | Схема ускоренного переноса | |

Заключение

В ходе данной работы была освоена программа «Х584», представляющая собой «Программно-логическую модель микропроцессора К584». Данной программой реализованы операции деления, сложения и вычитания.

Разработы и представлены алгоритмы реализуемых операций, как в общей схеме, так и каждая из операции отдельно.

Так же были рассчитаны технические параметры микроЭВМ. Представлена его структурная схема, функциональная, графики временных диаграмм работы и блок синхронизации.