Файл: Технический университет (мади) Заочный факультет Расчетнографическая работа.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 30.10.2023

Просмотров: 36

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«МОСКОВСКИЙ АВТОМОБИЛЬНО-ДОРОЖНЫЙ ГОСУДАРСТВЕННЫЙ

ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ (МАДИ)»

Заочный факультет

Расчетно-графическая работа

По дисциплине: Электротехника

Выполнил __________________/____02.04.2022___________/ Кузнецов

Н.С.

С

тудент (подпись) (дата) группы

тудент (подпись) (дата) группы 1ЗбАСУс1

Проверила /____________________/_____02.04.2022__________/ Матюхина

Е.Н.

(подпись) (дата)

Москва 2022г.

Лабораторная работа №1

Тема: запоминающие устройства

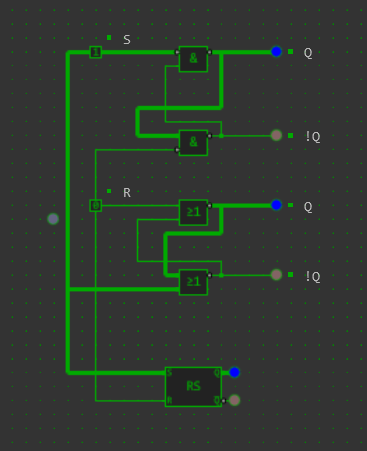

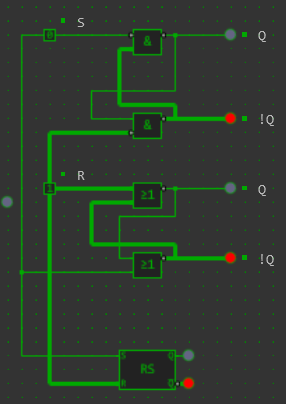

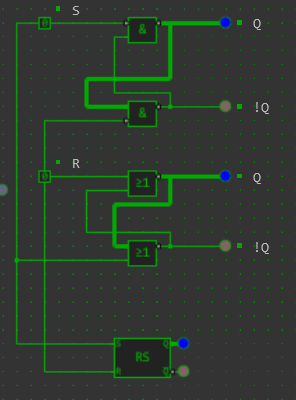

Задание 1: Запоминающий элемент – асинхронный RS триггер

Схема ИЛИ управляется единицей.

Схема И управляется нулём.

Рисунок 1 Режим установки в единицу

Рисунок 2 Режим установки в ноль.

Рисунок 3 Режим хранения.

Триггер в состоянии 0 когда на прямом выходе 0, а на инверсном единица.

Триггер в состоянии единица, когда на прямом выходе единица на инверсном ноль.

S вход (SET) вход установки единицы.

R вход (RESET) – установки нуля.

Задание 2

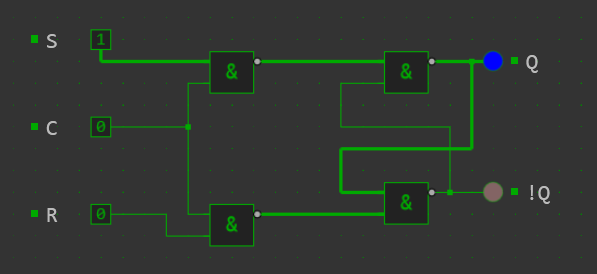

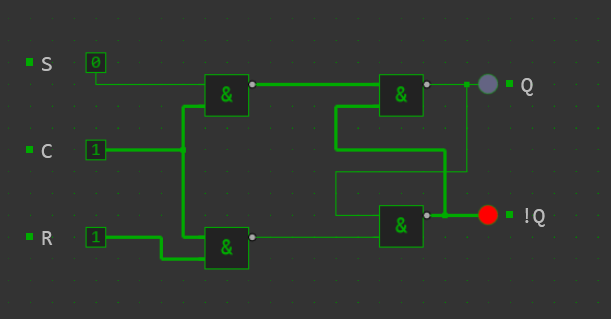

Синхронизируемый RS триггер

Рисунок 4 Режим хранения единицы

Рисунок 5 Режим установки нуля.

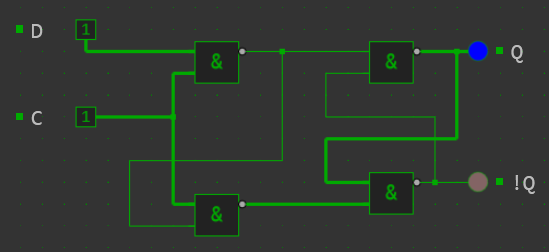

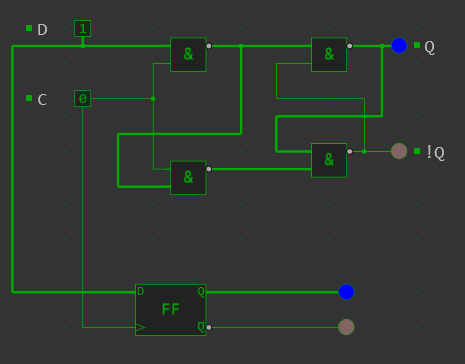

Построить D(delay) триггер

Триггер повторяет входной сигнал и хранит его.

С (импульсный) – управляющий сигнал, назначение сигнала C, разрешить приема информации на вход триггера.

Рисунок 6 D-триггер.

Рисунок 7 D-триггер в паралели.

Задание 3

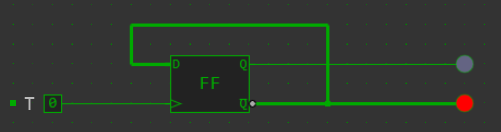

T триггер (триггер со счетным входом) – на каждый входной импульс состояние триггера меняется на противоположное

T триггер можно использовать как сумматор по модулю 2 вспомогательного типа.

Рисунок 8 T-триггер.

В процессе работы были построены и изучены различные типы интегральных триггеров.

Лабораторная работа №2

Функциональные узлы

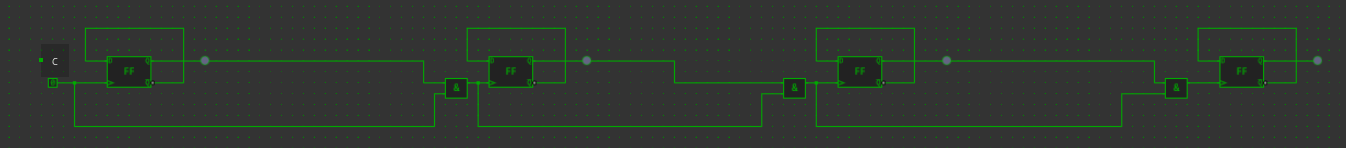

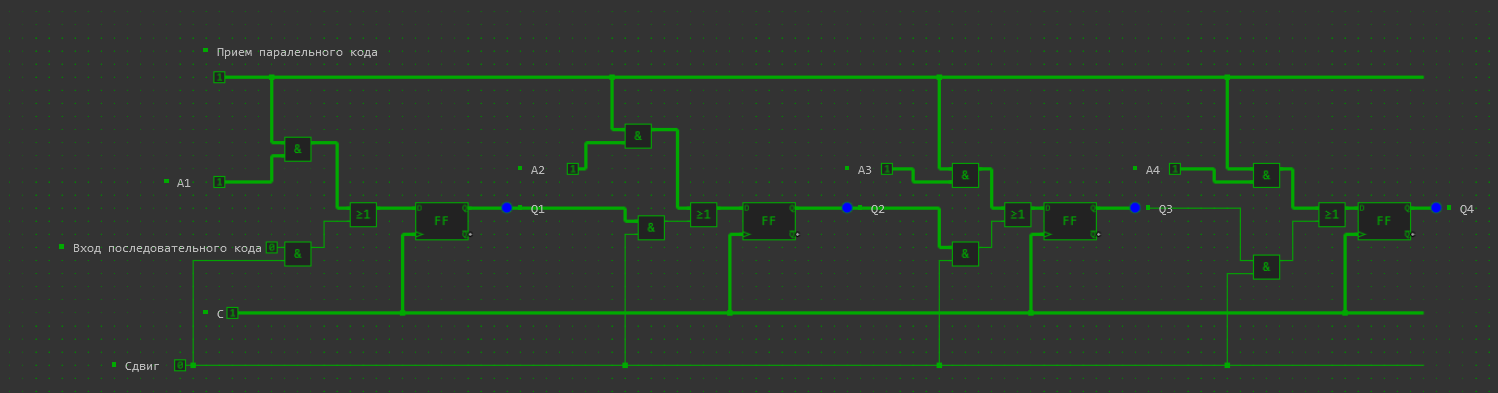

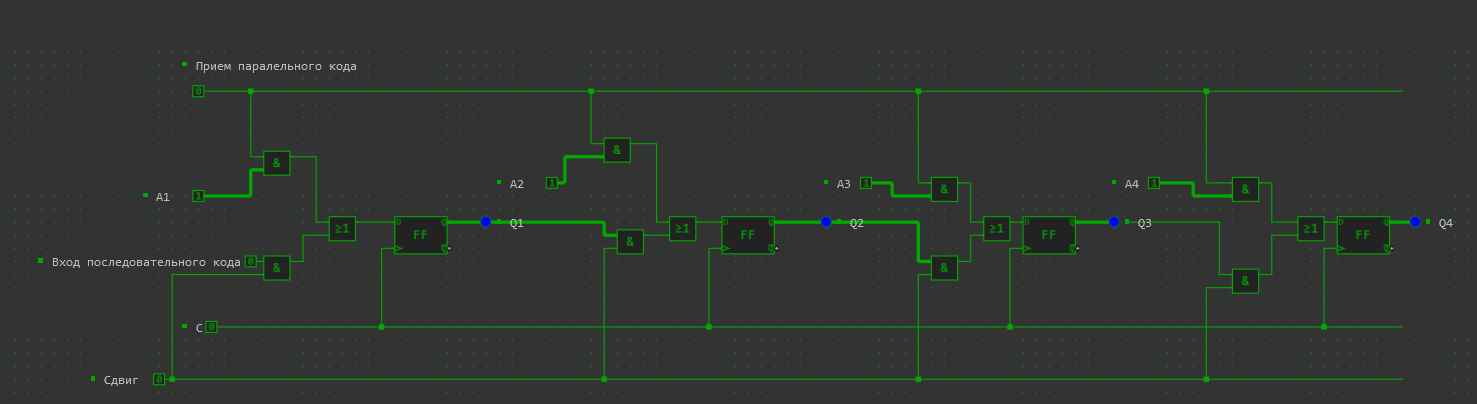

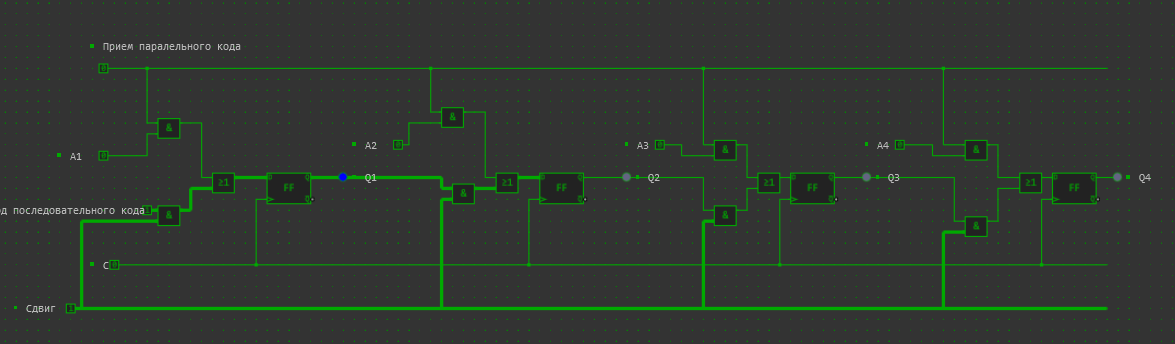

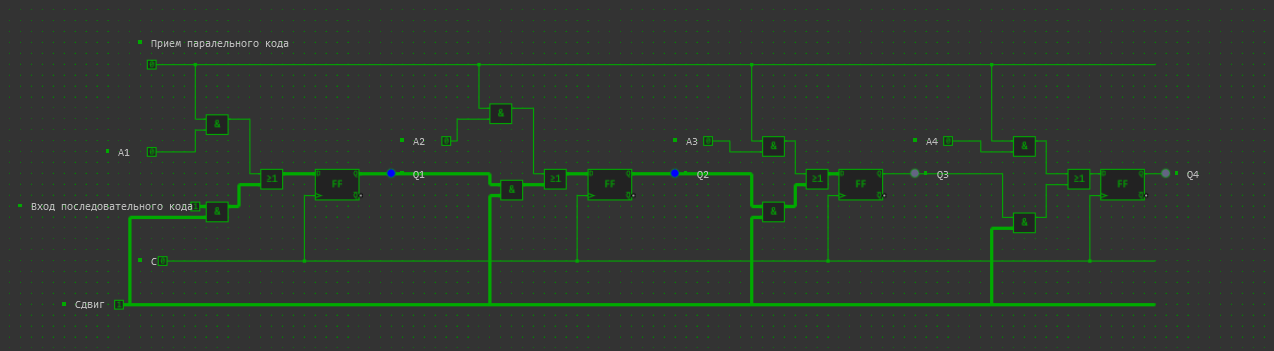

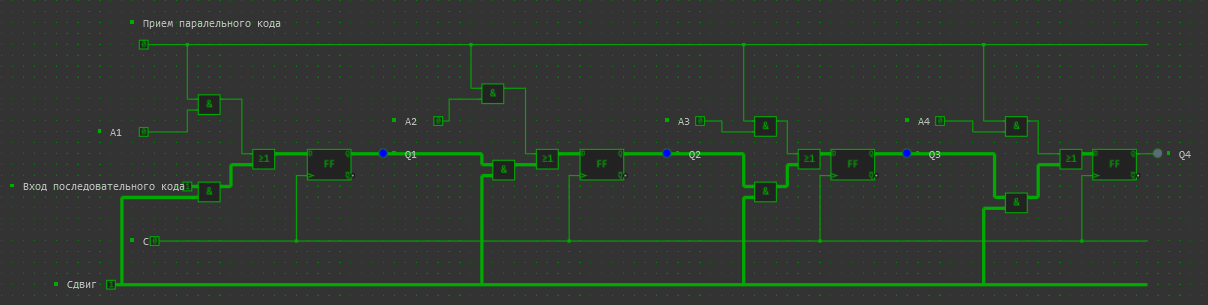

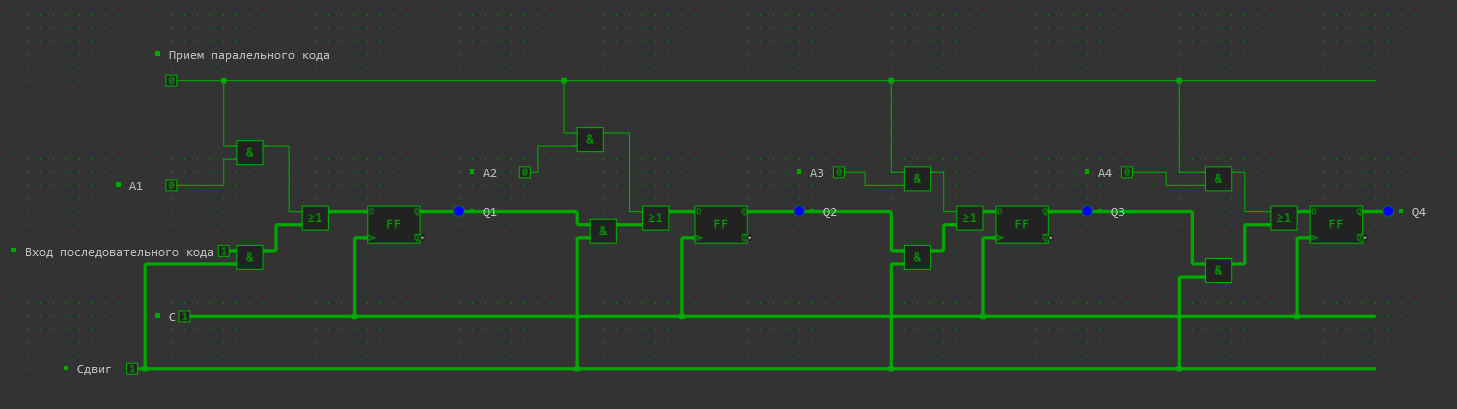

Задание 1.Разработать четырёхразрядный регистр сдвига с параллельным приемом информации.

Режим приема параллельного кода(режим 1), управляющий сигнал (прием).Информационный сигнал(А).

Режим сдвига управляющий сигнал сдвиг(СДВ), Информационный сигнал – последовательный код.

Рисунок 9 Режим приема параллельного кода (1,1,1,1)

Рисунок 9 Режим хранения кода (1,1,1,1)

Рисунок 10 Режим сдвига(часть 2).

Рисунок 11 Режим сдвига(часть 3).

Рисунок 12 Режим сдвига(часть 4).

Рисунок 13 Режим сдвига (часть 1).

Регистр является преобразователем последовательного кода в постоянный.

Вывод

Разработана логическая схема 4-ех разрядного регистра сдвига на D триггерах в системе схемотехнического проектирования

Выполнено моделирование которое подтвердило, что разработанная логическая схема регистра сдвига соответствует заданию.

Лабораторная работа №3

Двоичный суммирующий счетчик с последовательным переносом асинхрона.