Файл: Курсовой проект по дисциплине Прикладная теория цифровых автоматов.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 01.12.2023

Просмотров: 150

Скачиваний: 3

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

1 Условное графическое обозначение спецпроцессора

2.1 Структурная схема операционного автомата спецпроцессора

2.2 Функциональные схемы формирования признаков выполнения n-й операции

2.3 Элементы функциональной схемы операционного автомата

3.1 Список осведомительных сигналов Х

3.2 Список управляющих сигналов Y

3.3 Граф-схема алгоритма выполнения арифметических операций

3.4 Словесное описание граф-схемы алгоритма

3.5. Таблицы работы операционного автомата

2.3 Элементы функциональной схемы операционного автомата

В данном подразделе идёт описание функциональной реализации элементов, представленных на структурной схеме (рис. 2).

2.3.1 Регистры (без регистра RgS)

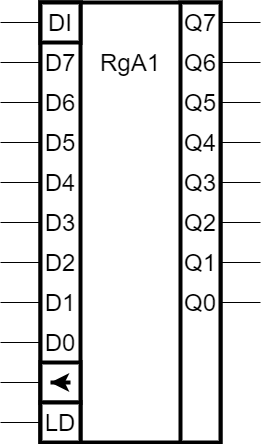

2.3.1.1 Регистр RgA1

Условное графическое обозначение регистра RgA1, обеспечивающего хранение числа A, а также арифметический сдвиг влево, представлено на рис. 5:

Рисунок 5 – УГО регистра RgA1

Данный регистр позволяет:

-

При подаче на вход LD логической единицы, число, установленное на входах D0 - D7 записывается в регистр. -

При подаче на вход ← логической единицы происходит сдвиг в сторону старших разрядов. При сдвиге влево в освободившийся разряд будет записываться значение с входа DI. -

На выходах Q0 - Q7 находится число, содержащееся в регистре.

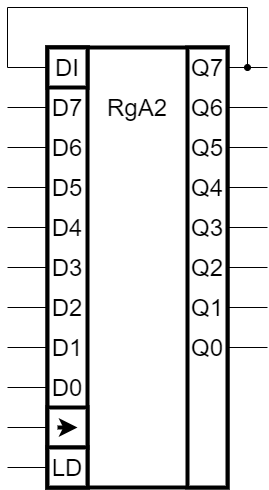

2.3.1.2 Регистр RgA2

Условное графическое обозначение регистра RgA2, обеспечивающего хранение числа A, а также арифметический сдвиг вправо, представлено на рис. 6:

Рисунок 6 – УГО регистра RgA2

Данный регистр позволяет:

-

При подаче на вход LD логической единицы, число, установленное на входах D0 - D7 записывается в регистр. -

При подаче на вход → логической единицы происходит сдвиг в сторону младших разрядов. При сдвиге вправо в освободившийся разряд будет записываться значение с входа DI. -

На выходах Q0 - Q7 находится число, содержащееся в регистре.

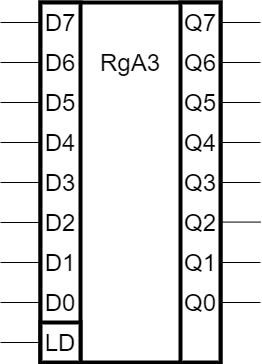

2.3.1.3 Регистр RgА3

Условное графическое обозначение регистра RgА3, обеспечивающего хранение числа с SM1 представлено на рис. 7:

Рисунок 7 – УГО регистра RgА3

Данный регистр позволяет:

-

При подаче на вход LD логической единицы, число, установленное на входах D0 - D7 записывается в регистр, LD – вход записи – по приходу сигнала y7 на данный вход регистр производит запись числа; -

На выходах Q0 - Q7 находится число, содержащееся в регистре.

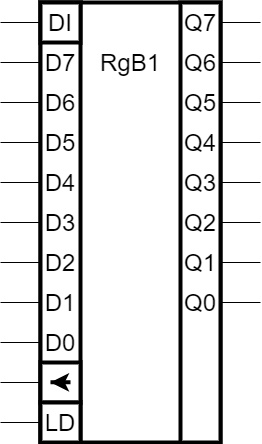

2.3.1.4 Регистр

RgВ1

Условное графическое обозначение регистра RgB1, обеспечивающего хранение числа В, а также арифметический сдвиг влево, представлено на рис. 8:

Рисунок 8 – УГО регистра RgB1

Данный регистр позволяет:

-

При подаче на вход LD логической единицы, число, установленное на входах D0 - D7 записывается в регистр; -

При подаче на вход ← логической единицы происходит сдвиг в сторону старших разрядов. При сдвиге влево в освободившийся разряд будет записываться значение с входа DI; -

На выходах Q0 - Q7 находится число, содержащееся в регистре.

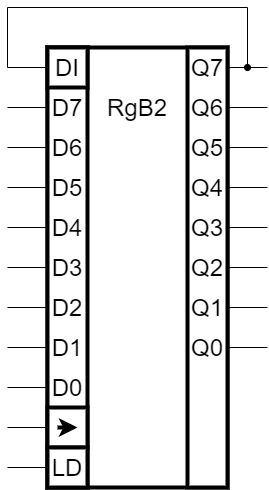

2.3.1.5 Регистр RgB2

Условное графическое обозначение регистра RgB2, обеспечивающего хранение числа В, а также арифметический сдвиг вправо, представлено на рис. 9.

Рисунок 9 – УГО регистра RgB2

Данный регистр позволяет:

-

При подаче на вход LD логической единицы, число, установленное на входах D0 - D7 записывается в регистр; -

При подаче на вход → логической единицы происходит сдвиг в сторону младших разрядов. При сдвиге вправо в освободившийся разряд будет записываться значение с входа DI; -

На выходах Q0 - Q7 находится число, содержащееся в регистре.

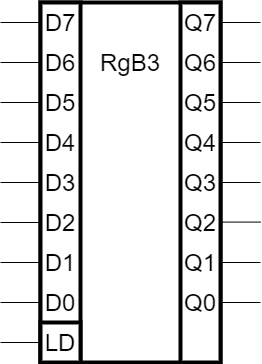

2.3.1.6 Регистр RgB3

Условное графическое обозначение регистра RgB3, обеспечивающего хранение числа В представлено на рис. 10.

Рисунок 10 – УГО регистра RgB3

Данный регистр позволяет:

-

При подаче на вход LD логической единицы, число, установленное на входах D0 - D7 записывается в регистр; -

На выходах Q0 - Q7 находится число, содержащееся в регистре.

2.3.2 Сумматоры

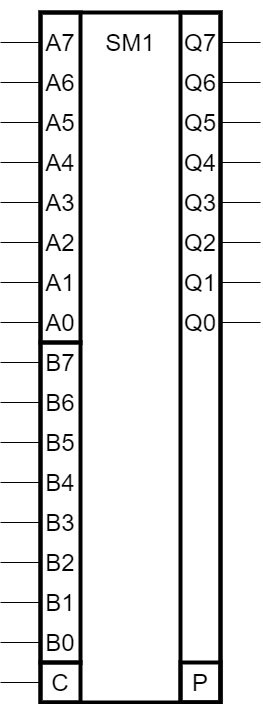

2.3.2.1 Сумматор SM1

Условное графическое обозначение сумматора SM1 представлено на рис. 11:

Рисунок 11 – УГО сумматора SM1

Входы: A7 - A0 – входы сумматора, на которые поступает число от регистра RgA1; B7 - B0 – входы сумматора, на которые поступает число от регистра RgА2; C – вход переноса;

Выходы: Q7-Q0 – являются выходами сумматора

, с которых выходят разряды полученного в результате суммы числа; P – выход переноса.

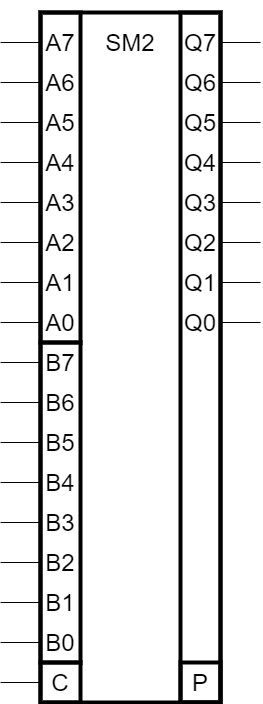

2.3.2.2 Сумматор SM2

Условное графическое обозначение сумматора SM2 представлено на рис. 12:

Рисунок 12 – УГО сумматора SM2

Входы: A7 - A0 – входы сумматора, на которые поступает число от регистра RgB1; B7 - B0 – входы сумматора, на которые поступает инвертированное число от регистра RgB2; C – вход переноса, на который подается сигнал у8;

Выходы: Q7-Q0 – являются выходами сумматора, с которых выходят разряды полученного в результате суммы числа; P – выход переноса.

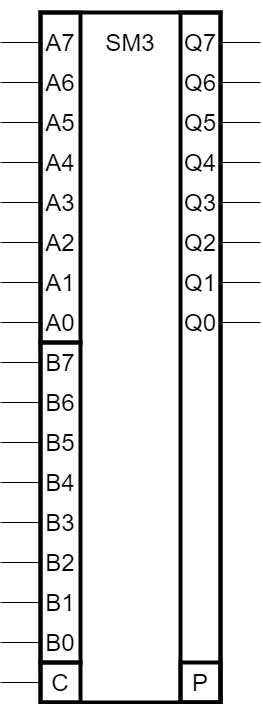

2.3.2.3 Сумматор SM3

Условное графическое обозначение сумматора SM3 представлено на рис. 13:

Рисунок 13 – УГО сумматора SM3

Входы: A7 - A0 – входы сумматора, на которые поступает число c регистра RgB2; B7 - B0 – входы сумматора, на которые поступает число c регистра RgB3; C – вход переноса;

Выходы: Q7-Q0 – являются выходами сумматора, с которых выходят разряды полученного в результате суммы числа; P – выход переноса.

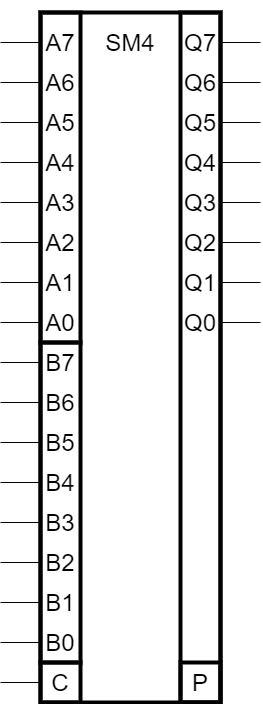

2.3.2.4 Сумматор SM4

Условное графическое обозначение сумматора SM3 представлено на рис. 14:

Рисунок 14 – УГО сумматора SM4

Входы: A7 - A0 – входы сумматора, на которые поступает число c регистра RgB1; B7 - B0 – входы сумматора, на которые поступает число c регистра RgB3; C – вход переноса;

Выходы: Q7-Q0 – являются выходами сумматора, с которых выходят разряды полученного в результате суммы числа; P – выход переноса

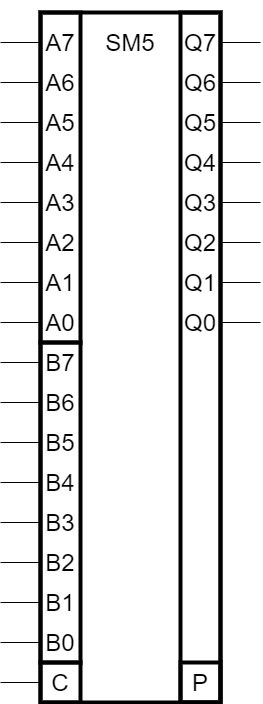

2.3.2.5 Сумматор SM5

Условное графическое обозначение сумматора SM3 представлено на рис. 15:

Рисунок 15 – УГО сумматора SM5

Входы: A7 - A0 – входы сумматора, на которые поступает число c регистра RgА3; B7 - B0 – входы сумматора, на которые поступает число c мультиплексора MUXB; C – вход переноса;

Выходы: Q7-Q0 – являются выходами сумматора, с которых выходят разряды полученного в результате суммы числа; P – выход переноса

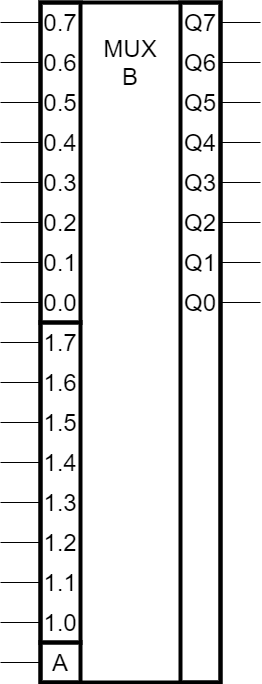

2.3.3 Мультиплексор MUXB

Условное графическое обозначение мультиплексора MUXВ представлено на рис. 16:

Рисунок 16 – УГО мультиплексора MUXВ

Входы: 0.0 - 0.7 – входы мультиплексора, на которые поступают инвертированные разряды числа с SM2; 1.0 - 1.7 – входы мультиплексора, на которые поступают инвертированные разряды с SM2; A – вход для коммутации, на который приходит сигнал y8;

Выходы: Q0 - Q7 – выходы мультиплексора;

Кодировка мультиплексора представлена в табл. 2:

Таблица 2 – Кодировка мультиплексора MUXB

| A | Выход группы |

| 0 | 0.0-0.7 |

| 1 | 1.0-1.7 |

2.3.4 Регистр RgS

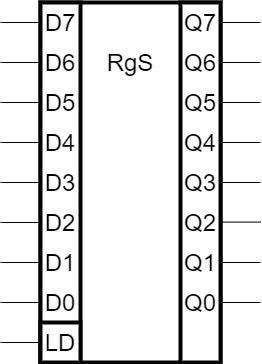

Условное графическое обозначение регистра RgS представлено на рис. 17:

Рисунок 17 – УГО регистра RgS

Входы: D7 - D0 – входы регистра, на которые поступает число с сумматора SM5; LD – вход записи – по приходу сигнала y11 на данный вход регистр производит запись числа;

Выходы: Q7 - Q0 – выходы регистра, с которых выходит результат;

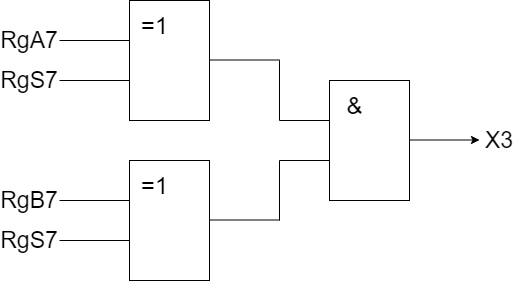

2.3.5 Схема определения переполнения (блок OF, overflow)

Условное графическое обозначение блока OF представлено на рис. 18:

Рисунок 18 – УГО переполнения

В таблице 3 приведена таблица истинности данной схемы.

Таблица 3 – Таблица истинности логической функции переполнения

| RgA7 | RgB7 | RgS7 | OF |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |