Файл: Курсовой проект по дисциплине Прикладная теория цифровых автоматов.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 01.12.2023

Просмотров: 143

Скачиваний: 3

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

1 Условное графическое обозначение спецпроцессора

2.1 Структурная схема операционного автомата спецпроцессора

2.2 Функциональные схемы формирования признаков выполнения n-й операции

2.3 Элементы функциональной схемы операционного автомата

3.1 Список осведомительных сигналов Х

3.2 Список управляющих сигналов Y

3.3 Граф-схема алгоритма выполнения арифметических операций

3.4 Словесное описание граф-схемы алгоритма

3.5. Таблицы работы операционного автомата

3 Разработка закодированной граф-схемы машинного алгоритма выполнения заданных арифметических операций

Перед тем, как составить закодированную граф-схему, необходимо обозначить списки осведомительных и управляющих сигналов (п. 3.1 и 3.2 далее). Граф-схема представлена далее в п. 3.3.

3.1 Список осведомительных сигналов Х

-

X1 – сигнал о выполнении условия A < 0, B ≥ 0, A ≥ 0, B ≥ 0, |A| < 0,25, |B| < 0,25; -

X2 – сигнал о выполнении условия A ≥ 0, B < 0, |A| < 0,5, |B| ≤ 0,5; -

X3 – сигнал проверки переполнения разрядной сетки; -

RA – сигнал о наличии на входе числа A; -

RB – сигнал о наличии на входе числа B.

3.2 Список управляющих сигналов Y

-

y1 – запись числа А в регистры RgA1, RgA2; -

y2 – сдвиг числа A в сторону старших разрядов; -

y3 – сдвиг числа A в сторону младших разрядов; -

y4 – запись числа B в регистры RgB1, RgB2, RgB3; -

y5 – сдвиг числа В в сторону старших разрядов; -

y6 – сдвиг числа B в сторону младших разрядов; -

y7 – запись результата с SM1; -

y8 – управляющий сигнал для SM2 (+1 в младший разряд если у8=1); -

y9 – сигнал для выбора адреса в мультиплексоре MUXB; -

y10 – управляющий сигнал для SM5 (+1 в младший разряд если у10=1); -

у11- запись результата операций в регистр RgS; -

OF – сигнал о переполнении; -

ER – сигнал о несоответствии ни одному из условий; -

RD – сигнал выдачи результата.

3.3 Граф-схема алгоритма выполнения арифметических операций

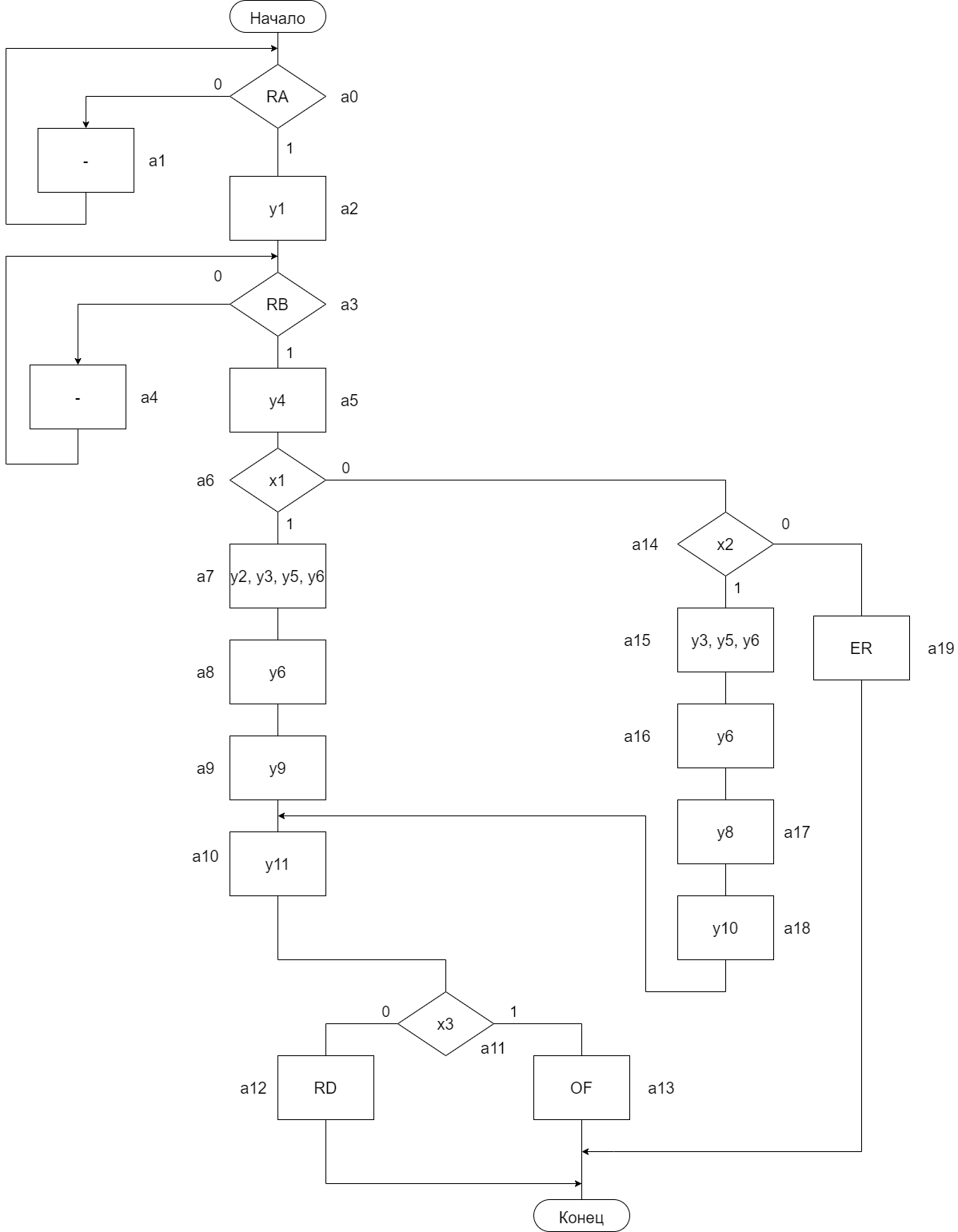

На рис. 19 обозначена граф-схема алгоритма выполнения заданных арифметических операций.

Рисунок 19 – Граф-схема алгоритма

3.4 Словесное описание граф-схемы алгоритма

Вершина 0. Проверка входного сигнала RA. Если на входе присутствует А (RA=1), то осуществляется переход в вершину 2. В противном случае процесс повторяется.

Вершина 1. Дополнительная пустая операторная вершина.

Вершина 2. По управляющему сигналу Y1 осуществляется запись числа А со входов спецпроцессора на регистры RgA1, RgA2. Осуществляется переход в вершину 3.

Вершина 3. Проверка входного сигнала RВ. Если на входе присутствует В (RВ=1), то осуществляется переход в вершину 5. В противном случае процесс повторяется.

Вершина 4. Дополнительная пустая операторная вершина.

Вершина 5. По управляющему сигналу Y4 осуществляется запись числа А со входов спецпроцессора на регистры RgВ1, RgВ2, RgB3. Осуществляется переход в вершину 6.

Вершина 6. Проверка осведомительного сигнала Х1 (группа условий для 2,5А+1,25В). Если Х1=1, то осуществляется переход в вершину 7. Если Х1=0, осуществляется переход в вершину 14.

Вершина 7. По управляющему сигналу Y2 осуществляется сдвиг влево в регистре RgА1. По управляющему сигналу Y3 осуществляется сдвиг вправо в регистре RgA2. По управляющему сигналу Y5 осуществляется сдвиг влево в регистре RgB1. По управляющему сигналу Y6 осуществляется сдвиг вправо в регистре RgB2. Осуществляется переход в вершину 8.

Вершина 8. По управляющему сигналу Y6 осуществляется сдвиг вправо в регистре RgB2. По управляющему сигналу Y7 осуществляется запись числа с SM1 в регистр RgА3. Осуществляется переход в вершину 9.

Вершина 9. По управляющему сигналу Y9 осуществляется коммутация входов 1.0-1.7 на входы Q0-Q7 на мультиплексоре MUXB. Осуществляется переход в вершину 10.

Вершина 10. По управляющему сигналу Y11 осуществляется запись числа в регистр RgS. Осуществляется переход в вершину 11.

Вершина 11. Проверка осведомительного сигнала Х3 (переполнение разрядной сетки). Если Х3=1, то осуществляется переход в вершину 13. Если Х2=0, осуществляется переход в вершину 12.

Вершина 12. Происходит выдача сигнала о готовности результата (RD). Осуществляется переход в конечную вершину.

Вершина 13. Производится выдача сигнала о переполнении разрядной сетки (OF). Осуществляется переход в конечную вершину.

Вершина 14. Проверка осведомительного сигнала Х2 (группа условий для 1,5А-3,5В). Если Х2=1, то осуществляется переход в вершину 7. Если Х2=0, осуществляется переход в вершину 19.

Вершина 15. По управляющему сигналу Y3 осуществляется сдвиг вправо в регистре RgА2. По управляющему сигналу Y5 осуществляется сдвиг влево в регистре RgВ1. По управляющему сигналу Y6 осуществляется сдвиг вправо в регистре RgB2. Осуществляется переход в вершину 16.

Вершина 16. По управляющему сигналу Y6 осуществляется сдвиг вправо в регистре RgB2. Осуществляется переход в вершину 17.

Вершина 17. По управляющему сигналу Y8 осуществляется добавление единицы в младший разряд в SM2. По управляющему сигналу Y7 осуществляется запись числа с SM1 в регистр RgА3. Без управляющих сигналов осуществляется коммутация входов 0.0-0.7 на входы Q0-Q7 на мультиплексоре MUXB. Осуществляется переход в вершину 18.

Вершина 18. По управляющему сигналу Y10 осуществляется добавление единицы в младший разряд в SM5. Осуществляется переход в вершину 10.

Вершина 19. Производится выдача сигнала о несоответствии чисел ни одному из условий (ER). Осуществляется переход в конечную вершину.

3.5. Таблицы работы операционного автомата

Проверочные значения: A = 22, B = 28. Представление в двоичной системе задана в таблице 4.

Таблица 4 – Значения в прямом, обратном и дополнительном коде

| Значение | Прямой код | Обратный код | Дополнительный код |

| 22 | 0.0010110 | 0.0010110 | 0.0010110 |

| 28 | 0.0011100 | 0.0011100 | 0.0011100 |

В таблице ниже (табл. 5) отражено содержимое всех регистров операционного автомата в каждом такте работы спецпроцессора для заданной пары операндов A и B:

Таблица 5 – Потактовая работа операционного автомата

| Такт | RgA1 | RgA2 | RgB1 | RgB2 | RgB3 | RgS |

| 1 | * | * | * | * | * | * |

| 2 | 0.0010110 | 0.0010110 | * | * | * | * |

| 3 | 0.0010110 | 0.0010110 | * | * | * | * |

| 4 | 0.0010110 | 0.0010110 | 0.0011100 | 0.0011100 | 0.0011100 | * |

| 5 | 0.0010110 | 0.0010110 | 0.0011100 | 0.0011100 | 0.0011100 | * |

| 6 | 0.0101100 | 0.0001011 | 0.0111000 | 0.0001110 | 0.0011100 | * |

| 7 | 0.0101100 | 0.0001011 | 0.0111000 | 0.0000111 | 0.0011100 | * |

| 8 | 0.0101100 | 0.0001011 | 0.0111000 | 0.0000111 | 0.0011100 | * |

| 9 | 0.0101100 | 0.0001011 | 0.0111000 | 0.0000111 | 0.0011100 | 1.0010010 |

| 10 | 0.0101100 | 0.0001011 | 0.0111000 | 0.0000111 | 0.0011100 | 1.0010010 |

| 11 | 0.0101100 | 0.0001011 | 0.0111000 | 0.0000111 | 0.0011100 | 1.0010010 |

-

В 1 такте происходит опрос RА; -

Во 2 такте происходит запись числа А в регистры RgA1, RgA2; -

В 3 такте происходит опрос RB; -

В 4 такте происходит запись числа B в регистры RgB1, RgB2, RgB3; -

В 5 такте происходит опрос Х1; -

В 6 такте происходит сдвиг в регистре RgA1 и RgB1 в сторону старших разрядов, RgА2 и RgB2 в сторону младших разрядов; -

В 7 такте происходит сдвиг в регистре RgB2 в сторону младших разрядов и запись результата с SM1 в регистр RgA3; -

В 8 такте происходит выбора адреса в мультиплексоре MUXB; -

В 9 такте происходит запись результата операций в регистр RgS; -

В 10 такте происходит опрос X3; -

В 11 такте происходит выдача сигнала о переполнении разрядной сетки.

Учитывая условия задачи, программа должна выполнить операцию 2,5A + 3,25B. Если А = 22, а В = 28, 2,5A + 3,25B= 55 + 91 = 146. Переведём 146 в немодифицированный дополнительный двоичный код 146 = 1.0010010. В нашем случае на выход спецпроцессора поступил сигнал о переполнении разрядной сетки (OF).