Файл: Методичні вказівки до виконання лабораторних робіт з дисциплін "схемотехніка еом" "компютерна схемотехніка".doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 03.12.2023

Просмотров: 225

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

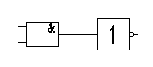

Э лемент ИЛИ-НЕ

Элемент ИЛИ-НЕ реализует функцию логического сложения с последующей инверсией результата. Он представляется моделью из последовательно включенных элементов ИЛИ и НЕ.

Его таблица истинности получается из таблицы истинности элемента ИЛИ путем инверсии результата.

Эквивалентная модель элемента:

Таблица истинности

| Вход А | Вход В | Выход У |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Выражения Булевой алгебры:

Y = (A + B)'

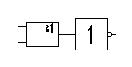

Исключающее ИЛИ-НЕ

Данный элемент реализует функцию "исключающее ИЛИ" с последующей инверсией результата. Он представляется моделью из двух последовательно соединенных элементов: исключающее ИЛИ и НЕ.

Эквивалентная модель элемента:

Таблица истинности

| Вход А | Вход В | Выход У |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Выражения Булевой алгебры:

Буфер служит для подачи больших токов в нагрузку. Данный буфер является неинвертирующим.

Таблица истинности

-

Вход

Выход

1

1

0

0

Установку типа буфера можно произвести с помощью команды Model в меню Circuit (CTRL+M). При использовании ТТЛ элемента в качестве буфера необходимо выбрать модель буфера LS-BUF или LS-OC-BUF (OpenCollector – открытый коллектор). Если в качестве буфера применяется КМОП элемент, следует выбрать модель Н- BUF, либо HC-OD-BUF (OpenDrain -открытый сток). Если тип буфера не выбран, то буфер ведет себя как обычный цифровой элемент с малой нагрузочной способностью.

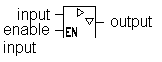

Буфер с тремя состояниями

Буфер с тремя состояниямиБуфер с тремя состояниями имеет дополнительный разрешающий вход (enable input). Если на разрешающем входе высокий потенциал, то элемент функционирует по таблице истинности обыкновенного буфера, если низкий, то независимо от сигнала на входе выход перейдет в состояние с высоким импедансом. В этом состоянии буфер не пропускает сигналы, поступающие на вход.

Установка режима работы, производится так же, как и для обычного буфера.

Узлы комбинационного типа

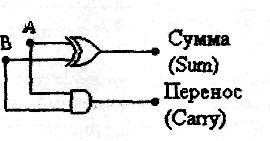

Полусумматор

ПолусумматорПолусумматор производит сложение двух одноразрядных двоичных чисел. Он имеет два входа слагаемых: А, В и два выхода: суммы (Sum) и переноса (Carry). Суммирование производится элементом Исключающее ИЛИ, а перенос – элементом И.

Эквивалентная схема:

Таблица функционирования

| Входы | Выходы | Примечание | ||

| A | B | Сумма | Перенос | |

| 0 | 0 | 0 | 0 | 0 + 0 = 0 |

| 0 | 1 | 1 | 0 | 0 + 1 = 1 |

| 1 | 0 | 1 | 0 | 1 + 0 = 1 |

| 1 | 1 | 1 | 1 | 1 + 1 = 0 (Carry = 1) |

Выражения Булевой алгебры:

Сумма = А В

Перенос = А • В.

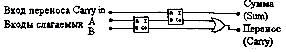

П

олный двоичный сумматор

олный двоичный сумматорПолный двоичный сумматор производит сложение трех одноразрядных двоичных чисел. Результатом является двухразрядное двоичное число, младший разряд которого назван суммой, старший разряд – переносом.

Устройство имеет три входа и два выхода. Входы: слагаемых – А, В и переноса - CarryIN. Выходы: суммы – Sum и переноса – СаггуOUT.. Полный двоичный сумматор можно реализовать на двух полусумматорах и одном элементе ИЛИ.

| Входы | Выходы | |||

| A | B | Перенос | Сумма | Перенос |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Д

ешифратор из 3 в 8

ешифратор из 3 в 8Дешифратор — логическое устройство, имеющее n входов и 2n выходов. Каждой комбинации входного кода соответствует активный уровень на одном из 2n выходов. Данный дешифратор имеет три входа адреса (А, В, С), два разрешающих входа (Gl, G2) и 8 выходов (YO...Y7). Номер выхода, имеющего активное состояние, равен числу N, определяемому состоянием адресных входов: N = 2

2С + 21В + 20А.

Активным уровнем является уровень логического нуля. Дешифратор работает, если на входе G1 высокий потенциал, а на G2 – низкий. В других случаях все выходы пассивны, то есть имеют уровень логической 1.

Таблица функционирования

| Входы разрешения | Адресные входы | Выходы | ||||||||||

| G1 | G2 | A | B | C | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

| X | 1 | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

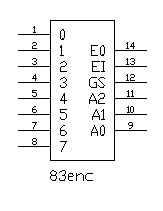

П

риоритетный шифратор

риоритетный шифраторШифратор выполняет операцию, обратную дешифратору. Строго говоря, только один из входов шифратора должен иметь активный уровень.

Данный шифратор при наличии на нескольких входах активного состояния активным считает вход со старшим номером. Кроме того, выход дешифратора инверсный, то есть значения разрядов двоичного числа на выходе инвертированы. Если хотя бы один из входов шифратора в активном состоянии, выход GS также будет в активном состоянии, а выход ЕО – в пассивном и наоборот. При пассивном состоянии разрешающего входа Е1 выходы GS также будут пассивными. Активным уровнем, так же, как и у дешифратора, является уровень логического нуля.

Таблица функционирования

| E1 | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | A2 | A1 | A0 | GS | E0 |

| 1 | x | x | x | x | x | x | x | x | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0 | x | x | x | x | x | x | x | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | x | x | x | x | x | x | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | x | x | x | x | x | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | x | x | x | x | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | x | x | x | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | x | x | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | x | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |