Добавлен: 05.12.2023

Просмотров: 17

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра РС

отчет

по лабораторной работе №5

по дисциплине «Цифровая электроника»

Тема: «Основы построения схем в пакете Quartus II»

Вариант-10

| Студент гр. 1402 | | Косарев А.М. |

| Преподаватель | | Богданов Д.В. |

Санкт-Петербург

2023

Цель работы:

Собрать схему синхронного двоичного четырехразрядного счетчика, запрограммировать его в отладочную плату, модифицировать его в двоично-десятичный, реализовать его с синхронным сбросом и разрешением работы на языке Verilog. Также собрать схему синхронного двоичного 32-разрядного счетчика.

Задание:

1. Собрать схему синхронного двоичного четырехразрядного счетчика. Для этого воспользоваться кодом из приложения.

Изучить схему, реализованную в RTL-Viewer.

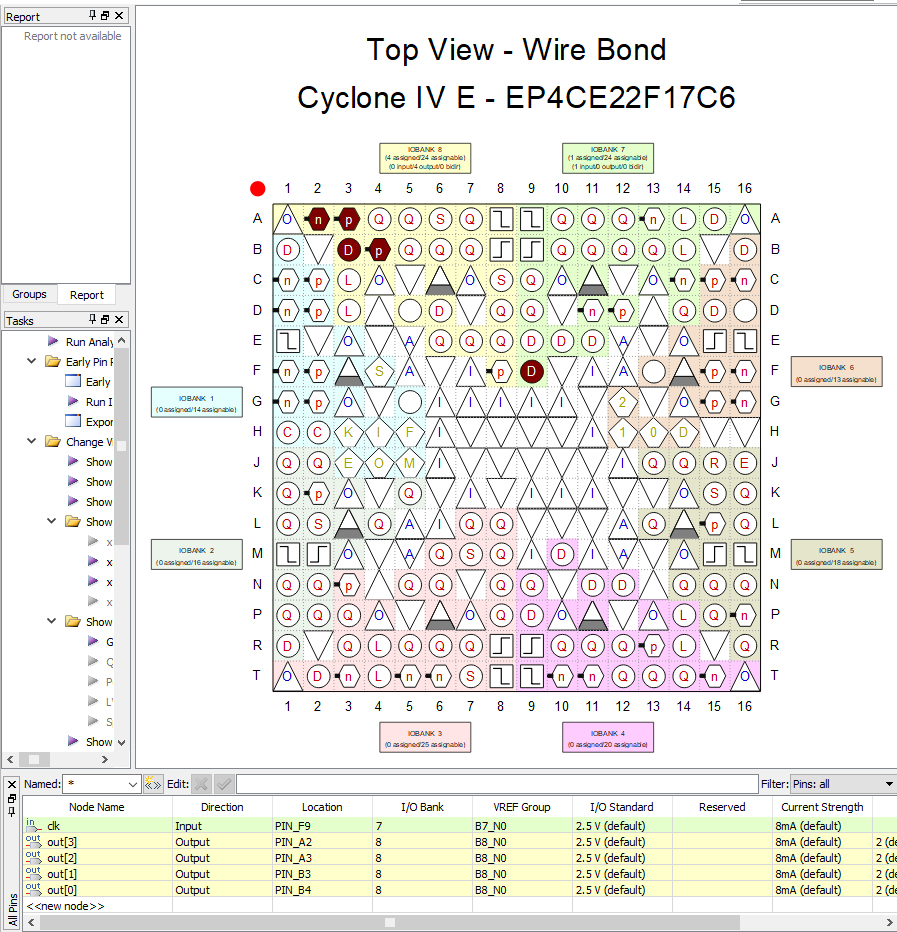

Построить временные диаграммы, иллюстрирующие работу устройства. Период тактового сигнала задать 20 нс.

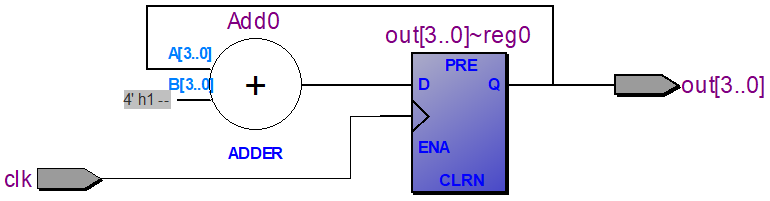

Запрограммировать в отладочную плату. Тип ПЛИС – Altera Cyclone IV E EP4CE22F17C6. Указать входной сигнал на key1 (clock),

выходные – на LED5…LED2.

Обратите внимание, что по каждому нажатию клавиши состояния могут увеличиться не на единицу, а на большую величину, это связано с «дребезгом» контактов кнопки.

2. Модифицировать схему так, чтобы получился двоично-десятичный счетчик. Для этого воспользоваться кодом из приложения.

Изучить схему, реализованную в RTL-Viewer.

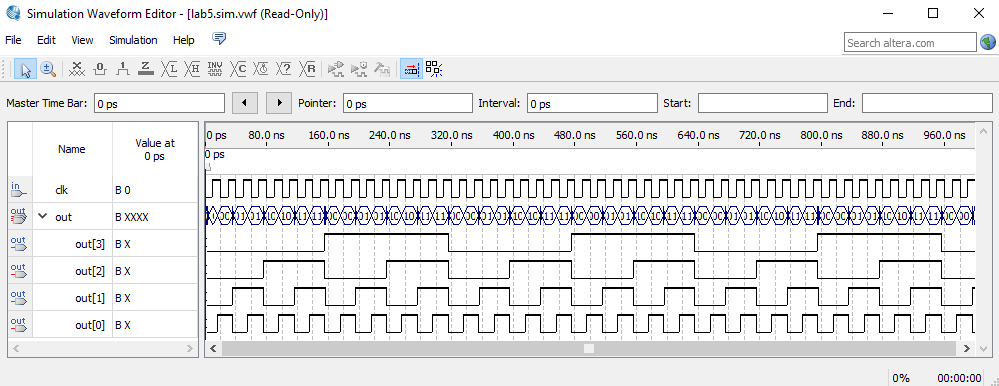

Построить временные диаграммы, иллюстрирующие работу устройства. Период тактового сигнала задать 20 нс.

3. Собрать схему синхронного двоичного четырехразрядного счетчика с синхронным сбросом и разрешением работы. Для этого воспользоваться кодом из приложения.

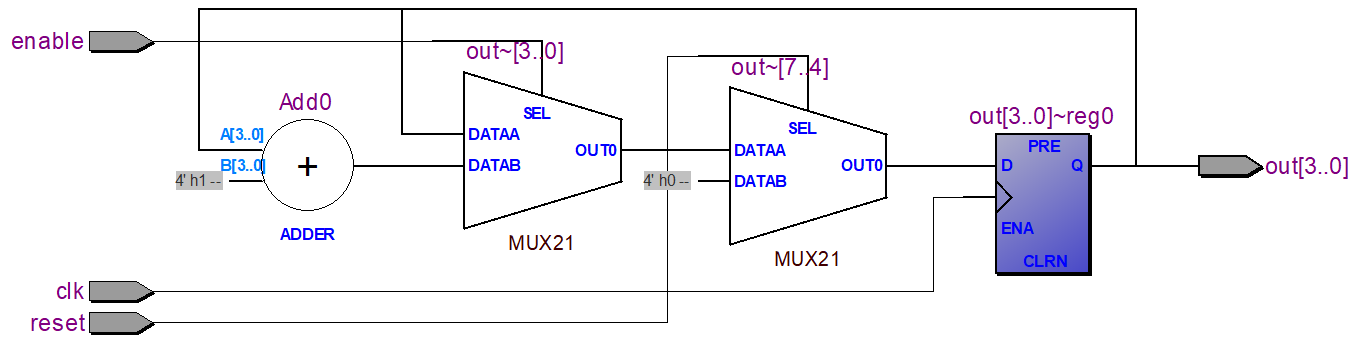

Изучить схему, реализованную в RTL-Viewer.

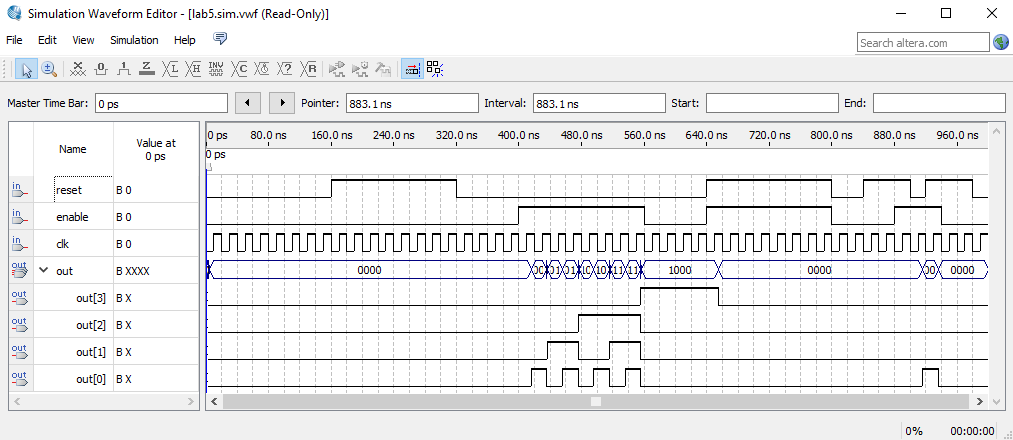

Построить временные диаграммы, иллюстрирующие все режимы работы устройства. Период тактового сигнала задать 20 нс.

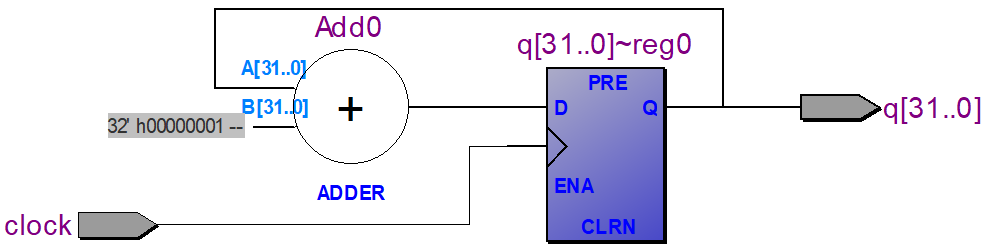

4. Собрать схему синхронного двоичного 32-разрядного счетчика.

Запрограммировать в отладочную плату. Указать входные сигналы:

clock – R8 (частота 50МГц от кварцевого резонатора);

сигналы q [28:25] подать на LED5-LED2.

C какой частотой мигает светодиод LED2? Поясните почему.

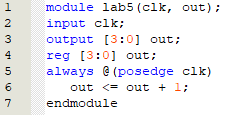

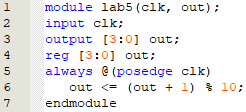

1. Текст программы:

RTL-Viewer:

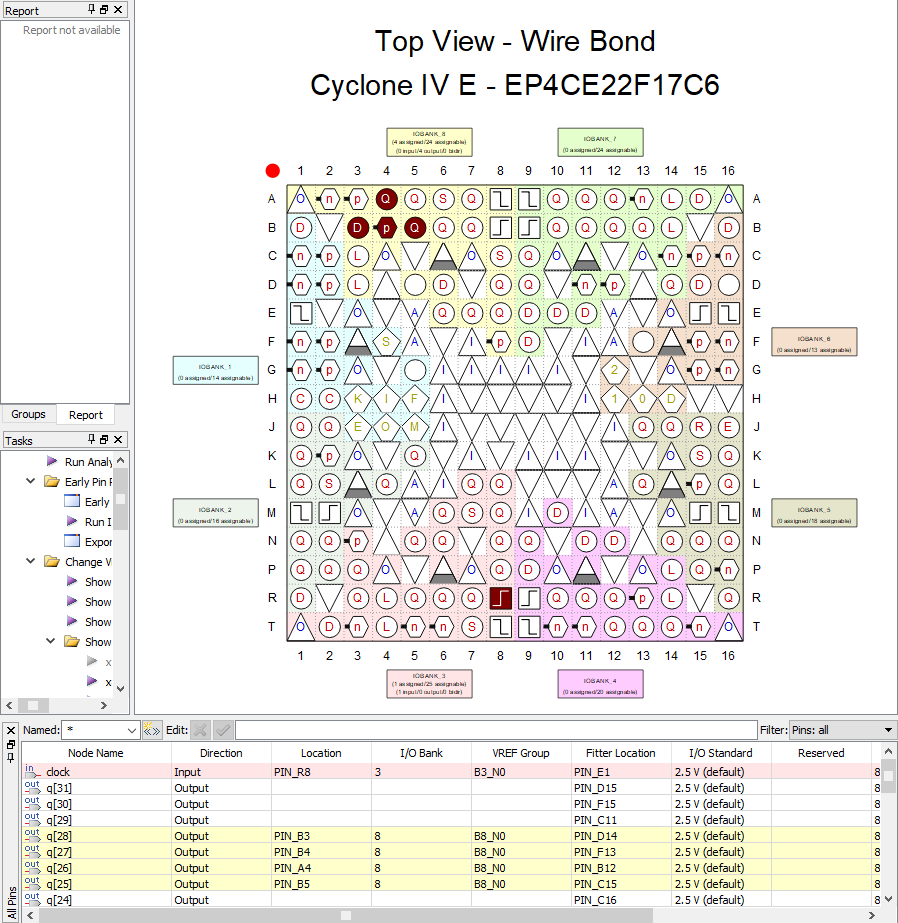

PinPlanner:

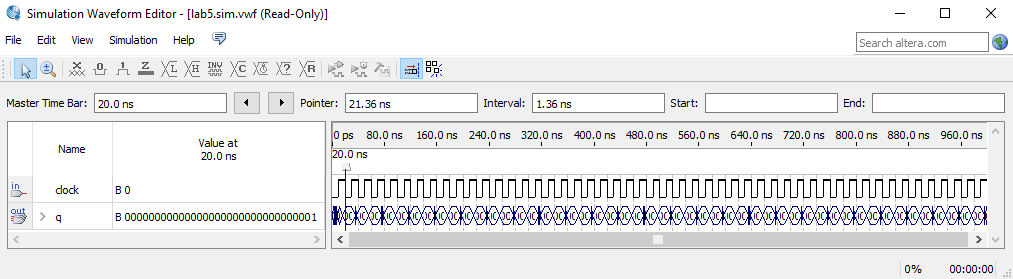

Временная диаграмма с наличием задержек:

2. Текст программы:

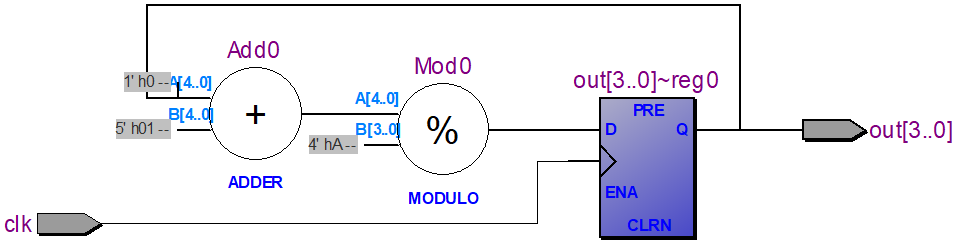

RTL-Viewer:

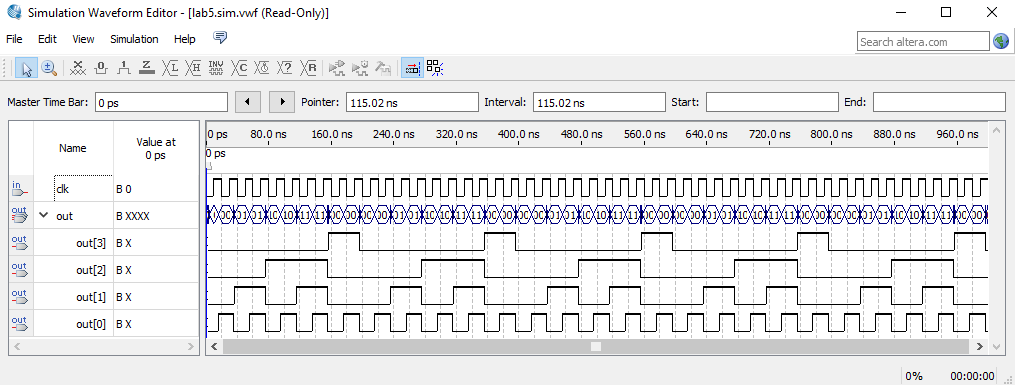

Временная диаграмма с наличием задержек:

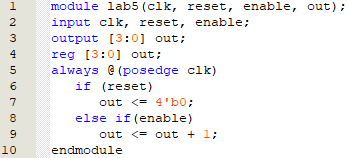

3. Текст программы:

RTL-Viewer:

Временная диаграмма с наличием задержек:

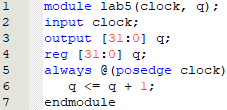

4. Текст программы:

RTL-Viewer:

PinPlanner:

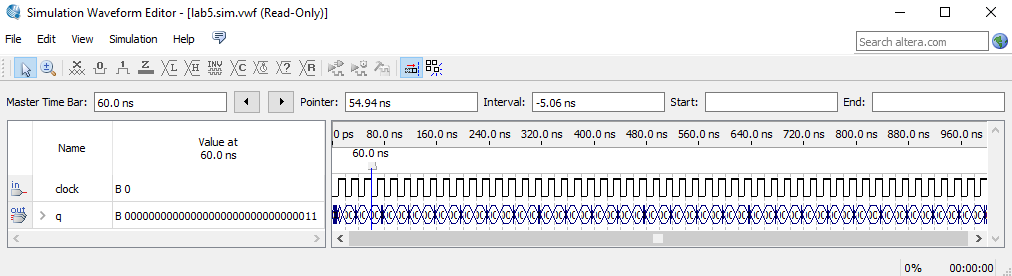

Временная диаграмма с наличием задержек:

C какой частотой мигает светодиод LED2? Поясните почему.

Светодиод LED2 мигает с частотой 25 МГц (25 МГц = 1 / 40 нс), потому что единица в младшем разряде получается каждую вторую итерацию счёта.

Вывод:

В данной работе мы изучили схемы различных счётчиков, использовали язык Verilog для различных типов счетчиков

, проанализировали каждую схему в RTL Viewer и изучили осциллограммы. Использовав PinPlaner, запрограммировали ПЛИС и получили наглядную демонстрацию принципа работы счетчиков.