Добавлен: 13.02.2019

Просмотров: 1557

Скачиваний: 19

считывание (или запись) информации не по одному, а сразу по нескольким адресам: i, i+1, i+2 и т.д. Количество одновременно опрашиваемых адресов, по которым происходит считывание информации, определяет кратность чередования адресов, что соответствует количеству блоков ОП. На практике обычно используется 2-х или 4-х кратное чередование адресов, т.е. ОП делится на 2 или 4 блока.Запись информации в блоки осуществляется независимо друг от друга. Информация по адресу i хранится в первом блоке, по адресу i+1 - во втором блоке и т.д. Считываемая с блоков информация далее переписывается в кэш-память для последующей переработки.

-

Метод страничной организации (Page-mode) . При данном методе организации память адресуется не по байтам, а по границам страниц. Размер страницы обычно равен 1 или 2 Кбайта. Данный метод предполагает наличие в системе кэш-памяти емкостью не менее 128 Кб куда предварительно считываются требуемые страницы ОП для последующей переработки МП или другим устройством. Обновленная информация периодически из кэш-памяти сбрасывается в ОП.

Последние два метода системной организации памяти предполагают обязательное наличие в системе сверх быстродействующей кэш-памяти для опережающего (read-ahaed) чтения в нее информации из ОП с последующей обработкой ее микропроцессором, что снижает время простоя последнего и повышает общую производительность системы.

Память типа DRAM

Динамическая оперативная память (Dynamic RAM – DRAM)

используется в большинстве систем оперативной памяти перс ональных компьютеров. Основное преимущество этого типа памяти состоит в том, что ее ячейки упакованы очень плотно, т.е. в небольшую микросхему можно упаковать много битов, а значит, на их основе можно построить память большей емкости.

Ячейки памяти в микросхеме DRAM – это крошечные конденсаторы, которые удерживают заряды. Проблемы, связанные с памятью этого типа, вызваны тем, что она динамическая, т.е. должна постоянно регенерироваться, так как в противном случае электрические заряды в конденсаторах памяти будут “стекать”, и данные будут потеряны. Регенерация происходит, когда контроллер памяти системы берет крошечный перерыв и обращается ко всем строкам данных в микросхемах памяти. Большинство систем имеет контроллер памяти (обычно встраиваемый в набор микросхем системной платы), который настроен на соответствующую промышленным стандартам частоту регенерации, равную 15 мкс.

Регенерация памяти, к сожалению, “отнимает время” у процессора: каждый цикл регенерации по длительности занимает несколько циклов центрального процессора. В старых компьютерах циклы регенерации могли занимать до 10% процессорного времени, но в современных системах, расходы на регенерацию составляют 1% (или меньше) процессорного времени. Некоторые системы позволяют изменить параметры регенерации с помощью программы установки параметров CMOS, но увеличение времени между циклами регенерации может привести к тому, что в некоторых ячейках памяти заряд “стечет”, а это вызовет сбой памяти. В большинстве случаев надежнее придерживаться рекомендуемой или заданной по умолчанию частоты регенерации.

-

устройствах DRAM для хранения одного бита используется только один транзистор и пара конденсаторов, поэтому они более вместительны, чем микросхемы других типов памяти. Транзистор для каждого однозарядного регистра DRAM использует для чтения состояния смежного конденсатора. Если конденсатор заряжен, в ячейке записана 1; если заряда нет – записан 0. Заряды в крошечных конденсаторах все время стекают, вот почему память должна постоянно регенерироваться. Даже мгновенное прерывание подачи питания или какой-нибудь сбой в

циклах регенерации приведет к потере заряда в ячейке DRAM, а следовательно, к потере данных.

Чтобы сократить время ожидания, стандартная память DRAM разбивается на страницы. Обычно для доступа к данным в памяти требуется выбрать строку и столбец адреса, что занимает некоторое время.

Разбиение на страницы обеспечивает более быстрый дос туп ко всем данным в пределах данной строки памяти, то есть изменяет не номер строки, а номер столбца. Такой режим доступа к данным памяти называется (быстрым) постраничным режимом ( Fast Page Mode), а сама память – памятью Fast Page Mode. Другие вариации постраничного режима называются Static Column или Nibble Mode.

Страничная организация памяти – простая схема повышения эффективности памяти, в соответствии с которой память разбивается на страницы длиной от 512 байт до нескольких килобайтов. Электронная схема пролистывания позволяет при обращении к ячейкам памяти в пределах страницы уменьшить количество состояний ожидания. Если нужная ячейка памяти находится вне текущей страницы, то добавляется одно или больше состояний ожидания, так как система выбирает новую страницу.

SDRAM (Synchronous DRAM) – это тип динамической оперативной памяти DRAM , работа которой синхронизируется с шиной памяти. SDRAM передает информацию в высокоскоростных пакетах, Использующих высокоскоростной синхронизированный интерфейс. SDRAM позволяет избежать использования большинства циклов ожидания, необходимых при работе асинхронной DRAM, поскольку сигналы, по которым работает память такого типа, синхронизированны с тактовым генератором системной платы.

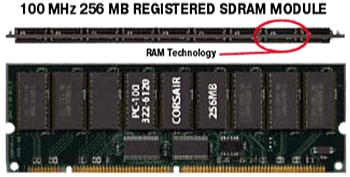

Модуль SDRAM на 256Мбайт

Следующим преимуществом SDRAM перед EDO заключается в том, что EDO не работает на частотах свыше 66 МГц, а SDRAM доступна частота шины памяти до 100 МГц.

Стандартный модуль памяти SDRAM PC100

Выпустив чипсет 440BX с официальной поддержкой тактовой частоты системной шины до 100 МГц, Intel сделала оговорку, что модули памяти SDRAM неустойчиво работают на такой скорости. После заявления Intel представила новую спецификацию, описывающую все тонкости, - SDRAM PC100.

Спецификация PC100. Ключевые моменты

-

Определение минимальной и максимальной длины пути для каждого сигнала в модуле.

-

Определение ширины дорожек и расстояния между ними.

-

6-слойные платы с отдельными сплошными слоями масса и питание.

-

Строгое определение длины тактового импульса, его маршрутизации,

момента начала и окончания.

-

Подавляющие резисторы в цепях передачи данных.

-

Детальная спецификация компонента SDRAM. Модули должны содержать чипы памяти SDRAM, совместимые с Intel SDRAM Component

SPEC (version 1.5).

Данной спецификации отвечают только 8-нс чипы, а 10-нс чипы, по мнению Intel, неспособны устойчиво работать на частоте 100 МГц.

-

Детальная спецификация программирования EEPROM. Модуль должен включать интерфейс SPD, совместимый с Intel SPD Component SPEC (version 1.2).

-

Особые требования к маркировке.

-

Подавление электромагнитной интерференции.

-

Местами позолоченные печатные платы.

Введение стандарта PC100 в некоторой степени можно считать

рекламной уловкой, но все известные производители памяти и системных плат поддержали эту спецификацию, а с появлением следующего поколения памяти переходят на его производство.

Спецификация PC100 является очень критичной, одно описание с дополнениями занимает больше 70 страниц.

Для комфортной работы с приложениями, требующими высокого быстродействия, разработано следующее поколение синхронной динамической памяти - SDRAM PC133. В продаже можно найти модули, поддерживающие эту спецификацию, причем цена на них превышает цены соответствующих моделей PC100 на 10-30%. Насколько это оправдано, судить довольно сложно. Продвижением данного стандарта на рынок занимается уже не Intel, а их главный конкурент на рынке процессоров AMD. Intel же решила поддерживать память от Rambus, мотивируя это тем, что она лучше сочетается с шиной AGP 4x.

133-МГц чипы направлены на использование с новым семейством микропроцессоров, работающих на частоте системной шины 133 МГц, и полностью совместимы со всеми PC100-продуктами. Такими производителями, как VIA Technologies, Inc., Acer Laboratories Inc. (ALi), OPTi Inc., Silicon Integrated Systems (SiS) и Standard Microsystems

Corporation (SMC), разработаны чипсеты, поддерживающие спецификацию PC133.

Недавно появилась еще одна интересная технология - Virtual Channel Memory. VCM использует архитектуру виртуального канала, позволяющую более гибко и эффективно передавать данные с использованием каналов регистра на чипе. Данная архитектура интегрирована в SDRAM. VCM, помимо высокой скорости передачи данных, совместима с существующими SDRAM, что позволяет делать апгрейд системы без значительных затрат и модификаций. Это решение также нашло поддержку у некоторых производителей чипсетов.

Enhanced SDRAM (ESDRAM)

Для преодоления некоторых проблем с задержкой сигнала, присущих стандартным DRAM-модулям, производители решили встроить небольшое количество SRAM в чип, т. е. создать на чипе кэш. Одним из таких решений, заслуживающих внимания, является ESDRAM от Ramtron International Corporation.

ESDRAM - это по существу SDRAM плюс немного SRAM. При малой задержке и пакетной работе достигается частота до 200 МГц. Как и

-

случае внешней кэш-памяти, DRAM-кэш предназначен для хранения наиболее часто используемых данных. Следовательно, уменьшается время доступа к данным медленной DRAM.

DDR SDRAM (SDRAM II)

DDR SDRAM (Double Date Rate SDRAM) является синхронной памятью, реализующей удвоенную скорость передачи данных по сравнению с обычной SDRAM.