Файл: Отчет по лабораторной работе 4 по теме Активные элементы радиоэлектронных устройств.docx

Добавлен: 18.01.2024

Просмотров: 91

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

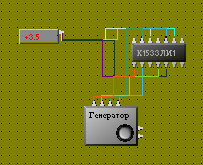

В программе не предусмотрена возможность подключения логического анализатора непосредственно к генератору входных сигналов.

6.5. Задать частоту генерирования.

1).Навести курсор на корпус генератора и нажать правую кнопку мыши.

2). В открывшемся меню выбрать позицию «Частота».

3). В открывшемся подменю выбрать соответствующее значение.

6.6. Задать режим непрерывной генерации, для чего:

1).Навести курсор на корпус генератора и нажать правую кнопку мыши.

2). В открывшемся меню выбрать позицию «Такты».

3). В открывшемся подменю выбрать позицию «Непрерывно».

6.7. Запустить генератор, нажав кнопку на его корпусе.

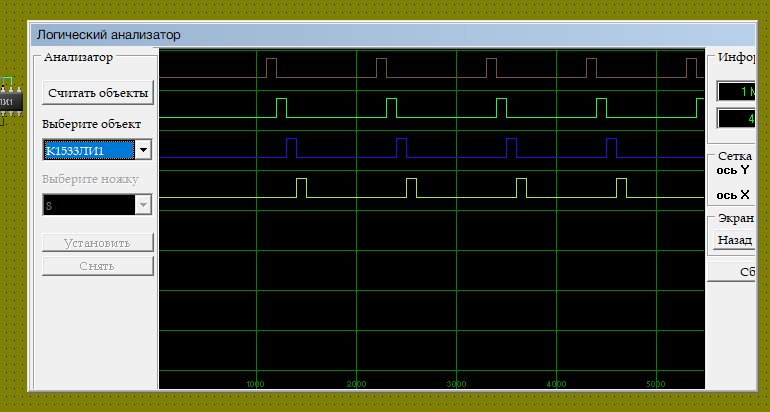

6.8. По сигналам на экране логического анализатора убедиться в работоспособности генератора и логического элемента. Обратить внимание на то, что с четырёх выходов генератора снимается четырёхфазный сигнал и временная задержка между фазами равна длительности генерируемых импульсов.

6.9. Занести в отчёт полученные временные диаграммы с пояснением их формы.

6.10. Задать конечное число генерируемых импульсов (например, 7) и получить аналогичные временные диаграммы.

Схема соединения логического анализатора к выходам 1533ЛИ и полученные временные диаграммы

ВЫВОД: Вентили 2И стабильно работают при динамически изменяющемся воздействии, и исправно умножают сигнал на логическую единицу.

6. Изучение работы триггеров

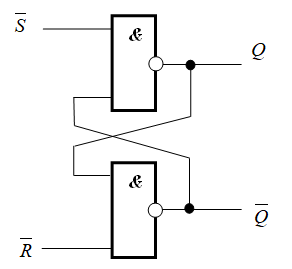

6.1. Синтез RS-триггера на базе логических вентилей И – НЕ

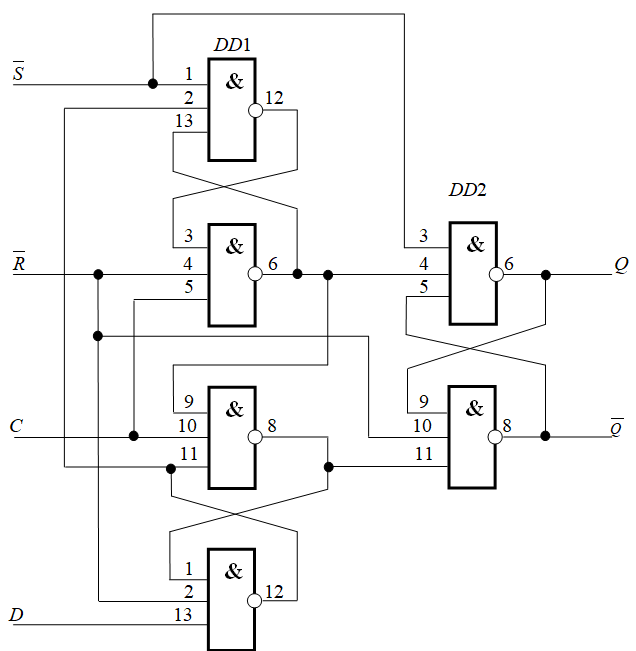

6.1. Используя логические вентили И-НЕ, построить схему, представленную на рис. 1.5.

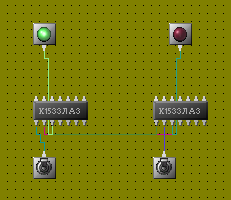

Рис. 1.5. Схема RS-триггера. Скриншот схемы.

Заполнить таблицу 1.4.

|  | Q |  |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | - | - |

6.2. Построение D-триггера на базе логических элементов

6.2.1. Используя логические вентили, собрать схему синхронного D-триггера, представленную на рис. 1.6. Составить таблицу истинности D-триггера, представленного на рис. 1.6.

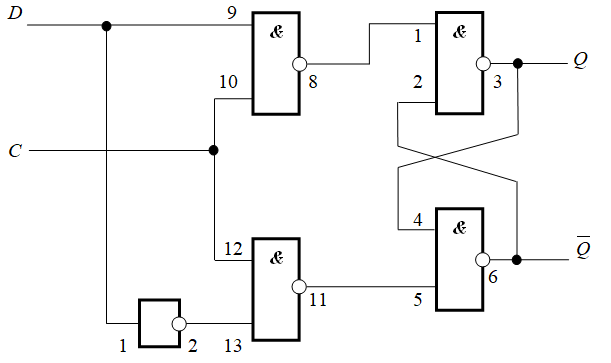

Рис. 1.6. Схема синхронного D-триггера. Скриншот схемы.

Заполнить таблицу 1.5.

| D | C | Q |  |

| 0 0 1 1 | 0 1 0 1 | 1 0 1 1 | 0 1 0 0 |

Проверить правильность составленной таблицы истинности. При проверке использовать все последовательные комбинации входных сигналов.

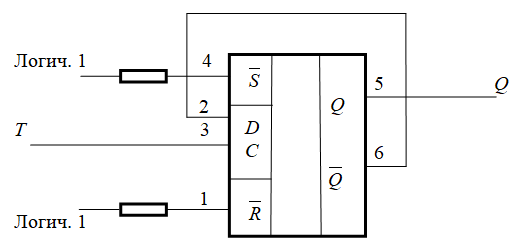

6.3. Построение D-триггера на базе логических элементов с учётом сигналов принудительной установки и сброса

6.3.1. Ввести дополнительные сигналы принудительной установки (S) и принудительного сброса (R) D-триггера. С учётом введённых сигналов построить схему (рис. 1.7):

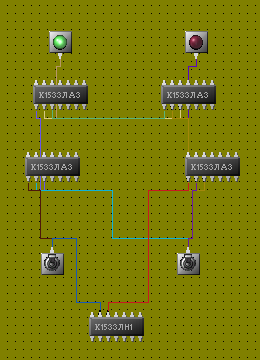

Скриншот схемы.

Скриншот схемы. Рис. 1.7. Схема D-триггера с сигналами принудительной установки и сброса.

6.3.2. На основании собранной схемы составить таблицу истинности (табл. 1.6.) и убедиться в работоспособности устройства. Пояснить полученные результаты.

Таблица 1.6.

| |  |  | D | C | Q |  |

| 0. | 0 | 0 | 0 | 0 | 0 | 1 |

| 1. | 0 | 0 | 0 | 1 | 0 | 1 |

| 2. | 0 | 0 | 1 | 0 | 1 | 0 |

| 3. | 0 | 0 | 1 | 1 | 1 | 0 |

| 4. | 0 | 1 | 0 | 0 | 0 | 1 |

| 5. | 0 | 1 | 0 | 1 | 0 | 1 |

| 6. | 0 | 1 | 1 | 0 | 0 | 1 |

| 7. | 0 | 1 | 1 | 1 | 0 | 1 |

| 8. | 1 | 0 | 0 | 0 | 1 | 0 |

| 9. | 1 | 0 | 0 | 1 | 1 | 0 |

| 10. | 1 | 0 | 1 | 0 | 1 | 0 |

| 11 | 1 | 0 | 1 | 1 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 | 1 |

| 13 | 1 | 1 | 0 | 1 | 1 | 1 |

| 14 | 1 | 1 | 1 | 0 | 1 | 1 |

| 15 | 1 | 1 | 1 | 1 | 1 | 1 |

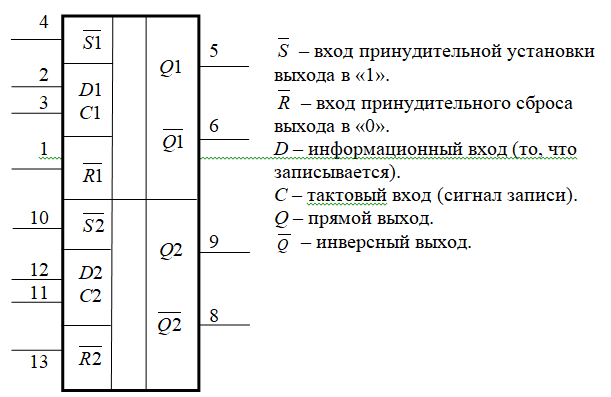

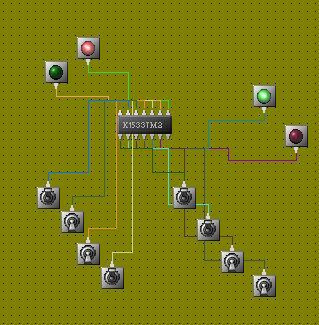

6.4. Изучение схемы включения сдвоенного D-триггера на базе микросхемы 1533ТМ2

6.4.1. Собрать схему включения данной микросхемы (рис. 1.8) и убедиться, что принцип её работы полностью соответствует составленной в п. 3.4.3 таблице истинности.

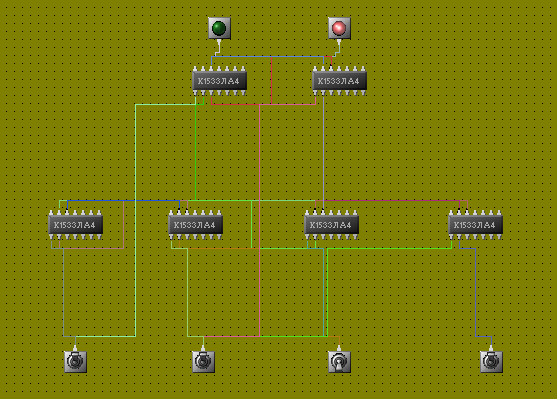

Поместить в отчет схему сборки сдвоенного D-триггера (поле для рис. 1.9.)

Рис. 1.8. УГО микросхемы 1533ТМ2 и сборка сдвоенного D-триггера.

Рис. 1.9. Сборка сдвоенного D-триггера (скриншот).

6.5. Изучение работы Т-триггера, построенного на базе D-триггера

3.5.1. Изменить схему включения синхронного D-триггера для построения Т-триггера, как показано на рис. 1.10. Схему включения Т-триггера и таблицу истинности показать преподавателю и занести в отчёт.

3.5.1. Изменить схему включения синхронного D-триггера для построения Т-триггера, как показано на рис. 1.10. Схему включения Т-триггера и таблицу истинности показать преподавателю и занести в отчёт. Скриншот схемы.

Скриншот схемы.Рис. 1.10. Схема построения Т-триггера на базе синхронного D-триггера.

6.5.2. Составить таблицу истинности работы Т-триггера (табл. 1.7):

Таблица 1.7.

| T | Q | Q(t+1) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

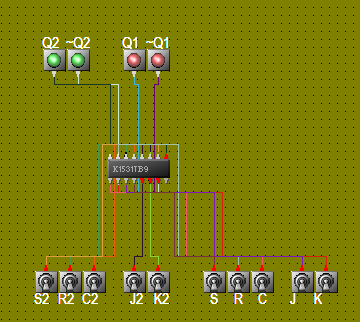

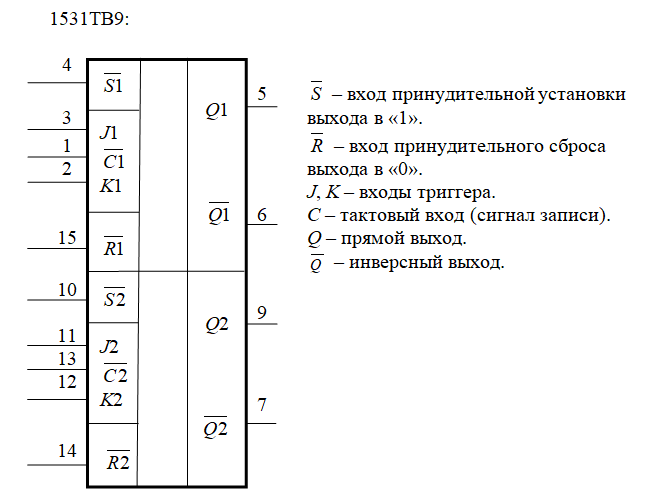

6.6. Изучение работы JK-триггера на базе микросхемы 1531ТВ9

В лабораторной работе рассматривается тактируемый JK-триггер на базе микросхемы 1531ТВ9 (рис. 1.11).

Рис. 1.11. УГО микросхемы 1531ТВ9.

6.6.1. Для открытия готовой схемы в окне программы IC Builder v1.51 выбрать:

Файл → Открыть проект → Триггеры → Триггер - К1531ТВ9 (JK).icb

.

6.6.2. На основании собранной схемы составить таблицу истинности (табл. 1.8.) и убедиться в работоспособности устройства. Пояснить полученные результаты.

Таблица 1.8.

| S | R |  | J | K | Q |  |

| 0 1 0 1 1 1 1 1 | 1 0 0 1 1 1 1 1 | X X X 1 | X X X 0 1 0 1 x | X X X 1 1 0 0 x | 1 0 1* 0 Счётный Q0 1 Q0 | 0 1 1* 1 Режим неQ0 0 неQ0 |

6.6.3. Схему триггера (скриншот), а также таблицу истинности занести в отчёт.