ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 26.03.2024

Просмотров: 85

Скачиваний: 0

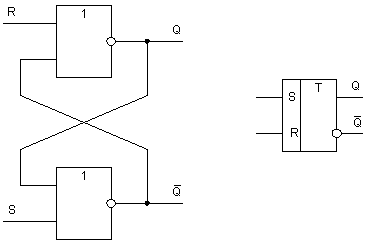

Рисунок 9.4 – Схеми та умовні позначення RS-тригерів

Т аблиця

9.1 – Таблиці істинності асинхронних

RS-тригерів

аблиця

9.1 – Таблиці істинності асинхронних

RS-тригерів

В таблиці 9.1 Qt і Q't позначають рівні, які були на виході тригера до подачі на його входи так званих активних рівнів. Активним називають логічний рівень, що діє на вході логічного елемента і однозначно визначає логічний рівень вихідного сигналу (незалежно від логічних рівнів, що діють на інших входах). Для елементів АБО-НІ за активний рівень приймають високий рівень, а для елементів І-НІ - низький рівень. Рівні, подача яких на один з входів не призводить до модифікації логічного рівня на виході елемента, називають пасивними. Рівні Qt+1 і Q't+1 позначають логічні рівні на виході тригера після подачі інформації на його входи. Для тригера з прямими входами Qt+1=1 при S=1 і R=0; Qt+1=0 при S=0 і R=1; Qt+1=Qt при S=0 і R=0. При R=S=1 стан тригера буде невизначеним (*), бо під час дії інформаційних сигналів логічні рівні на виході тригера однакові Qt+1=Q't+1, а після закінчення їхньої дії тригер може рівноймовірно прийняти будь-який із стійких станів. Тому така комбінація є забороненою.

Режим S=1, R=0 називають режимом запису 1 (бо Qt+1=1); режим S=0 і R=1 - режимом запису 0. Режим S=0, R=0 називається режимом зберігання інформації, бо інформація на виході залишається незмінною. Для тригера з інверсними входами режим запису логічної 1 реалізується при S=0, R=1, режим запису логічного 0 - при S=1, R=0. При S=R=1 забезпечується зберігання інформації. Комбінація S=R=0 є забороненою.

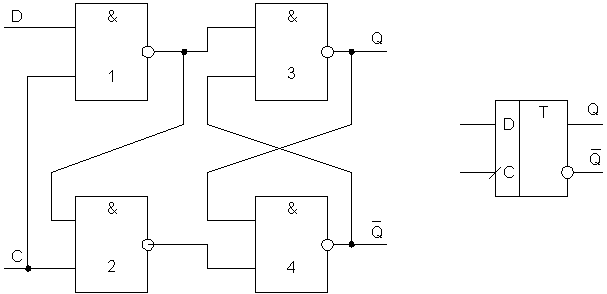

Тактовий D-тригер. Він має інформаційний вихід і вхід синхронізації. Одна із можливих структурних схем однотактного D-тригера і його умовне позначення наведені на рисунку 9.5.

Рисунок 9.5 – Схема та умовне позначення тактового D-тригера

Якщо рівень сигналу на вході С=0, стан тригера стійкий і не залежить від рівня сигналу на інформаційному вході. При цьому на входи RS-тригера з інверсними входами (елементи 3 і 4) надходять пасивні рівні (S=R=1). При подачі на вхід синхронізації рівня С=1 інформація на прямому виході буде повторювати інформацію, що подається на вхід D. Таким чином, при С=0 Qt+1=Qt, а при С=1 Qt+1=D (таблиця 9.2).

Таблиця 9.2 – Таблиця істинності тактового D-тригера

-

D

0

0

1

1

0

1

0

1

0

0

1

1

Тут Qt означає логічний рівень на прямому виході до подачі імпульсу синхронізації, a Qt+1 - логічний рівень на цьому виході після подачі імпульсу синхронізації.

В такому тригері відбувається затримка сигналу на виході по відношенню до сигналу, поданого на вхід, під час паузи між синхросигналами. Для стійкої роботи тригера необхідно, щоб протягом синхроімпульса інформація на вході була незмінною.

Тактові D-тригери можуть бути з потенційним і динамічним управлінням. У перших з них інформація записується протягом часу, при якому рівень сигналу С=1. В тригерах з динамічним управлінням інформація записується тільки протягом перепаду напруги на вході синхронізації. Динамічні входи зображають на схемах трикутником. Якщо верхівка трикутника звернута в сторону мікросхеми, то тригер «спрацьовує» по фронту вхідного імпульсу, якщо від неї - по зрізу імпульсу. В такому тригері інформація на виході може бути затримана на один такт по відношенню до вхідної інформації.

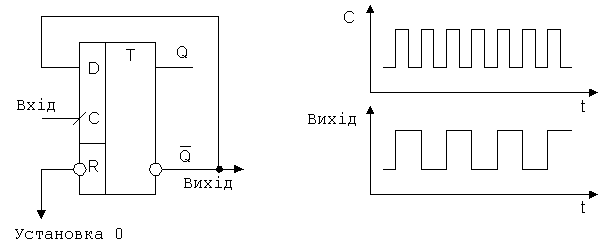

Лічильний Т-тригер (рисунок 9.6). Його називають також тригером зі лічильним входом. Він має один вхід керування Т і два виходи Q і Q'. Інформація на виході такого тригера змінює свій знак на протилежний при кожному позитивному (або при кожному негативному) перепаді напруги на вході. В серії мікросхем, що випускаються, Т-тригерів, як правило, немає. Але тригер такого типу може бути створений на базі тактового D-тригера, якщо його інверсний вихід з'єднати з інформаційним входом. Як видно з діаграми, частота сигналу на виході Т-тригера в два разу нижче частоти сигналу на вході, тому такий тригер можна використовувати як подільник частоти і двійковий лічильник.

Рисунок 9.6 - Лічильний тригер

В серіях мікросхем, що випускаються, є також універсальні JK-тригери. При відповідному під'єднанні вхідної логіки JK-тригер може виконувати функції тригера будь-якого іншого типу.

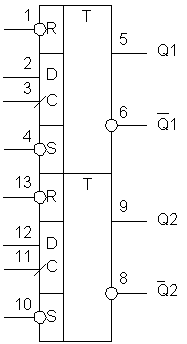

Умовні графічні позначення тригерів на принципових схемах наведені на рисунку 9.7.

Рисунок 9.7 – Графічні позначення тригерів

ЛІЧИЛЬНИКИ

Лічильником називають прилад, призначений для підрахунку числа імпульсів, поданих на вхід. Вони, як і зсувні регістри, складаються з ланцюжка тригерів. Розрядність лічильника, а отже, і число тригерів, визначається максимальним числом, до якого він рахує.

Регістр зсуву можна перетворити в кільцевий лічильник, якщо вихід останнього тригера з'єднати з входом D першого. Схема такого лічильника на N розрядів наведена на рисунку 9.8. Перед початком підрахунку імпульсом початкової установки в нульовий розряд лічильника (Q0) записується логічна 1, в інші розряди — логічні 0. З початком рахунку кожний з лічильних імпульсів Т, що приходять, перезаписує 1 в наступний тригер, і число імпульсів, що надійшли, визначається за номером виходу, на якому є 1. Передостанній (N-1) імпульс переведе в одиничний стан останній тригер, а N-ний імпульс перенесе цей стан на вихід нульового тригера, і підрахунок розпочнеться спочатку. Таким чином, можна побудувати кільцевий лічильник з довільним коефіцієнтом перерахунку (будь-якою основою числення), змінюючи лише число тригерів в ланцюжку.

Рисунок 9.8 – Кільцевий лічильник на регістрі зсуву

Недолік

такого лічильника - велике число тригерів,

необхідних для його побудови. Більш

економічні, а тому і більш розповсюджені

лічильники, які побудовані на лічильних

Т-тригерах. Після кожного тактового

імпульсу Т сигнал на вході D змінюється

на протилежний і тому частота вихідних

імпульсів вдвічі менша частоти імпульсів,

що надходять. Зібравши послідовний

ланцюжок з n лічильних тригерів (з'єднуючи

вихід попереднього тригера із входом

С наступного), ми отримаємо частоту

![]() .

При цьому кожний вхідний імпульс змінює

код числа на виході лічильника на 1 в

інтервалі від 0 до

.

При цьому кожний вхідний імпульс змінює

код числа на виході лічильника на 1 в

інтервалі від 0 до![]() .

.

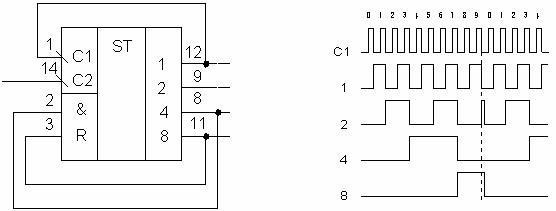

Мікросхема К555ИЕ5 (рисунок 9.9) містить лічильний тригер (вхід С1) і подільник на вісім (вхід С2), створений трьома з'єднаними послідовно тригерами. Тригери спрацьовують по зрізу вхідного імпульсу (по переходу з 1 в 0). Якщо з'єднати послідовно всі чотири тригери, то одержимо лічильник за модулем 24=16. Максимальне число, що зберігається в лічильнику при повному заповненні його одиницями дорівнює N=24-1=15=(1111)2. Такий лічильник працює з коефіцієнтом рахунку К (модулем), кратним цілій степені 2, і в ньому відбувається циклічний перебір К=2n стійких станів. Лічильник має входи примусової установки в 0.

Рисунок 9.9 – Лічильник з коефіцієнтом перерахування 16 і його часова діаграма

Часто потрібні лічильники з числом стійких станів, відмінним від 2n. Наприклад, в електронних годинниках є мікросхеми з коефіцієнтом рахунку 6 (десятки хвилин), 10 (одиниці хвилин), 7 (дні тижня), 24 (години). Для побудови лічильника з модулем К ≠ 2n можна використати прилад з n тригерів, для якого виконується умова 2n>K. Очевидно, такий лічильник може мати зайві стійкі стани (2n-К). Виключити ці непотрібні стани можна використанням зворотних зв'язків, по колах яких лічильник перемикається в нульовий стан в тому такті роботи, коли він дораховує до числа К.

Для лічильника з К=10 потрібні чотири тригери (бо 23<10<24). Лічильник повинен мати десять стійких станів N=0, 1, ..., 8, 9. В тому такті, в якому він повинен був би перейти в одинадцятий стійкий стан (N=10), його необхідно перевести в вихідний нульовий стан. Для такого лічильника можна використати мікросхему К555ИЕ5 (рисунок 9.10), ввівши коло зворотного зв'язку з виходу лічильника, відповідних числу 10 (тобто 2 і 8), на входи установки лічильника в 0 (вхід R). В самому початку 11-го стану (число 10) на обох входах елемента і мікросхеми з'являються логічні одиниці (так звана «просічка» на виході «2»), що генерує сигнал переводу всіх тригерів лічильника в нульовий стан.

Рисунок 9.10 – Двійково-десятковий лічильник і часова діаграма його роботи

В усіх серіях цифрових мікросхем є лічильники з внутрішньою організацією найбільш «ходових» коефіцієнтів перерахування, наприклад в мікросхемах К555ИЕ2 і К555ИЕ6 К=10, в мікросхемі К555ИЕ4 К=2×б=12.

Як видно з схем і діаграм (рисунки 9.8 – 9.10), лічильники можуть виконувати функції подільників частоти, тобто приладів, що формують з імпульсної послідовності з частотою fвх імпульсну послідовність, на виході останнього тригера, з частотою fвих, в К разів меншу за вхідну. При такому використанні лічильників немає необхідності знати, яке число в ньому записане в поточний момент, тому подільники в деяких випадках можуть бути значно простіші за лічильники. Наприклад, мікросхема К555ИЕ1 - це подільник на 10, а К555ИЕ8 - подільник із змінним коефіцієнтом ділення К=64/n, де n=1....63.

Крім розглянутих лічильників, що підсумовують, широко застосовують реверсивні лічильники на мікросхемах К555ИЕ6, К555ИЕ7, у яких в залежності від режиму роботи вміст лічильника або збільшується на одиницю (режим додавання), або зменшується на одиницю (режим віднімання) після приходу чергового лічильного імпульсу.

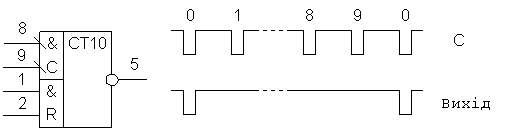

Мікросхема К555ИЕ1 (рисунок 9.11) – подільник на 10. Установка її тригерів в 0 здійснюється одночасною подачею високого рівня на входи 1 і 2 (елемент І). Лічильні імпульси подають на вхід 8 або 9 (при цьому на іншому вході повинен бути високий рівень), або водночас на обидва входи (елемент і).

Рисунок 9.11 – Подільник частоти

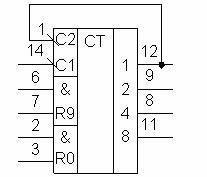

У склад мікросхеми К555ИЕ2 (рисунок 9.13) входять тригер з лічильним входом (вхід С1) і подільник на 5 (вхід С2). При з‘єднанні виходу лічильного тригера із входом С2 утвориться двійково-десятковий лічильник (діаграма його роботи аналогічна діаграмі на рисунку 9.10). Підрахунок відбувається по зрізу імпульсу. Лічильник має входи установки в 0 (R0 з логікою І) і входи установки в 9 (R9 з логікою І).

Рисунок 9.12 – Двійково-десятковий лічильник

В мікросхему К555ИЕ4 (рисунок 9.13) входять лічильний тригер і подільник на 6.

Рисунок 9.13 – Лічильник на мікросхемі К555ИЕ4 та часова діаграма його роботи

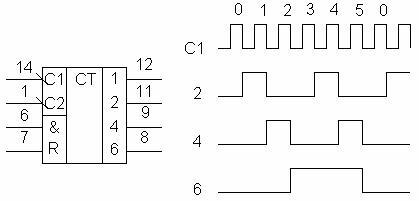

Мікросхеми К555ИЕ6 і К555ИЕ7 – реверсивні лічильники з попереднім записом; перший із них - двійково-десятковий, другий – чотири розрядний двійковий. Установка їх в 0 відбувається при високому рівні на вході R. В лічильник можна записати число, двійковий код якого поданий на входи D1-D4 (в К555ИЕ6 від 0 до 9, в К555ИЕ7 від 0 до 15). Для цього на вхід S необхідно подати низький рівень (на входах С1 і С2 - високий рівень, на вході R - низький). Рахування почнеться із записаного числа по імпульсах низького рівня, що подаються на вхід С1 (в режимі додавання) або С2 (в режимі віднімання). інформація на виході змінюється по фронту лічильного імпульсу. При цьому на другому лічильному вході і вході S повинен бути високий рівень, на вході R - низький, а стан входів D байдужий. Водночас з кожним десятим (шістнадцятим) на вході С1 імпульсом на виході Р1 з'являється вихідний імпульс, який його повторює, що може подаватися на вхід наступного лічильника. В режимі віднімання водночас з кожним імпульсом на вході С2, що переводить лічильник в стан 9 (15), на виході Р2 з'являється вихідний імпульс. Часова діаграма роботи лічильника наведена на рис. 9.15. На діаграмі в режимі паралельного запису (S=0) було записане число 6 (високий рівень на входах D2 і D3).