ВУЗ: Томский государственный университет систем управления и радиоэлектроники

Категория: Учебное пособие

Дисциплина: Дискретная математика

Добавлен: 28.11.2018

Просмотров: 16648

Скачиваний: 202

196

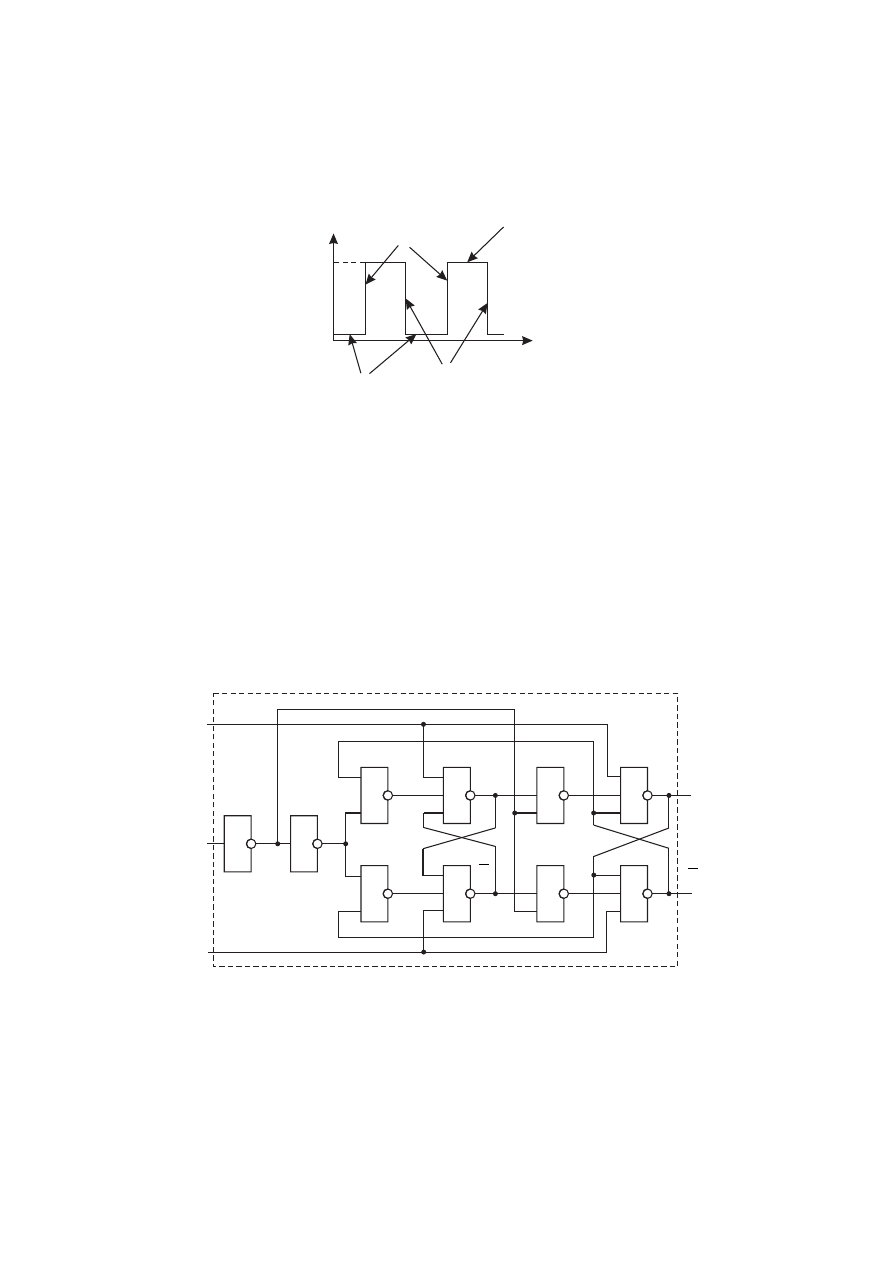

В теории дискретных автоматов используются в основном прямоугольные им-

пульсы (рис. 10.1).

Рис. 10.1

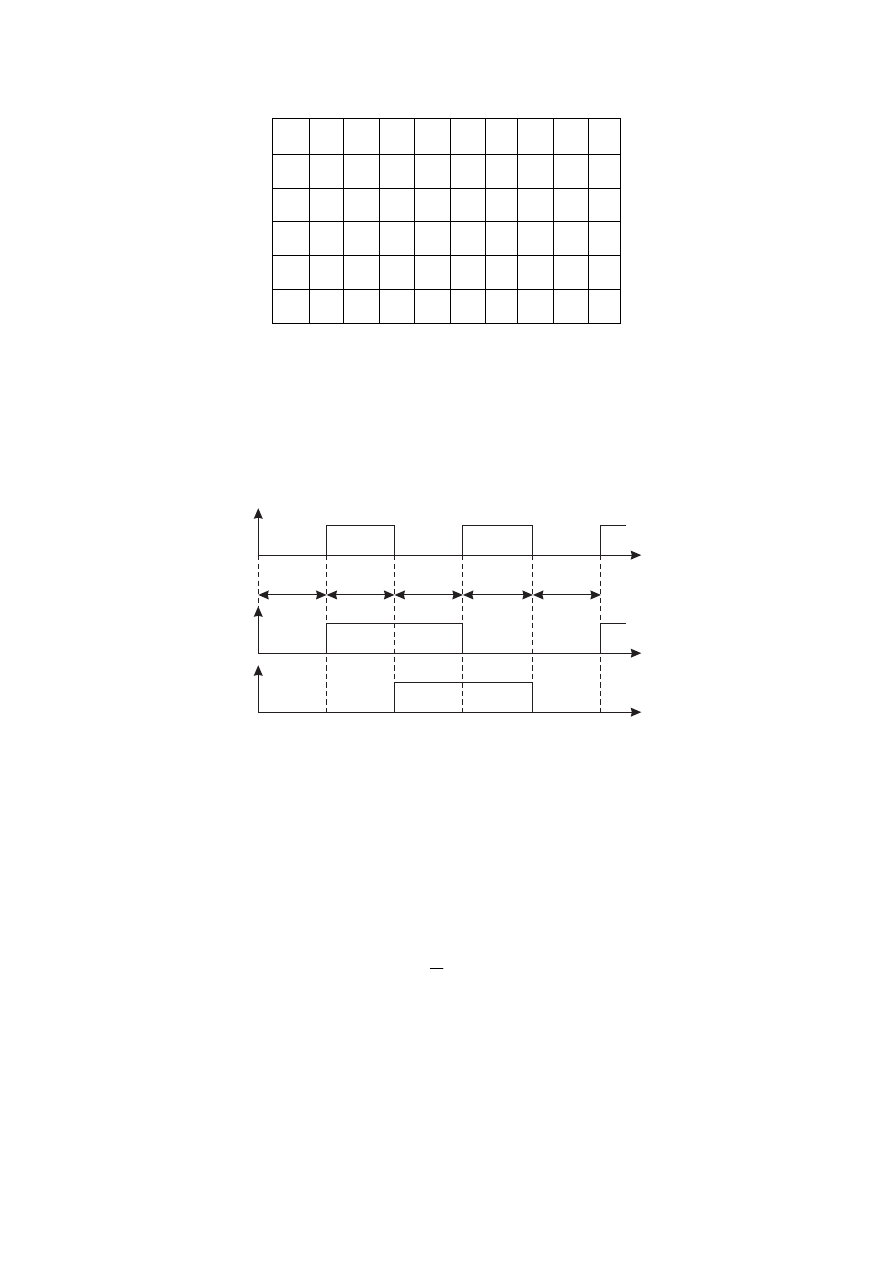

Один из вариантов логической схемы Т-триггера представлен на рисун-

ке 10.2. Он состоит из двух RS-триггеров P и Q, соединенных между собой

комбинационными схемами, состоящими из логических элементов Шеффера 3,

4, 5, 6. Триггер P называется ведущим, а триггер Q – ведомым. Пусть исходным

является состояние

P = Q = 0; S = R = 1.

Рис. 10.2

Сначала предположим, что T = 0, тогда

ϕ

1

= 1, ϕ

2

= 0; ϕ

3

= ϕ

4

= 1, ϕ

5

= 1, ϕ

6

= 0.

Эти значения отмечены в первой строке таблицы 10.1. Кроме того, в ней

указано:

P = Q = 0.

U

t

5

0

Высокий

уровень

Передний

(положительный)

фронт

Задний

(отрицательный)

фронт

Низкий

уровень

S

P

Q

T

R

1

1

1

2

& φ

3

3

& φ

4

4

& P

&

& φ

5

5

& φ

6

6

&

Q

&

φ

1

φ

2

197

Таблица 10.1

№ T ϕ

1

ϕ

2

ϕ

3

ϕ

4

P ϕ

5

ϕ

6

Q

1 0 1 0 1 1 0 1 0 0

2 1 0 1 0 1 1 1 1 0

3 0 1 0 1 1 1 0 1 1

4 1 0 1 1 0 0 1 1 1

5 0 1 0 1 1 0 1 0 0

Состояние P = 0 обусловлено тем, что ϕ

3

= ϕ

4

= S = R = 1 (режим хранения

информации), а Q = 0, благодаря тому, что ϕ

6

= 0. Состояния T, P и Q отмечены

на рисунке 10.3. На нём изображена диаграмма выходов триггеров P и Q, где

показано, что при T = 0 (зона 1) триггеры P и Q находятся в состоянии нуля.

Рис. 10.3

Подадим на вход Т высокий уровень. Низким уровнем выходного напря-

жения элемента 1 окажутся запертыми схемы 5 и 6, вследствие чего:

ϕ

5

= ϕ

6

= 1,

и триггер Q перейдёт в режим хранения информации, оставшись в нулевом со-

стоянии. Элементы 3 и 4 со стороны ϕ

2

окажутся открытыми. На вход элемен-

та 4 с прямого выхода триггера Q поступил низкий уровень напряжения, а на

вход элемента 3 с инверсного выхода

Q

– высокий уровень. Следовательно:

ϕ

3

= 0; ϕ

4

= 1.

Так как ϕ

3

= 0, то триггер P перешёл в единичное состояние.

Все эти значения приведены во второй строке таблицы 10.1, а на рисун-

ке 10.3 в зоне 2, обозначенной надписью «1-й имп.» (т. е. первый импульс), от-

мечено, что при T = 1 триггер P находится в единичном состоянии, а Q – в ну-

левом. Таким образом, в момент положительного фронта входного импульса

T

0

P

0

0

Q

t

t

t

1-й имп.

2 й имп.

-

1

2

3

4

5

T = 0

T = 1

T = 0

T = 1

T = 0

198

триггер P перешёл в единичное состояние, а ведомый триггер Q остался в со-

стоянии нуля.

Подадим на вход Т низкий уровень напряжения. На выходе элемента 2

получим низкий уровень. Триггер P перейдёт в режим хранения информации

(так как ϕ

3

= ϕ

4

= 1), оставшись в единичном состоянии. С выхода элемента 1 на

входы элементов 5 и 6 поступит высокий уровень. Поскольку P = 1 и ϕ

1

= 1, то

ϕ

5

= 0, ϕ

6

= 1.

Триггер Q перейдёт в единичное состояние.

Все перечисленные изменения записаны в строке 3 таблицы 10.1. На ри-

сунке 10.3 этой строке соответствует зона 3, где отмечено, что при T = 0 триг-

геры P и Q находятся в единичном состоянии. Таким образом, с приходом от-

рицательного фронта входного импульса оба триггера окажутся в состоянии

единицы.

Если на вход триггера подать второй импульс, то триггеры P и Q перей-

дут в нулевое состояние. На этом заканчивается полный цикл работы T-

триггера. Состоит он из двух тактов. Под действием положительного фронта

меняет состояние ведущий триггер P (первый такт). С приходом отрицательно-

го фронта меняет состояние ведомый триггер Q (второй такт). В связи с этим T-

триггер называют двухтактным.

Условное изображение T-триггера приведено на рисунке 10.4. Надпись TT

на этом рисунке говорит о том, что триггер является двухтактным, т. е. содер-

жит два RS-триггера, из которых один реагирует на положительный перепад

входного напряжения, второй – на отрицательный. А так как к ведущему триг-

геру доступа нет, то о состоянии T-триггера можно судить лишь по уровням

напряжения на выходах ведомого RS-триггера: T-триггер меняет состояние под

действием только отрицательного фронта входного импульса, а на положитель-

ный фронт T-триггер не реагирует.

Рис. 10.4

T

R

S TT

Q

Q

199

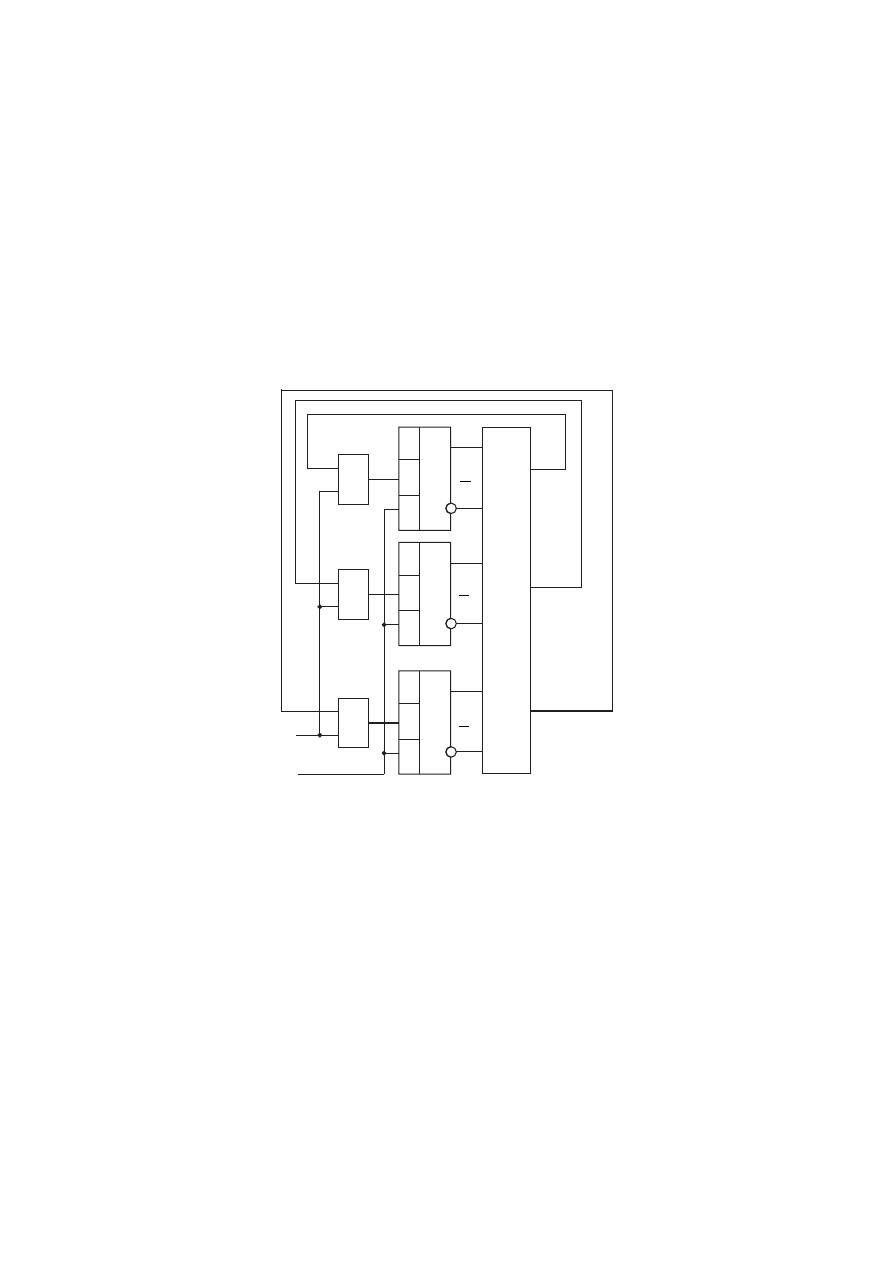

10.3 Синтез синхронного автомата на Т-триггерах

В схеме синхронного автомата тактовый (синхронизирующий) импульс

непосредственно управляет каждым триггером (рис. 10.5). Тактовые импульсы

поступают на один из входов элементов И, выходы которых подключены к

счетным входам триггеров А

1

, А

2

, …, А

n

. Ко вторым входам схем

И присоединены выходы комбинационной схемы, представляющей собой пре-

образователь входного n-разрядного двоичного кода в n-разрядный выходной

код, разряды которого обозначены символами f

1

, f

2

, …, f

n

. Буквой Y обозначена

шина установки автомата в исходное (нулевое) состояние.

Рис. 10.5

Зафиксируем какой-либо момент времени между синхроимпульсами, ко-

гда ϕ = 0. Триггеры находятся в некоторых состояниях, образующих набор зна-

чений аргументов А

1

, А

2

, …, А

n

. Этому набору на выходах f

1

, f

2

, …, f

n

соответ-

ствует набор высоких и низких уровней. Когда на вход ϕ поступит

синхроимпульс, он пройдет только через те схемы И, на которые поданы высо-

кие уровни с выходов f

1

, f

2

, …, f

n

. Задача синтеза автомата сводится к построе-

нию комбинационной схемы, распределяющей тактовые импульсы по входам

триггеров так, чтобы автомат менял свои состояния в соответствии с заданны-

ми условиями.

Метод построения такого автомата проиллюстрируем на примере четы-

рёхразрядного синхронного реверсивного счётчика: если А = 0, то счёт ведётся

Y

R

S TT

1

A

T

А

1

&

R

S TT

2

A

T

А

2

&

R

S TT

n

A

T

А

n

&

φ

f

1

f

2

f

n

...

...

...

К

о

мбинационнаяс

х

ем

а

200

в прямом направлении по замкнутому циклу: 0, 1, 2, 3, 4, 5, 6, 7, 0, …; при А = 1

счёт ведётся в обратной последовательности: 7, 6, 5, 4, 3, 2, 1, 0, 7, … .

Очевидно, что для схемы необходимо четыре триггера: из них триггер

А переключает направления счета, а для реализации собственно счета необхо-

димо ещё три триггера B, C, D. Составим таблицу переходов (табл. 10.2).

Таблица 10.2

Дес. A B C D

f

B

f

C

f

D

0

0 0 0 0 0 0 1

1

0 0 0 1 0 1 1

2

0 0 1 0 0 0 1

3

0 0 1 1 1 1 1

4

0 1 0 0 0 0 1

5

0 1 0 1 0 1 1

6

0 1 1 0 0 0 1

7

0 1 1 1 1 1 1

8

1 0 0 0 1 1 1

15

1 1 1 1 0 0 1

14

1 1 1 0 0 1 1

13

1 1 0 1 0 0 1

12

1 1 0 0 1 1 1

11

1 0 1 1 0 0 1

10

1 0 1 0 0 1 1

9

1 0 0 1 0 0 1

В средней части таблицы, где приведены колонки, обозначенные логиче-

скими переменными А, В, С, D, записаны состояния автомата. Когда А = 0, ав-

томат ведет счет в прямом направлении: 000, 001, 010, …, 111, а когда А = 1, то

счет идет в обратной последовательности: 000,111, 110, …, 001.

В левой колонке, обозначенной «Дес.» (десятичные числа), указаны деся-

тичные эквиваленты четырехзначных двоичных чисел, записанных в строках

таблицы. При этом учитывается и переключающий триггер A.

Правая часть таблицы 10.2 содержит колонки f

B

, f

C

, f

D

. Это выходы ком-

бинационной схемы, управляющей триггерами В, С, D.