Файл: Перечень ответов на вопросы к промежуточному зачету по дисциплине Организация эвм и вс.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 07.11.2023

Просмотров: 253

Скачиваний: 4

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Последовательность исполнения команды.

Цикл процессора

Цикл процессора - процесс обработки каждой команды, состоящий из двух этапов: выборка и исполнение.

Выборка команды

Когда устройство управления завершит выполнение текущей команды, оно должно выбрать следующую команду из памяти в Регистр команд (РгК).

Адрес следующей команды содержится в специальном регистре, называемом Счетчиком Команд (СчК).

Всякий раз при выборке команды устройство управления одновременно увеличивает содержимое СчК на единицу, чтобы после выполнения текущей команды можно было произвести выборку следующей.

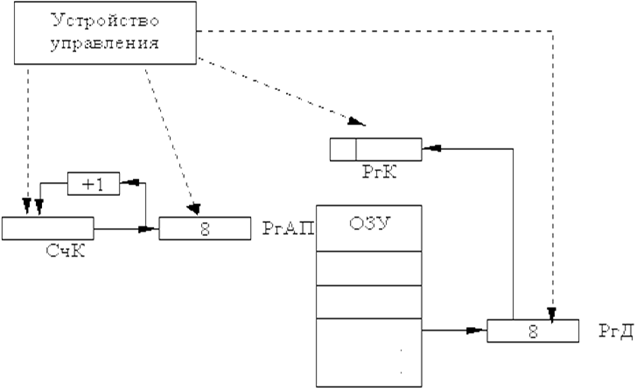

Таким образом, устройство управления работает с коман-дами в порядке, в котором они помещены в ОЗУ. Подобная ситуация иллюстрируется на рис. 5.8.

Последовательность выборки команды:

а) копируется адрес следующей команды из СчК в Регистр адреса памяти (РгАП) (адрес 8 в примере на рис.5.8);

б) прибавляется 1 к содержимому СчК СчК:=СчК+1 ( 9 );

в) содержимое ячейки (команда), кото-рая адресуется РгАП, пересылается в Регистр данных (РгД);

г) содержимое РгД копируется в Регистр команд (РгК).

Этим выборка завершается.

Исполнение команды

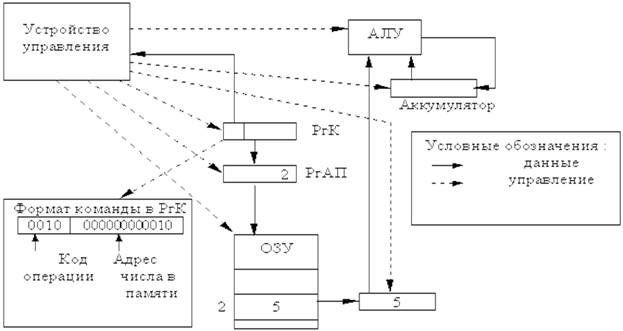

Взаимодействие блоков процессора при выполнении команды (например: СЛОЖЕНИЕ) схематично показано на рис. 5.7.

Рис. 5.7. Взаимодействие блоков процессора при выполнении команды СЛОЖЕНИЕ

Для временного хранения машинной команды используется специальный регистр, содержимое которого интерпретируется как команда - Регистр Команды (РгК).

Команда, записанная в РгК, имеет две части: функциональную и адресную.

Последовательность выполнения команды:

а) устройство управления декодирует функциональную часть команды, интерпретируя ее как операцию сложения;

б) адрес операнда из адресной части РгК пересылается в РгАП;

в) устройство управления инициирует чтение операнда из ячейки, адрес которой находится в РгАП, и загрузку операнда в РгД. Таким образом, 5 из второй ячейки оказывается в регистре данных.

г) АЛУ выполняет операцию (сложение) над содержимым РгД и аккумулятора. А результат по сигналу устройства управления будет занесен в аккумулятор. Таким образом, к концу команды сложения содержимое аккумулятора равно 11.

Этим завершается выполнение команды.

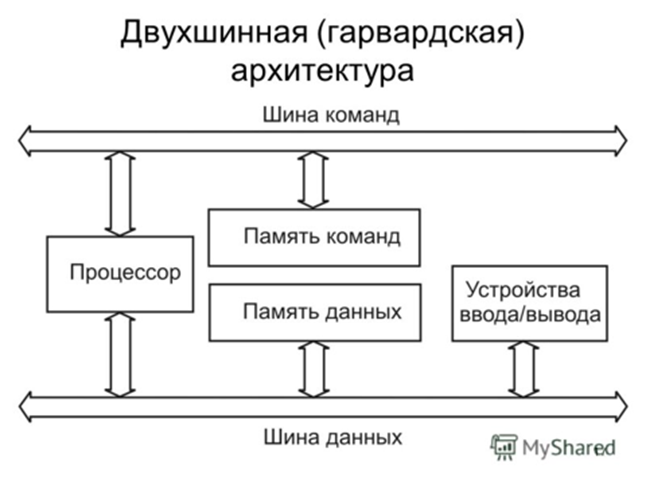

6. Гарвардская архитектура (классическая, модифицированаая, расширенная)

Гарвардская архитектура —архитектура ЭВМ, отличительными признаками которой являются:

-

хранилище инструкций и хранилище данных представляют собой разные физические устройства; -

канал инструкций и канал данных также физически разделены.

классикка - Типичные операции (сложение иумножение) требуют от любого вычислительного устройства нескольких действий:

-

выборку двухоперандов; -

выборинструкции и её выполнение; -

сохранение результата.

модифицированная - Соответствующая схема реализации доступа к памяти имеет один очевидный недостаток — высокую стоимость. При разделении каналов передачи команд и данных на кристаллепроцессора последний должен иметь почти вдвое больше интерфейсныхвыводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Способом разрешения этой проблемы стала идея использовать общие шину данных и шину адреса для всех внешних данных, а внутри процессора использовать шину данных, шину команд и две шины адреса. Такую концепцию стали называть модифицированной гарвардской архитектурой.

расширенная - Часто требуется выбрать три составляющие: два операнда и инструкцию (в алгоритмах цифровой обработки сигналов это наиболее распространенная задача вБПФ-,КИХ- иБИХ-фильтрах). Для этого существуеткэш-память. В ней может храниться инструкция — следовательно, обе шины остаются свободными и появляется возможность передать два операнда одновременно. Использование кэш-памяти вместе с разделёнными шинами получило название «Super Harvard Architecture» («SHARC») — расширенная гарвардская архитектура.

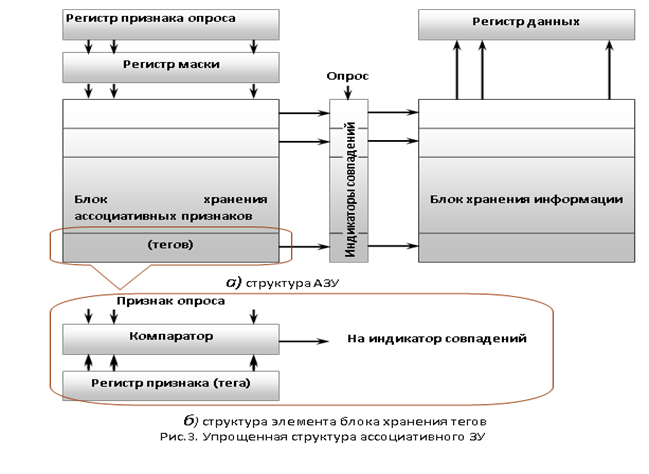

7. Ассоциативные ЗУ (АЗУ). Ассоциативный поиск данных. Структура АЗУ.

Ассоциативное запоминающее устройство – безадресное ЗУ, в котором выборка (запись) производится не по конкретному адресу, а по заданному сочетанию (ассоциации) признаков, свойственных искомой информации. В ассоциативных ЗУ поиск осуществляется по признаку, связанному не с местоположением информации, а с самой информацией. Если в ассоциативном

ЗУ переписать информацию из одной ячейки в другую и не сообщить об этом процессу, то никакой потери информации не произойдет, информация будет найдена.

Ассоциативные ЗУ следует различать с ассоциативным поиском данных. Ассоциативный поиск можно реализовать программно в обычном адресном ЗУ. Примером ассоциативного поиска может служить поиск файла по имени. В ассоциативном ЗУ ассоциативный поиск реализован аппаратно.

Структура ассоциативного ЗУ:

Регистр маски позволяет исключить из поиска определенные биты.

Особенностями ассоциативных ЗУ являются:

· Большая емкость за счет блока хранения тегов. Емкость ассоциативного ЗУ не должна превышать 2n информационных слов, где n – разрядность тега;

· Возможность многозначного ответа – случай, когда несколько ассоциативных признаков совпадает с признаком опроса;

· Возможность организовать сложный поиск – имеет целью решение общей задачи поиска - найти слова, ассоциативные признаки (теги) которых удовлетворяют заданной комбинации логических отношений к признаку опроса. Одной из основ сложного поиска является упорядоченная выборка – выборка в порядке возрастания (или убывания) численного значения ассоциативных признаков (тегов).

8. Принцип программного управления

Основным принципом построения всех современных ЭВМ является программное управление. В основе его лежит представление алгоритма решения любой задачи в виде программы вычислений. Принцип программного управления может быть осуществлен различными способами.

Стандартом для построения практически всех ЭВМ стал способ, описанный Дж. фон Нейманом в 1945 г. при построении еще первых образцов ЭВМ. Суть его заключается в следующем.

1. Все вычисления, предписанные алгоритмом решения задачи, должны быть представлены в виде программы, состоящей из последовательности управляющих слов-команд.

2. Каждая команда содержит указания на конкретную выполняемую операцию, место нахождения (адреса) операндов и ряд служебных признаков. Операнды – переменные, значения которых участвуют в операциях преобразования данных.

3. Список (массив) всех переменных (входных данных, промежуточных значений и результатов вычислений) является еще одним неотъемлемым элементом любой программы.

Для доступа к программам, командам и операндам используются их адреса. В качестве адресов выступают номера ячеек памяти ЭВМ, предназначенных для хранения объектов. Информация (командная и данные: числовая, текстовая, графическая и т.п.) кодируется двоичными цифрами 0 и 1. Поэтому различные типы информации, размещенные в памяти ЭВМ, практически неразличимы, идентификация их возможна лишь при выполнении программы, согласно ее логике, по контексту.

Каждый тип информации имеет форматы – структурные единицы информации, закодированные двоичными цифрами 0 и 1. Обычно все форматы данных, используемые в ЭВМ, кратны байту, т.е. состоят из целого числа байтов. Последовательность битов в формате, имеющая определенный смысл, называется полем. Например, в каждой команде программы различают поле кода операций, поле адресов операндов. Применительно к числовой информации выделяют знаковые разряды, поле значащих разрядов чисел, старшие и младшие разряды.

9. Суперконвейерные, суперскалярные процессоры.

Суперконыейерные процессоры – процессоры, в которых для повышения производительности повышается тактовая частота. Суперконвейеризациясводится к увеличению количества ступеней конвейера, как за счет добавления новых ступеней, так и путем дробления уже имеющихся ступеней на несколько простых подступеней. В каждой из подступеней операции реализуются с помощью наиболее простых технических средств и с минимальными затратами времени, что позволяет увеличить тактовую частоту внутри конвейера.

Суперконвейерный подход – применение относительно длинных конвейеров с довольно большим числом коротких ступеней; увеличение количества ступеней конвейера может быть достигнуто как за счет добавления новых ступеней, так и путем дробления имеющихся ступеней на несколько простых подступеней. Главное требование – возможность реализации операции в каждой подступени наиболее простыми техническими средствами, а значит, с минимальными затратами времени, вторым, не менее важным, является одинаковость задержки во всех подступенях. Идеология суперконвейерного подхода эффективна, если выполнение потока команд в конвейере не нарушается командами перехода, когда конвейер приходится запускать вновь, что приводит к большим задержкам. Критерием для причисления процессора к суперконвейерным служит число ступеней в конвейере команд – их должно быть больше шести. Таким первым серийным процессором считается MIPS R4000 (8 ступеней), где суперконвейеризация стала следствием разбиения этапов выборки команды и выборки операнда, а также введения в конвейер дополнительного этапа проверки тега.

Суперскалярные процессоры – процессоры, имеющие в своем составе более одного конвейера, называются суперскалярными. Такие процессоры выполняют одновременно более, чем одну скалярную команду. Это достигается за счет включения в состав ЦП нескольких

самостоятельных функциональных блоков, каждый из которых отвечает за свой класс операций и может присутствовать в процессоре в нескольких экземплярах. Суперскалярность предполагает параллельную работу нескольких функциональных блоков, что возможно лишь при одновременном выполнении нескольких скалярных команд. Последнее условие хорошо сочетается с конвейерной обработкой, при этом желательно, чтобы таких конвейеров было несколько, например, два или три. Разумеется, в этом случае ступень выборки команд, общая для всех конвейеров, должна в каждом такте извлекать из памяти сразу несколько команд. За этой ступенью располагается блок диспетчеризации, отвечающий за распределение команд по конвейерам.

10. Классификация, структуры, функции устройств управления ЭВМ.

Классификация ЭВМ

- по принципу действия (форма представления информации, с которой они работают)

1. Аналоговые (АВМ) - вычислительные машины непрерывного действия, работают с информацией, представленной в непрерывной (аналоговой) форме, т.е. в виде непрерывного ряда значений какой-либо физической величины (чаще всего электрического напряжения).

2. Цифровые (ЦВМ) - вычислительные машины дискретного действия, работают с информацией, представленной в дискретной, а точнее, в цифровой форме.

3. Гибридные (ГВМ) - вычислительные машины комбинированного действия, работают с информацией, представленной и в цифровой, и в аналоговой форме.

- по назначению.

1. Универсальные (общего назначения) - предназначены для решения самых различных технических задач, экономических, математических, информационных и других задач, отличающихся сложностью алгоритмов и большим объемом обрабатываемых данных.

2. Проблемно-ориентированные - служат для решения более узкого круга задач, связанных, как правило, с управлением технологическими объектами; регистрацией, накоплением и об-работкой относительно небольших объемов данных; выполнением расчетов по относитель-но несложным алгоритмам;

3. Специализированные - используются для решения узкого круга задач или реализации строго определенной группы функций.

- по размерам и функциональным возможностям.