Файл: Перечень ответов на вопросы к промежуточному зачету по дисциплине Организация эвм и вс.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 07.11.2023

Просмотров: 255

Скачиваний: 4

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

принудительная адресация) либо автоматическим увеличением на единицу адреса текущей микрокоманды (естественная адресация).

В общем случае средства адресации микрокоманд должны обеспечивать формирование:

1. произвольного значения адреса;

2. за минимальное время;

3. при сравнительно небольших затратах оборудования.

Ни естественная, ни принудительная адресации не удовлетворяют перечисленным требованиям.

Естественная адресация удовлетворяет пунктам 2 и 3, но не позволяет простыми средствами обеспечить выполнение п.1, что является существенным при реализации переходов.

Принудительная адресация требует значительно больших затрат микропрограммной памяти для хранения адресов.

45.Многонаправленные переходы. Способы их реализации.

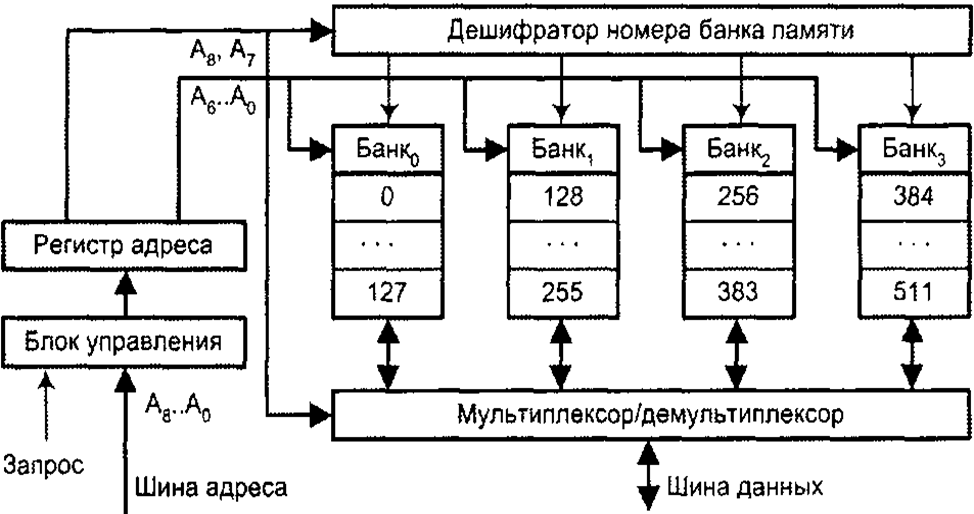

В микропрограммировании значительно чаще, чем в обычном программировании встречаются многонаправленные переходы, когда направление перехода зависит от нескольких признаков.

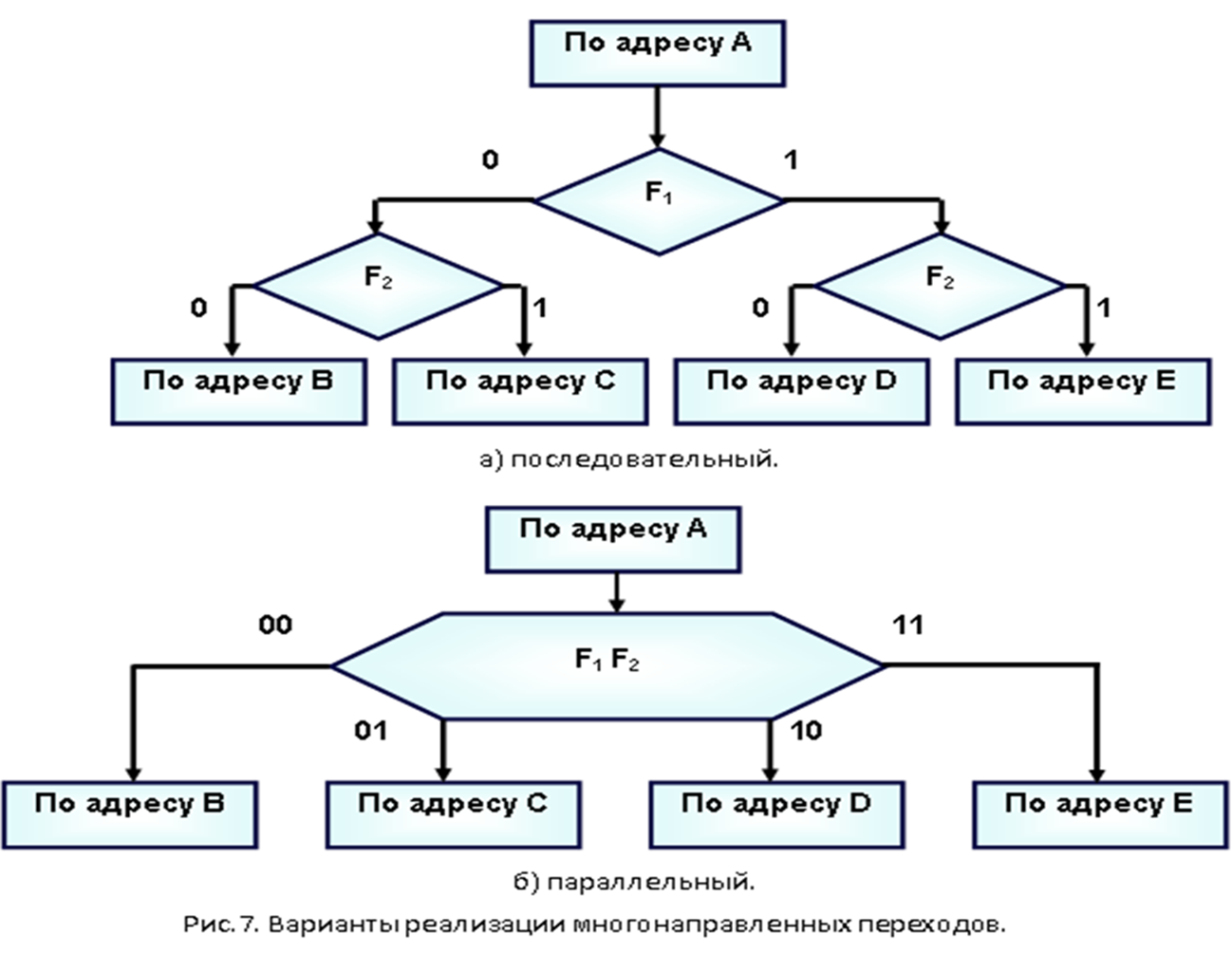

На рисунке 7 показаны два способа реализации многонаправленного перехода – последовательный и параллельный.

В такой ситуации при параллельной реализации проблема формирования произвольного адреса становится достаточно сложной.

Задание нескольких адресов в адресном поле неприемлемо, поскольку микропрограммная память будет использоваться крайне неэффективно. (Выполнение много-направленных переходов за один такт требует наличия у секвенсора нескольких входов тестирования признаков)

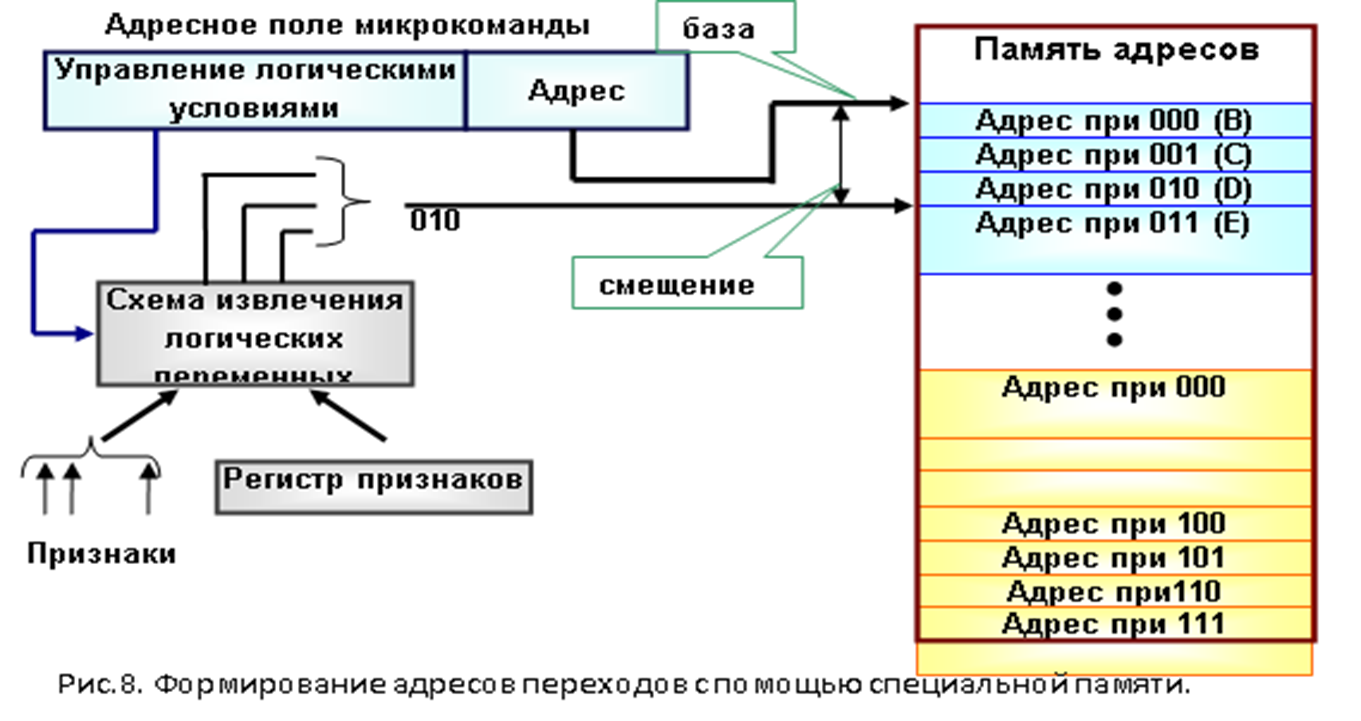

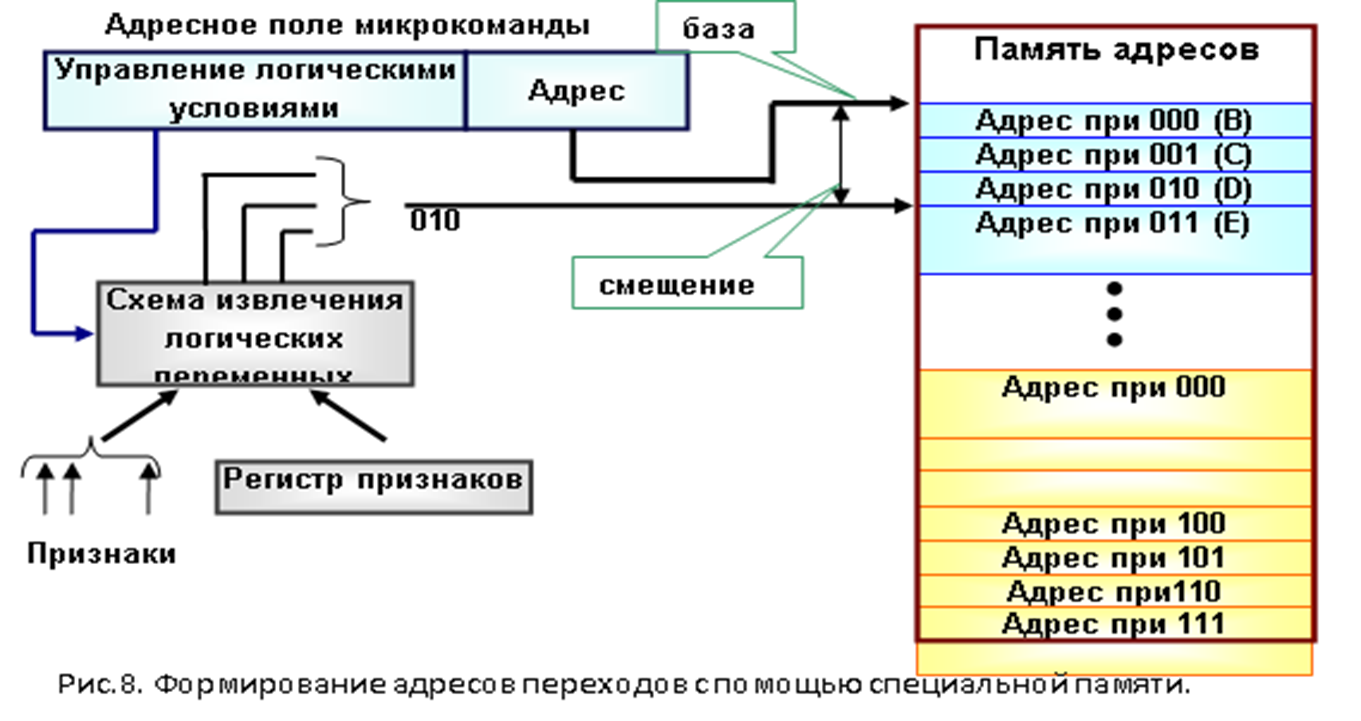

Один из наиболее удачных методов формирования адресов нескольких направлений заключается в использовании дополнительной памяти, как это показано на рис.8.

В адресном поле микрокоманды задаётся не адрес следующей микрокоманды, а указывается начало области адресов переходов в этой памяти для данного случая.

Совокупность значений признаков является смещением, тем самым, указывая на конкретную ячейку, в которой хранится адрес требуемой микрокоманды.

Поле управления логическими условиями определяет правило формирования и количество анализируемых признаков.

Следует отметить, что время, затрачиваемое на формирование адреса, по сравнению с тем, как если бы адреса указывались в микрокоманде, будет больше.

46.Виды микропрограммного управления.

Применяемые в микрокомандах варианты кодирования сигналов управления можно свести к трем типам: горизонтальное, вертикальное и смешанное микропрограммирование.

При горизонтальном микропрограммировании каждому функциональному сигналу в поле код микрооперации ставится в соответствие один разряд.

Это позволяет в рамках одной микрокоманды формировать любые сочетания функциональных сигналов, чем обеспечивается максимальный параллелизм (максимальная производительность) выполнения микроопераций.

При вертикальном кодировании каждой микрооперации присваивается определенный код.

Этот код и заносится в поле код микрооперации, которое имеет минимальную длину. Такой способ кодирования требует минимальных аппаратных зат-рат ПМ, однако возникает необходимость в дешифраторе, преобразующем код микрооперации в соответствующий сигнал управления.

В зависимости от принципа разбиения микроопераций на группы различают два вида смешанного микропрограммирования:

Горизонтально-вертикальное (более распространено) и вертикально-горизонтальное.

В горизонтально-вертикальном методе в каждую группу включаются взаимно несовместимые микрооперации, то есть такие, которые никогда не встречаются вместе в одной микрокоманде. При этом сигналы, обычно формируемые в одном и том же такте, оказываются в разных группах. Внутри каждой группы сигналы управления кодируются вертикальным способом, а группы – горизонтальным способом.

47.Способы повышения быстродействия микропрограммных устройств управления.

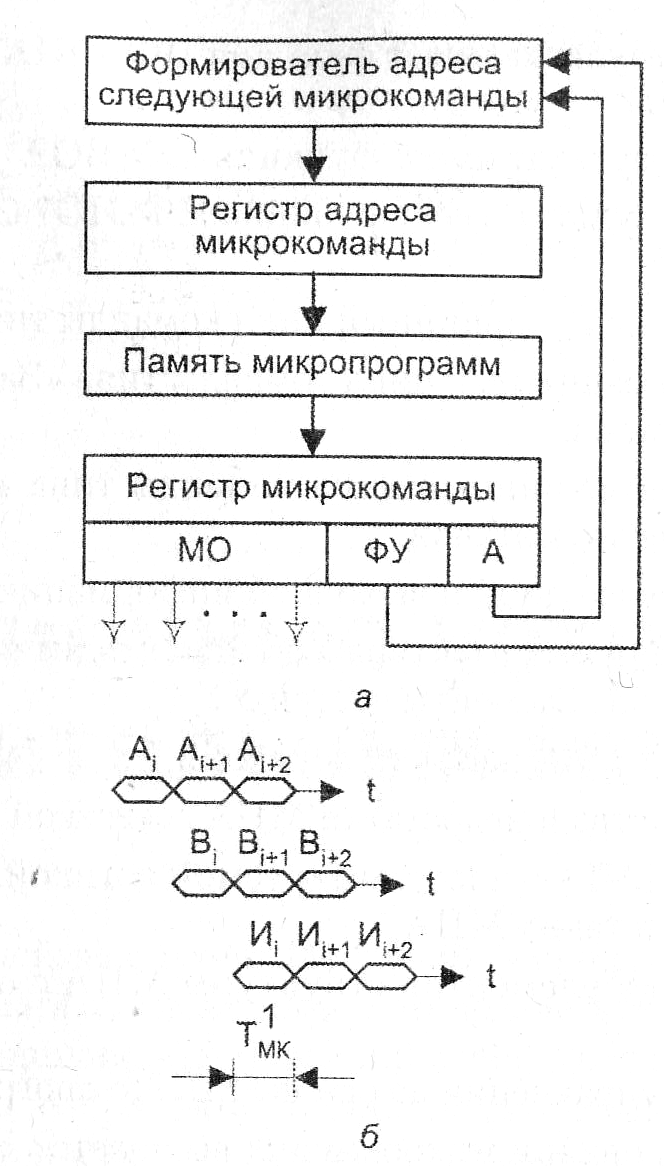

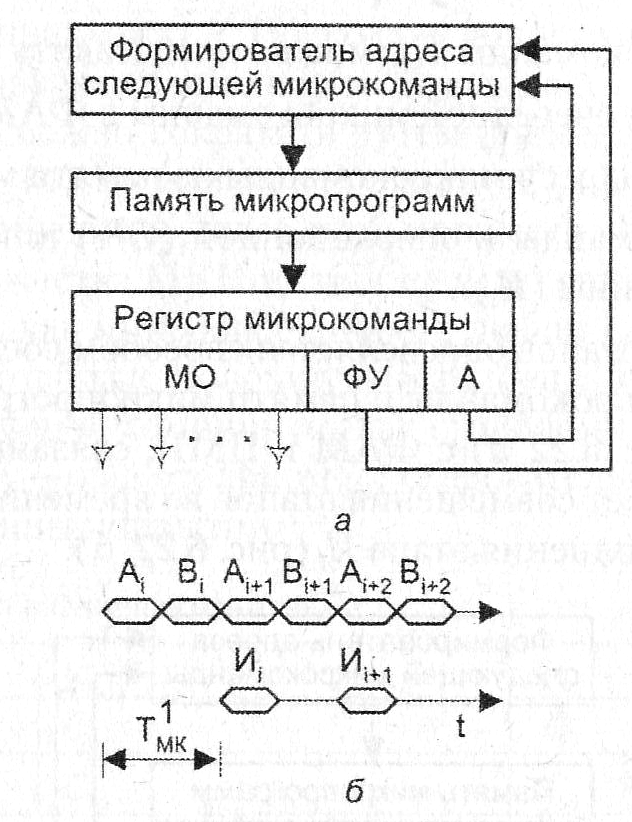

Производительность ВМ повышается при одновременной конвейерной обработке в МПА нескольких микрокоманд, находящихся на различных этапах выполнения. Для совмещения во времени этапов Ajt Вi и Иi в МПА вводятся дополнительные запоминающие элементы, которые хранят результаты обработки на каждом этапе.

В МПА с одним уровнем совмещения используется один запоминающий элемент — конвейерный регистр микрокоманды, подключенный к выходу памяти микропрограмм (рис. 6.23, а). В данной структуре реализуется одновременна обработка двух микрокоманд: в то время как исполняется находящаяся в PМК i-я микрокоманда (этап Иi), в ФАМ вычисляется адрес (i + 1)-й микрокоманды (этап Аi+1)> и затем по этому адресу из ПМП выбирается (i + 1)-я микрокоманда (этап В

i+1). Следовательно, в МПА с одним уровнем совмещения обеспечивается параллельное выполнение этапов Ai+l и Bi+1 и этапа Иi (рис. 6 23 б):

Тмк = max{(t., + tB), tu}.

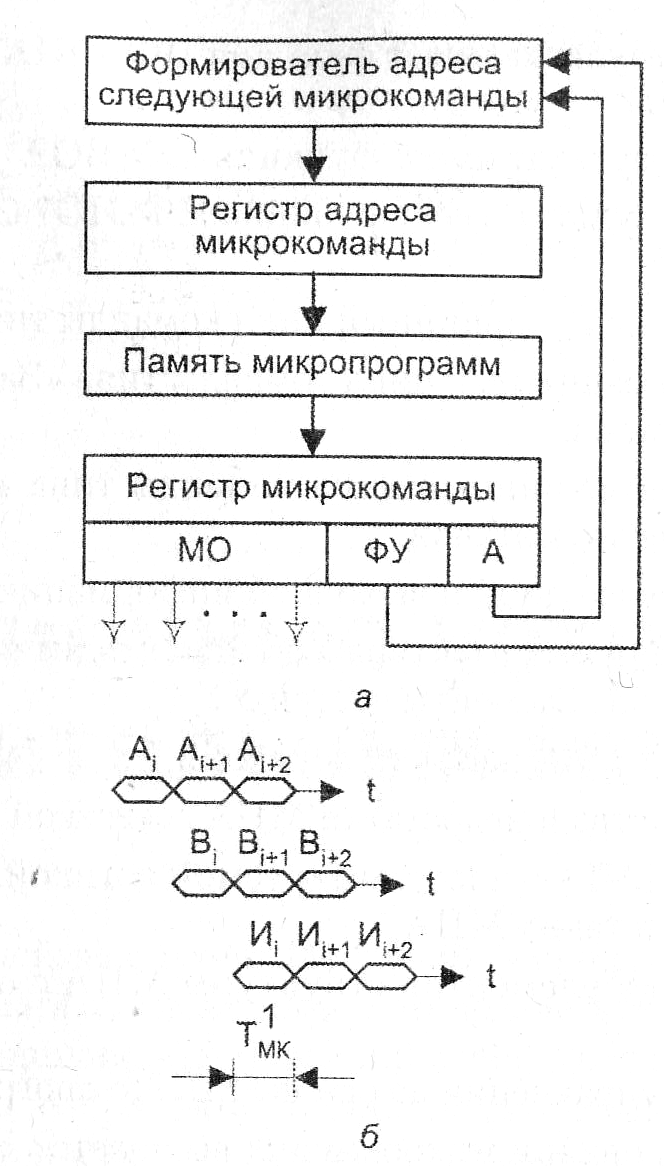

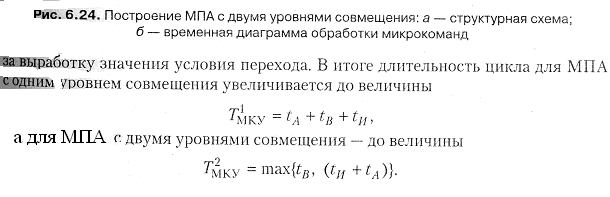

Очевидно, что при tn < tA + tB в данной структуре наблюдается вынужденный простой операционной (или адресной) части ВМ. Этот недостаток устраняется в МПА с двумя уровнями совмещения (рис. 6.24, а), в котором ФАМ и ПМП связаны друг с другом двумя конвейерными регистрами — РМК и РАМ. Здесь одновременно обрабатываются три микрокоманды: в операционной или адресной части исполняется МК, (этап Я,), выбирается из памяти MKi+l (этап Bi+i), а в Ф вычисляется адрес MKi+2 (этап Аi+2). Как видно из рис. 6.24, б, в такой структуре совмещается во времени выполнение всех трех этапов и

Методы конвейерной обработки обеспечивают значительный выигрыш только при выполнении линейных участков микропрограммы. Если реализуемая в функция управления является условной, а значение условия вырабатывается на текущем этапе в операционной (адресной) части, то правильный адрес следующей микрокоманды может быть вычислен только по окончании этапа Иi, ответственного

48.Преимущества и недостатки микропрограммного управления.

К явно выраженным достоинствам микропрограммного управления можно отнести следующее.

1. Гибкость, приспосабливаемость, простота модернизации, заключающиеся в возможности получения на том же самом оборудовании системы с новыми свойствами простой заменой содержимого микропрограммной памяти.

Другой областью применения является эмуляция, представляющая собой такое расширение архитектуры одной системы, в результате которого она воспроизводит архитектуру другой системы.

2. Простота проектирования, тестирования и эксплуатации.

3. Регулярность структуры (по разрядам). Этот фактор является очень важным с точки зрения совместимости с технологией производства БИС и СБИС.

Основным недостатком микропрограммного управления является меньшее быстродействие.

49. Принцип локальности по обращению (три вида).

Локальность по обращению позволяет эффективно реализовывать многоуровневую систему памяти. Принцип локальности в численной форме представляют в виде правила «90/10»: 90% времени работы программы связано с доступом к 10% адресного пространства этой программы.

Существуют три вида локальности:

- пространственная локальность программы: с очень высокой вероятностью адрес очередной команды программы: = следует непосредственно за адресом, по которому была считана текущая команда; = расположен вблизи него.

- пространственная локальность данных: обрабатываемые данные, как правило, структурированы, и такие структуры обычно хранятся в последовательных ячейках памяти.

- временная локальность данных: программы содержат множество небольших циклов и подпрограмм. Небольшие наборы команд могут многократно повторяться в течение некоторого интервала времени.

Программу представляют в виде последовательно обрабатываемых фрагментов – компактных групп команд и данных (кластеров).

Помещая такие фрагменты в более быструю память, можно существенно снизить общие задержки на обращение:

- команды и данные, будучи один раз переданы из медленного ЗУ в быстрое, затем могут использоваться многократно;

- среднее время доступа к ним в этом случае определяется уже более быстрым ЗУ.

К архитектуре иерархической системе: локальность по обращению позволяет хранить программы и данные в дешевых емких ЗУ, а в процессе обработки активно использовать дорогую, быструю память малой емкости.

50 Блочная организация оперативной памяти.

Емкость основной памяти современных ВМ слишком велика, чтобы ее можно было реализовать на базе единственной интегральной микросхемы (ИМС).

Необходимость объединения нескольких ИМС ЗУ возникает также, когда разрядность ячеек в микросхеме ЗУ меньше разрядности слов ВМ.

Увеличение разрядности ЗУ реализуется за счет объединения адресных входов объединяемых ИМС ЗУ.

Информационные входы и выходы микросхем являются входами и выходами модуля ЗУ увеличенной разрядности (рис. 5.2).

Полученную совокупность микросхем называют модулем памяти. Модулем можно считать и единственную микросхему, если она уже имеет нужную разрядность.

Один или несколько модулей образуют банк памяти.

Рис. 5.2. Увеличение разрядности памяти

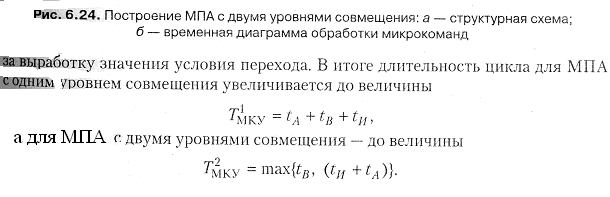

Для получения требуемой емкости ЗУ нужно определенным образом объединить несколько банков памяти меньшей емкости.

В общем случае основная память ВМ практически всегда имеет блочную структуру, то есть содержит несколько банков.

При использовании блочной памяти, состоящей из В банков, адрес ячейки А преобразуется в пару (b, w), где b — номер банка, w — адрес ячейки внутри банка.

Известны три схемы распределения разрядов адреса А между b и w:

- блочная (номер банка b определяет старшие разряды адреса);

Адресное пространство памяти разбито на группы последовательных адресов, и каждая такая группа обеспечивается отдельным банком памяти.

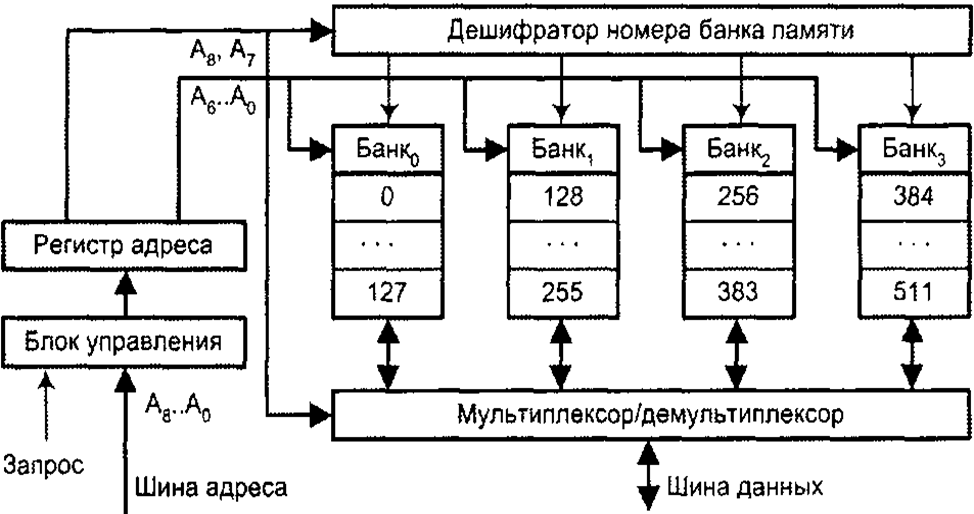

Для обращения к ОП используется 9-разрядный адрес, семь младших разрядов которого (А0-А6) поступают параллельно на все банки памяти и выбирают в каждом из них одну ячейку.

Два старших разряда адреса (A7,A8 ) содержат номер банка.

Выбор банка обеспечивается либо с помощью дешифратора номера банка памяти, либо путем мультиплексирования информации (на рис. 5.3 показаны оба варианта).

В функциональном отношении такая ОП может рассматриваться как единое ЗУ, емкость которого равна суммарной емкости составляющих, а быстродействие — быстродействию отдельного банка.

- циклическая (b = А mod В; w = A div В);

- блочно-циклическая (комбинация двух предыдущих схем).

Рассмотрение основных структур блочной ОП проведем на примере памяти емкостью 512 слов (2^9), построенной из четырех банков по 128 слов в каждом. Типовая структура памяти, организованная в соответствии с блочной структурой, показана на рис. 5.3.

Адресное пространство памяти разбито на группы последовательных адресов, и каждая такая группа обеспечивается отдельным банком памяти.

Для обращения к ОП используется 9-разрядный адрес, семь младших разрядов которого (А0-А6) поступают параллельно на все банки памяти и выбирают в каждом из них одну ячейку.

Два старших разряда адреса (A7,A8 ) содержат номер банка.

Выбор банка обеспечивается либо с помощью дешифратора номера банка памяти, либо путем мультиплексирования информации (на рис. 5.3 показаны оба варианта).

В общем случае средства адресации микрокоманд должны обеспечивать формирование:

1. произвольного значения адреса;

2. за минимальное время;

3. при сравнительно небольших затратах оборудования.

Ни естественная, ни принудительная адресации не удовлетворяют перечисленным требованиям.

Естественная адресация удовлетворяет пунктам 2 и 3, но не позволяет простыми средствами обеспечить выполнение п.1, что является существенным при реализации переходов.

Принудительная адресация требует значительно больших затрат микропрограммной памяти для хранения адресов.

45.Многонаправленные переходы. Способы их реализации.

В микропрограммировании значительно чаще, чем в обычном программировании встречаются многонаправленные переходы, когда направление перехода зависит от нескольких признаков.

На рисунке 7 показаны два способа реализации многонаправленного перехода – последовательный и параллельный.

В такой ситуации при параллельной реализации проблема формирования произвольного адреса становится достаточно сложной.

Задание нескольких адресов в адресном поле неприемлемо, поскольку микропрограммная память будет использоваться крайне неэффективно. (Выполнение много-направленных переходов за один такт требует наличия у секвенсора нескольких входов тестирования признаков)

Один из наиболее удачных методов формирования адресов нескольких направлений заключается в использовании дополнительной памяти, как это показано на рис.8.

В адресном поле микрокоманды задаётся не адрес следующей микрокоманды, а указывается начало области адресов переходов в этой памяти для данного случая.

Совокупность значений признаков является смещением, тем самым, указывая на конкретную ячейку, в которой хранится адрес требуемой микрокоманды.

Поле управления логическими условиями определяет правило формирования и количество анализируемых признаков.

Следует отметить, что время, затрачиваемое на формирование адреса, по сравнению с тем, как если бы адреса указывались в микрокоманде, будет больше.

46.Виды микропрограммного управления.

Применяемые в микрокомандах варианты кодирования сигналов управления можно свести к трем типам: горизонтальное, вертикальное и смешанное микропрограммирование.

При горизонтальном микропрограммировании каждому функциональному сигналу в поле код микрооперации ставится в соответствие один разряд.

Это позволяет в рамках одной микрокоманды формировать любые сочетания функциональных сигналов, чем обеспечивается максимальный параллелизм (максимальная производительность) выполнения микроопераций.

При вертикальном кодировании каждой микрооперации присваивается определенный код.

Этот код и заносится в поле код микрооперации, которое имеет минимальную длину. Такой способ кодирования требует минимальных аппаратных зат-рат ПМ, однако возникает необходимость в дешифраторе, преобразующем код микрооперации в соответствующий сигнал управления.

В зависимости от принципа разбиения микроопераций на группы различают два вида смешанного микропрограммирования:

Горизонтально-вертикальное (более распространено) и вертикально-горизонтальное.

В горизонтально-вертикальном методе в каждую группу включаются взаимно несовместимые микрооперации, то есть такие, которые никогда не встречаются вместе в одной микрокоманде. При этом сигналы, обычно формируемые в одном и том же такте, оказываются в разных группах. Внутри каждой группы сигналы управления кодируются вертикальным способом, а группы – горизонтальным способом.

47.Способы повышения быстродействия микропрограммных устройств управления.

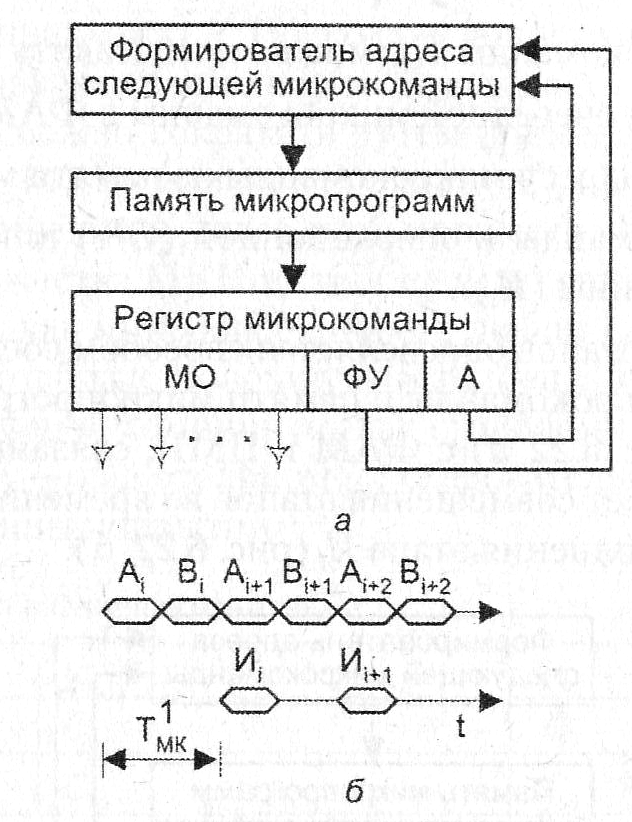

Производительность ВМ повышается при одновременной конвейерной обработке в МПА нескольких микрокоманд, находящихся на различных этапах выполнения. Для совмещения во времени этапов Ajt Вi и Иi в МПА вводятся дополнительные запоминающие элементы, которые хранят результаты обработки на каждом этапе.

В МПА с одним уровнем совмещения используется один запоминающий элемент — конвейерный регистр микрокоманды, подключенный к выходу памяти микропрограмм (рис. 6.23, а). В данной структуре реализуется одновременна обработка двух микрокоманд: в то время как исполняется находящаяся в PМК i-я микрокоманда (этап Иi), в ФАМ вычисляется адрес (i + 1)-й микрокоманды (этап Аi+1)> и затем по этому адресу из ПМП выбирается (i + 1)-я микрокоманда (этап В

i+1). Следовательно, в МПА с одним уровнем совмещения обеспечивается параллельное выполнение этапов Ai+l и Bi+1 и этапа Иi (рис. 6 23 б):

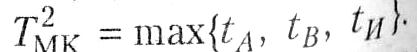

Тмк = max{(t., + tB), tu}.

Очевидно, что при tn < tA + tB в данной структуре наблюдается вынужденный простой операционной (или адресной) части ВМ. Этот недостаток устраняется в МПА с двумя уровнями совмещения (рис. 6.24, а), в котором ФАМ и ПМП связаны друг с другом двумя конвейерными регистрами — РМК и РАМ. Здесь одновременно обрабатываются три микрокоманды: в операционной или адресной части исполняется МК, (этап Я,), выбирается из памяти MKi+l (этап Bi+i), а в Ф вычисляется адрес MKi+2 (этап Аi+2). Как видно из рис. 6.24, б, в такой структуре совмещается во времени выполнение всех трех этапов и

Методы конвейерной обработки обеспечивают значительный выигрыш только при выполнении линейных участков микропрограммы. Если реализуемая в функция управления является условной, а значение условия вырабатывается на текущем этапе в операционной (адресной) части, то правильный адрес следующей микрокоманды может быть вычислен только по окончании этапа Иi, ответственного

48.Преимущества и недостатки микропрограммного управления.

К явно выраженным достоинствам микропрограммного управления можно отнести следующее.

1. Гибкость, приспосабливаемость, простота модернизации, заключающиеся в возможности получения на том же самом оборудовании системы с новыми свойствами простой заменой содержимого микропрограммной памяти.

Другой областью применения является эмуляция, представляющая собой такое расширение архитектуры одной системы, в результате которого она воспроизводит архитектуру другой системы.

2. Простота проектирования, тестирования и эксплуатации.

3. Регулярность структуры (по разрядам). Этот фактор является очень важным с точки зрения совместимости с технологией производства БИС и СБИС.

Основным недостатком микропрограммного управления является меньшее быстродействие.

49. Принцип локальности по обращению (три вида).

Локальность по обращению позволяет эффективно реализовывать многоуровневую систему памяти. Принцип локальности в численной форме представляют в виде правила «90/10»: 90% времени работы программы связано с доступом к 10% адресного пространства этой программы.

Существуют три вида локальности:

- пространственная локальность программы: с очень высокой вероятностью адрес очередной команды программы: = следует непосредственно за адресом, по которому была считана текущая команда; = расположен вблизи него.

- пространственная локальность данных: обрабатываемые данные, как правило, структурированы, и такие структуры обычно хранятся в последовательных ячейках памяти.

- временная локальность данных: программы содержат множество небольших циклов и подпрограмм. Небольшие наборы команд могут многократно повторяться в течение некоторого интервала времени.

Программу представляют в виде последовательно обрабатываемых фрагментов – компактных групп команд и данных (кластеров).

Помещая такие фрагменты в более быструю память, можно существенно снизить общие задержки на обращение:

- команды и данные, будучи один раз переданы из медленного ЗУ в быстрое, затем могут использоваться многократно;

- среднее время доступа к ним в этом случае определяется уже более быстрым ЗУ.

К архитектуре иерархической системе: локальность по обращению позволяет хранить программы и данные в дешевых емких ЗУ, а в процессе обработки активно использовать дорогую, быструю память малой емкости.

50 Блочная организация оперативной памяти.

Емкость основной памяти современных ВМ слишком велика, чтобы ее можно было реализовать на базе единственной интегральной микросхемы (ИМС).

Необходимость объединения нескольких ИМС ЗУ возникает также, когда разрядность ячеек в микросхеме ЗУ меньше разрядности слов ВМ.

Увеличение разрядности ЗУ реализуется за счет объединения адресных входов объединяемых ИМС ЗУ.

Информационные входы и выходы микросхем являются входами и выходами модуля ЗУ увеличенной разрядности (рис. 5.2).

Полученную совокупность микросхем называют модулем памяти. Модулем можно считать и единственную микросхему, если она уже имеет нужную разрядность.

Один или несколько модулей образуют банк памяти.

Рис. 5.2. Увеличение разрядности памяти

Для получения требуемой емкости ЗУ нужно определенным образом объединить несколько банков памяти меньшей емкости.

В общем случае основная память ВМ практически всегда имеет блочную структуру, то есть содержит несколько банков.

При использовании блочной памяти, состоящей из В банков, адрес ячейки А преобразуется в пару (b, w), где b — номер банка, w — адрес ячейки внутри банка.

Известны три схемы распределения разрядов адреса А между b и w:

- блочная (номер банка b определяет старшие разряды адреса);

Адресное пространство памяти разбито на группы последовательных адресов, и каждая такая группа обеспечивается отдельным банком памяти.

Для обращения к ОП используется 9-разрядный адрес, семь младших разрядов которого (А0-А6) поступают параллельно на все банки памяти и выбирают в каждом из них одну ячейку.

Два старших разряда адреса (A7,A8 ) содержат номер банка.

Выбор банка обеспечивается либо с помощью дешифратора номера банка памяти, либо путем мультиплексирования информации (на рис. 5.3 показаны оба варианта).

В функциональном отношении такая ОП может рассматриваться как единое ЗУ, емкость которого равна суммарной емкости составляющих, а быстродействие — быстродействию отдельного банка.

- циклическая (b = А mod В; w = A div В);

- блочно-циклическая (комбинация двух предыдущих схем).

Рассмотрение основных структур блочной ОП проведем на примере памяти емкостью 512 слов (2^9), построенной из четырех банков по 128 слов в каждом. Типовая структура памяти, организованная в соответствии с блочной структурой, показана на рис. 5.3.

Адресное пространство памяти разбито на группы последовательных адресов, и каждая такая группа обеспечивается отдельным банком памяти.

Для обращения к ОП используется 9-разрядный адрес, семь младших разрядов которого (А0-А6) поступают параллельно на все банки памяти и выбирают в каждом из них одну ячейку.

Два старших разряда адреса (A7,A8 ) содержат номер банка.

Выбор банка обеспечивается либо с помощью дешифратора номера банка памяти, либо путем мультиплексирования информации (на рис. 5.3 показаны оба варианта).