Файл: Перечень ответов на вопросы к промежуточному зачету по дисциплине Организация эвм и вс.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 07.11.2023

Просмотров: 257

Скачиваний: 4

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Многомодальная логика (в вопросе 34 есть че-то)

36.Общее понятие о ядре процессора. Многоядерные процессоры

Ядро – это самостоятельный вычислительный блок в архитектуре процессора, способный выполнять линейную последовательность задач за определенный период времени. Если нагрузить одно ядро несколькими последовательностями задач, то оно будет попеременно переключаться между ними, обрабатывая по одной задаче из каждого потока (образно говоря, ядро - мозг процессора).

Ядро процессора выполняет все арифметические и логические операции, а также содержит все необходимые функциональные блоки.

Одним из этапов совершенствования архитектуры фон Неймана является распараллеливание потоков (Thread Level Parallelism, TLP). Различают одновременную многопоточность (Simultaneous Multithreading, SMT) и многопоточность на уровне кристалла (Chip-level Multithreading, CMT). Эти два подхода в основном различаются представлением о том, что такое поток. Типичным представителем SMT является так называемая технология HTT (Hyper-Threading Technology).

Многоядерные процессоры могут выполнять параллельно несколько однотипных (или разноплановых) задач, увеличивая скорость их обработки и, соответственно, скорость их выполнения.

Преимущества многоядерных процессоров:

37. Основные функции Устройства управления. Понятия ЦИКЛ и ТАКТ

В самом упрощенном виде процессор можно представить состоящим из операционного (обрабатывающего) устройства и устройства управления (УУ).

Исходя из такого представления, основными функциями УУ являются:

1) выборка очередной команды из ОП;

2) хранение команды во время её исполнения;

3) преобразование (вместе с другими устройствами ЦП) адресного поля команда;

4) дешифрация кода операции и формирование необходимой последовательности управляющих сигналов;

5) формирование адреса следующей команды;

6) ряд вспомогательных действий.

ИЛИ

Основные функции УУ:

1. Формирование адреса инструкции.

2. Считывание инструкции из ОЗУ (ПЗУ) и ее хранение во время выполнения.

3. Дешифрация кода операции.

4. Формирование управляющих сигналов.

5. Считывание из регистра команд и регистров микропроцессорной памяти отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирование полных адресов операндов.

6. Выборка операндов (по сформированным адресам) и выполнение заданной операции обработки этих операндов.

7. Запись результатов операции в память.

8. Формирования адреса следующей команды программы.

Чтобы характеризовать временные соотношения в устройстве управления, воспользуемся понятиями цикл и такт.

Цикл – это время выполнения операции

Такт – время выполнения одной (или нескольких, выполняемых одновременно) микрооперации.

Под микрооперацией обычно понимается элементарное действие, выполняемое в процессоре, и которое нельзя разбить на более мелкие этапы.

Типичными примерами микроопераций могут служить сдвиг содержимого регистра на один разряд, суммирование, приём числа в регистр

С точки зрения длительности цикла и такта различают: синхронное, синхронно – асинхронное и асинхронное управление. В первом случае длительность цикла (для одной и той же операции) и длительность такта постоянны. Во втором случае длительность цикла переменна, а длительность такта постоянно.

Переменность длительности цикла достигается исключением некоторых тактов. Примером может служить операция умножения, реализуемая с пропуском тактов суммирования по нулевым значениям анализируемого разряда множителя.

В третьем случае переменны длительности и цикла, и такта. Это наиболее сложный, но и самый быстродействующий вариант.

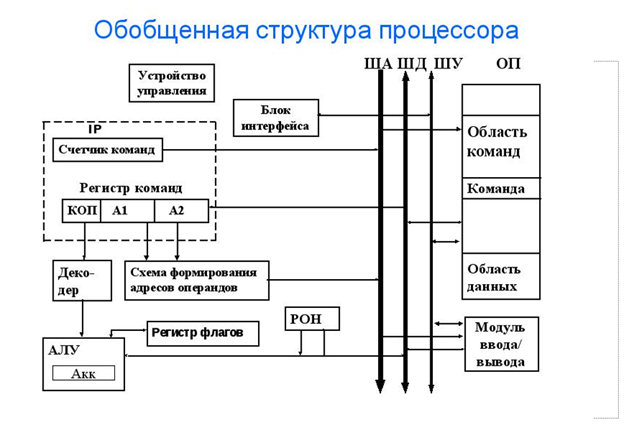

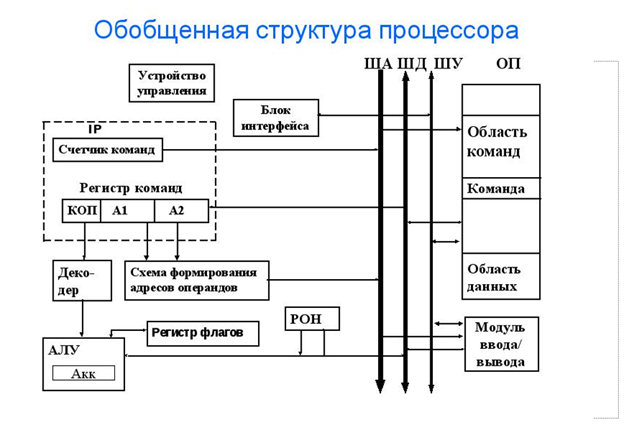

38.Обобщенная структура ПРОЦЕССОРА. Ее основные узлы и их назначение.

В состав любого процессора входят указатель команд (IP), регистр команд (РК), регистр адреса (РгАП), арифметико-логическое устройство (АЛУ), набор регистров общего назначения (РОН).

В состав любого процессора входят указатель команд (IP), регистр команд (РК), регистр адреса (РгАП), арифметико-логическое устройство (АЛУ), набор регистров общего назначения (РОН).

Регистр команд предназначен для хранения кода команды на период времени, который необходим для ее выполнения.

Указатель команды хранит адрес команды.

Регистр адреса хранит в себе исполнительные адреса операндов.

АЛУ служит для выполнения арифметических и логических преобразований над операндами.

Регистры общего назначения предназначены для хранения операндов арифметико-логических инструкций, а также адресов или отдельных компонентов адресов ячеек памяти.

39.Схемно-логическое устройство управления. Достоинства и недостатки

(че-то есть в 37 вопросе, вроде)

Схемно-логическое УУ - устройство управления, построенное на микропрограммном автомате с жесткой логикой. Такие УУ можно рассматривать как конечный автомат, реализованный аппаратно.

Достоинство: при реализации простой системы команд услы МПА с жесткой логикой экономичны и позволяют обеспечить наибольшее быстродействие из всех возможных методов построения МПА.

Недостатки:

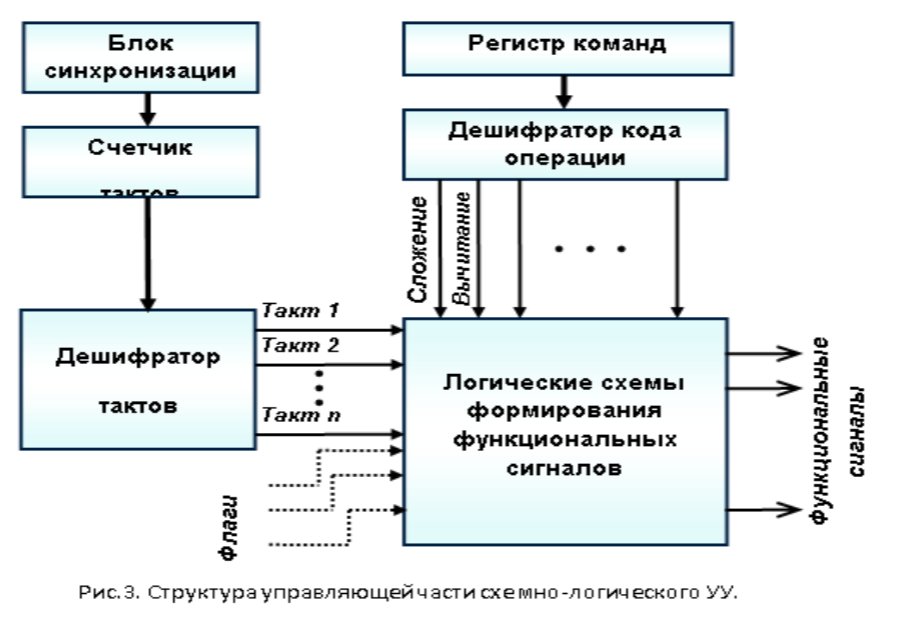

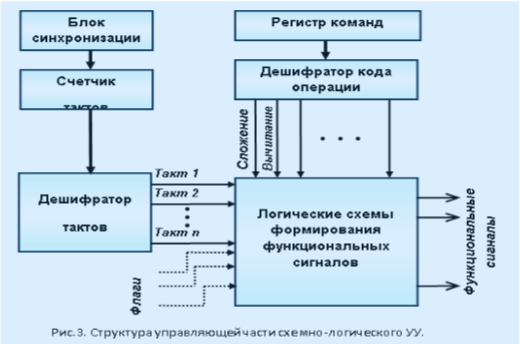

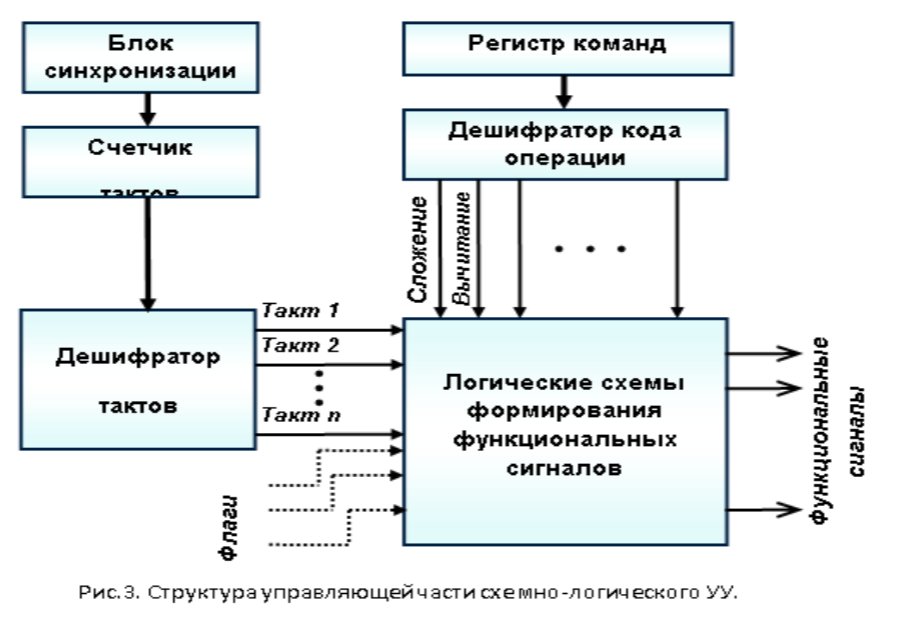

40.Структура управляющей части схемно-логического устройства управления. Ее основные узлы и их назначение.

Обычно тип микропрограммного автомата, формирующего сигналы управления,определяет название всего устройства управления. Так, схемно-логическое УУ имеет в своем составе МПА с жесткой (аппаратной) логикой. Такие устройства управления можно рассматривать как конечный автомат, реализованный аппаратно. Последовательность формирования функциональных сигналов задается схемой соединения элементов устройства.

Под функциональным сигналом будем понимать сигнал, инициирующий выполнение какого-то действия, без учета временных и электрических параметров этого сигнала.

При реализации простой системы команд узлы МПА с жесткой логикой экономичны и позволяют обеспечить наибольшее быстродействие из всех возможных методов построения МПА.

Однако с возрастанием сложности системы команд соответственно усложняются и схемы автоматов с жесткой логикой, в результате чего уменьшается их быстродействие.

Второй недостаток МПА с жесткой логикой - слабая регулярность структуры, а, следовательно, и большие трудности при размещении УУ такого типа на кристалле интегральной микросхемы.

Ещё одним недостатком, существенно ограничивающим распространение УУ с «жесткой логикой», являются очень большие трудности, возникающие при проектировании таких устройств, а также большие проблемы, связанные с внесением изменений или добавлений в систему команд ЭВМ.

41.Принцип микропрограммного управления. Понятие микрокоманды и микропрограммы.

Одним из мощных инструментов разработки цифровых устройств является микропрограммирование.

Принцип микропрограммного управления, предложенный М. Уилксом в 1951 году, широко применяется при построении устройств управления, эмуляторов, интерпретаторов систем команд и языков высокого уровня.

В основе идеи лежит тот факт, что для инициирования любой микрооперации достаточно сформировать соответствующий управляющий сигнал на соответствующей линии управления, то есть перевести такую линию в активное состояние.

Это может быть представлено с помощью двоичных цифр 1 (активное состояние - есть управляющий сигнал) и 0 (пассивное состояние - нет сигнала)

Для указания микроопераций, выполняемых в данном такте, можно сформировать управляющее слово, которое будет задавать формирование управляющих сигналов на соответствующих линиях.

Такое управляющее слово называют микрокомандой.

Таким образом, микрокоманда может быть представлена управляющим словом со своей комбинацией нулей и единиц.

Упорядоченная последовательность микрокоманд образует микропрограмму.

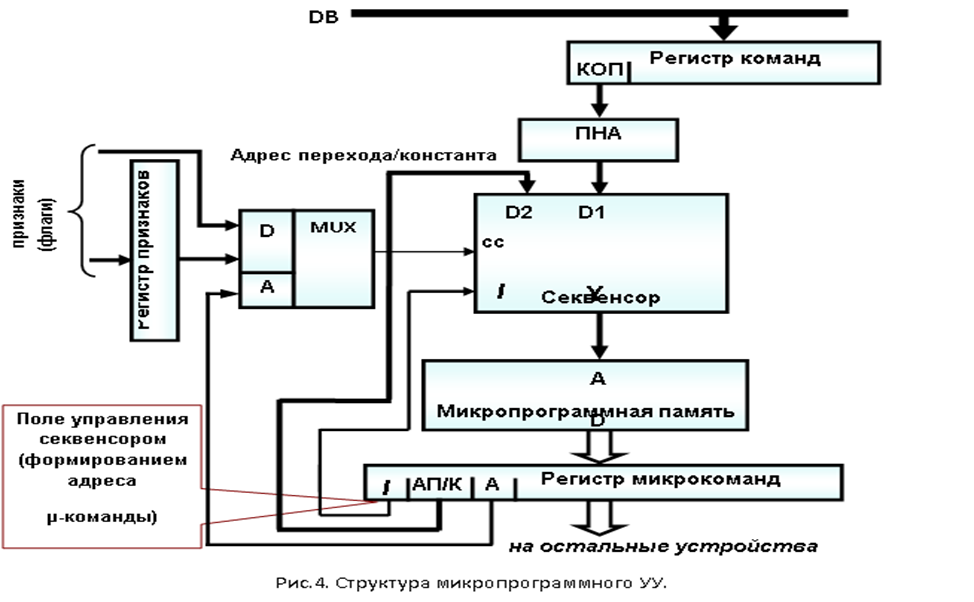

42. Структура микропрограммного устройства управления, ее основные блоки их назначение.

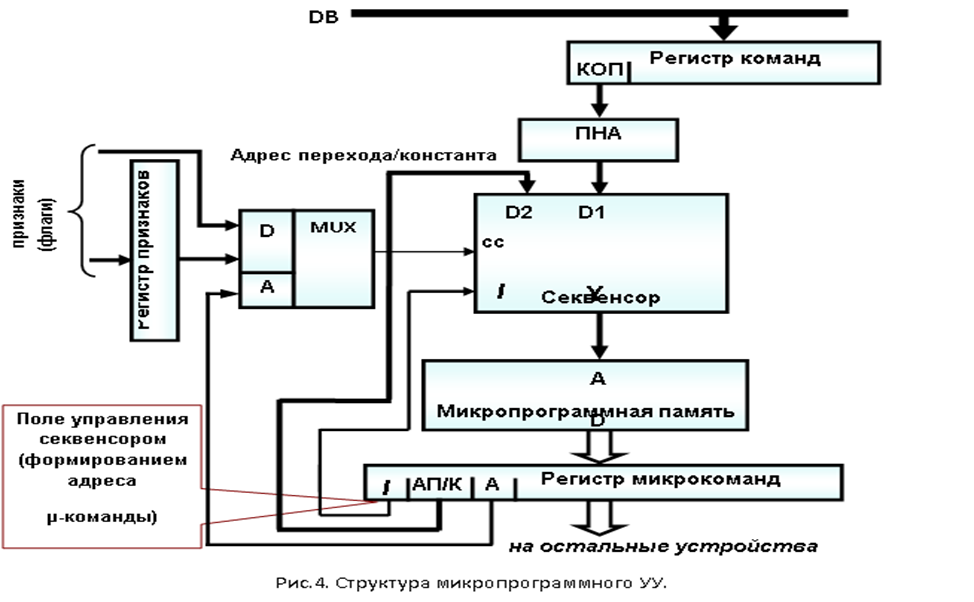

В простейшем случае микропрограммное устройство управления состоит из памяти микропрограмм ПМ и схемы формирования адресов микрокоманд. Наиболее распространенная структура микропрограммного устройства управления (МПУ) приведена выше.

Регистр команд служит для хранения исполняемой команды.

Преобразователь начального адреса ПНА из кода операции формирует начальный адрес соответствующей этой команде микропрограммы.

Секвенсор вместе с мультиплексором признаков формирует адреса ПМ.

Значение адреса зависит от типа инструкции на входах I и признака, подключаемого к входу код условия cc (condition code).

В реальных условиях секвенсор – достаточно сложное устройство, в состав которого входят регистры, мультиплексоры, сумматоры, стек на 10 – 20 адресов. Количество инструкций может достигать десятков.

В регистре микрокоманд хранится исполняемая в текущем такте микрокоманда.

43. Типы микропрограмм. Последовательность действий выполнения микропрограммы.

В регистре микрокоманд хранится исполняемая в текущем такте микрокоманда. Хранящиеся в МПП микропрограммы условно можно разделить на два типа:

1. Микропрограммы, управляющие исполнением команд. Очевидно, что количество таких микропрограмм равно количеству команд, составляющих систему команд ЭВМ.

2. Микропрограммы (назовём их микропроцедуры), управляющие выполнением специальных процедур, необходимых для функционирования ЭВМ. Примерами их могут служить процедуры «Чтение команды», «Реакция на прерывание», «Приостановка процессора» и т.п.

Исходя из такого представления, запуск и выполнение программы можно отобразить как следующую последовательность действий.

1. В указатель команд IP заносится адрес первой команды.

2. Запускается процедура «Чтение команды», в результате чего в регистр команд заносится команда.

3. В преобразователе начального адреса ПНА из кода операции формируется начальный адрес соответствующей микропрограммы.

4. Секвенсор транслирует адрес на выход.

5. Выполняется микропрограмма.

6. Последняя микрокоманда этой микропрограммы в поле управления секвенсором содержит микроинструкцию «безусловный переход», а в поле «адрес перехода АП» - адрес начала процедуры «Чтение команды».

7. Возврат на п.2.

Понимание этого процесса является важным для понимания обработки прерываний на уровне команд.

44. Адресация микрокоманд.(принудительная, естественная ).

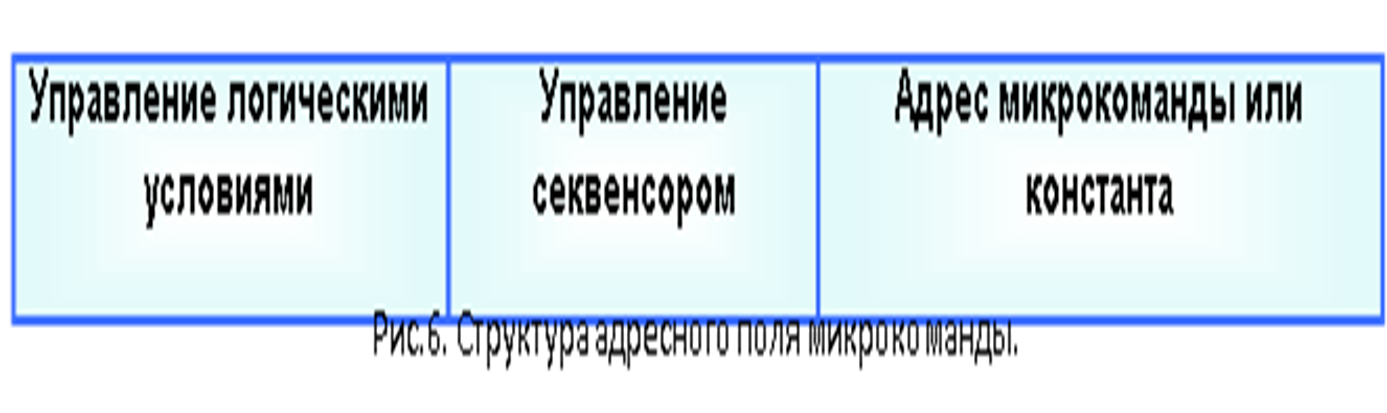

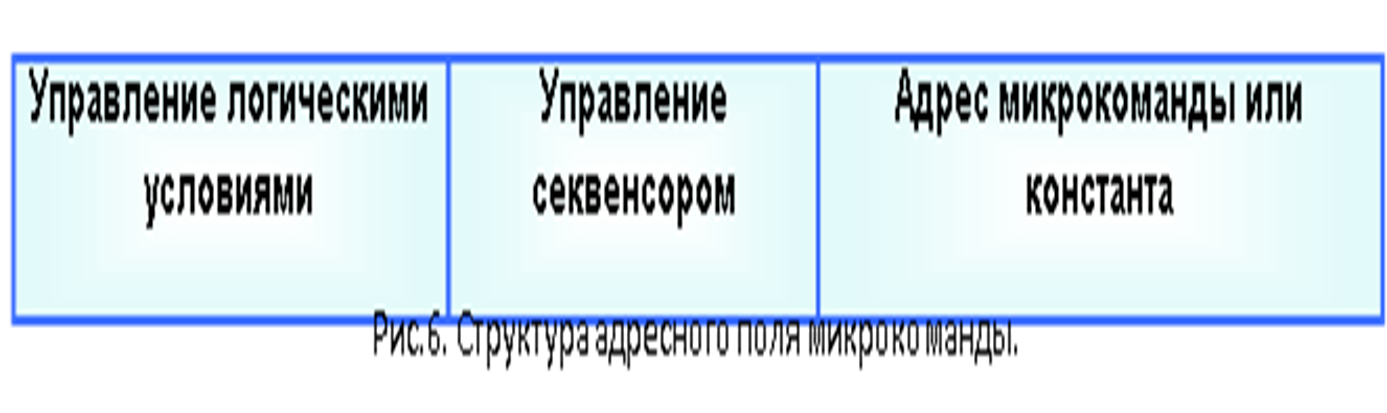

Структура адресного поля микрокоманды показана на рис.6

В битах «Управление логическими условиями» указывается правило формирования логического условия, подаваемого на вход cc (в простейшем случае – это код, подаваемый на адресные входы мультиплексора признаков); осуществляется управление запоминанием флагов в статусном регистре и т.п.

Биты «Управление секвенсором» служат для задания инструкции на входах I.

В разрядах «Адрес микрокоманды или конс-танта» указывается адрес (АП на рис.4) для инструкций перехода. Кроме этого здесь может указываться, например, количество повторений циклов в микропрограммах.

При выполнении микропрограммы адрес очередной микрокоманды относится к одной из трех категорий:

1. - определяется кодом операции команды;

2. - является следующим по порядку адресом;

3. - является адресом перехода.

Дальнейшая очередность выполнения микрокоманд микропрограммы может быть задана указанием в каждой микрокоманде адреса следующей микрокоманды (

36.Общее понятие о ядре процессора. Многоядерные процессоры

Ядро – это самостоятельный вычислительный блок в архитектуре процессора, способный выполнять линейную последовательность задач за определенный период времени. Если нагрузить одно ядро несколькими последовательностями задач, то оно будет попеременно переключаться между ними, обрабатывая по одной задаче из каждого потока (образно говоря, ядро - мозг процессора).

Ядро процессора выполняет все арифметические и логические операции, а также содержит все необходимые функциональные блоки.

Одним из этапов совершенствования архитектуры фон Неймана является распараллеливание потоков (Thread Level Parallelism, TLP). Различают одновременную многопоточность (Simultaneous Multithreading, SMT) и многопоточность на уровне кристалла (Chip-level Multithreading, CMT). Эти два подхода в основном различаются представлением о том, что такое поток. Типичным представителем SMT является так называемая технология HTT (Hyper-Threading Technology).

Многоядерные процессоры могут выполнять параллельно несколько однотипных (или разноплановых) задач, увеличивая скорость их обработки и, соответственно, скорость их выполнения.

Преимущества многоядерных процессоров:

-

Простота проектирования и производства; -

Заметно уменьшается энергопотребление.

37. Основные функции Устройства управления. Понятия ЦИКЛ и ТАКТ

В самом упрощенном виде процессор можно представить состоящим из операционного (обрабатывающего) устройства и устройства управления (УУ).

Исходя из такого представления, основными функциями УУ являются:

1) выборка очередной команды из ОП;

2) хранение команды во время её исполнения;

3) преобразование (вместе с другими устройствами ЦП) адресного поля команда;

4) дешифрация кода операции и формирование необходимой последовательности управляющих сигналов;

5) формирование адреса следующей команды;

6) ряд вспомогательных действий.

ИЛИ

Основные функции УУ:

1. Формирование адреса инструкции.

2. Считывание инструкции из ОЗУ (ПЗУ) и ее хранение во время выполнения.

3. Дешифрация кода операции.

4. Формирование управляющих сигналов.

5. Считывание из регистра команд и регистров микропроцессорной памяти отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирование полных адресов операндов.

6. Выборка операндов (по сформированным адресам) и выполнение заданной операции обработки этих операндов.

7. Запись результатов операции в память.

8. Формирования адреса следующей команды программы.

Чтобы характеризовать временные соотношения в устройстве управления, воспользуемся понятиями цикл и такт.

Цикл – это время выполнения операции

Такт – время выполнения одной (или нескольких, выполняемых одновременно) микрооперации.

Под микрооперацией обычно понимается элементарное действие, выполняемое в процессоре, и которое нельзя разбить на более мелкие этапы.

Типичными примерами микроопераций могут служить сдвиг содержимого регистра на один разряд, суммирование, приём числа в регистр

С точки зрения длительности цикла и такта различают: синхронное, синхронно – асинхронное и асинхронное управление. В первом случае длительность цикла (для одной и той же операции) и длительность такта постоянны. Во втором случае длительность цикла переменна, а длительность такта постоянно.

Переменность длительности цикла достигается исключением некоторых тактов. Примером может служить операция умножения, реализуемая с пропуском тактов суммирования по нулевым значениям анализируемого разряда множителя.

В третьем случае переменны длительности и цикла, и такта. Это наиболее сложный, но и самый быстродействующий вариант.

38.Обобщенная структура ПРОЦЕССОРА. Ее основные узлы и их назначение.

В состав любого процессора входят указатель команд (IP), регистр команд (РК), регистр адреса (РгАП), арифметико-логическое устройство (АЛУ), набор регистров общего назначения (РОН).

В состав любого процессора входят указатель команд (IP), регистр команд (РК), регистр адреса (РгАП), арифметико-логическое устройство (АЛУ), набор регистров общего назначения (РОН).Регистр команд предназначен для хранения кода команды на период времени, который необходим для ее выполнения.

Указатель команды хранит адрес команды.

Регистр адреса хранит в себе исполнительные адреса операндов.

АЛУ служит для выполнения арифметических и логических преобразований над операндами.

Регистры общего назначения предназначены для хранения операндов арифметико-логических инструкций, а также адресов или отдельных компонентов адресов ячеек памяти.

39.Схемно-логическое устройство управления. Достоинства и недостатки

(че-то есть в 37 вопросе, вроде)

Схемно-логическое УУ - устройство управления, построенное на микропрограммном автомате с жесткой логикой. Такие УУ можно рассматривать как конечный автомат, реализованный аппаратно.

Достоинство: при реализации простой системы команд услы МПА с жесткой логикой экономичны и позволяют обеспечить наибольшее быстродействие из всех возможных методов построения МПА.

Недостатки:

-

С возрастанием сложности системы команд соответственно усложняются и схемы автоматов с жесткой логикой, из-за чего уменьшается их быстродействие; -

Слабая регулярность структуры, следовательно, и большие трудности при размещении УУ такого типа на кристалле интегральной микросхемы; -

Очень большие трудности, возникающие при проектировании таких устройств, а также большие проблемы, связанные с внесением изменений или добавлений в систему команд ЭВМ.

40.Структура управляющей части схемно-логического устройства управления. Ее основные узлы и их назначение.

Обычно тип микропрограммного автомата, формирующего сигналы управления,определяет название всего устройства управления. Так, схемно-логическое УУ имеет в своем составе МПА с жесткой (аппаратной) логикой. Такие устройства управления можно рассматривать как конечный автомат, реализованный аппаратно. Последовательность формирования функциональных сигналов задается схемой соединения элементов устройства.

Под функциональным сигналом будем понимать сигнал, инициирующий выполнение какого-то действия, без учета временных и электрических параметров этого сигнала.

При реализации простой системы команд узлы МПА с жесткой логикой экономичны и позволяют обеспечить наибольшее быстродействие из всех возможных методов построения МПА.

Однако с возрастанием сложности системы команд соответственно усложняются и схемы автоматов с жесткой логикой, в результате чего уменьшается их быстродействие.

Второй недостаток МПА с жесткой логикой - слабая регулярность структуры, а, следовательно, и большие трудности при размещении УУ такого типа на кристалле интегральной микросхемы.

Ещё одним недостатком, существенно ограничивающим распространение УУ с «жесткой логикой», являются очень большие трудности, возникающие при проектировании таких устройств, а также большие проблемы, связанные с внесением изменений или добавлений в систему команд ЭВМ.

41.Принцип микропрограммного управления. Понятие микрокоманды и микропрограммы.

Одним из мощных инструментов разработки цифровых устройств является микропрограммирование.

Принцип микропрограммного управления, предложенный М. Уилксом в 1951 году, широко применяется при построении устройств управления, эмуляторов, интерпретаторов систем команд и языков высокого уровня.

В основе идеи лежит тот факт, что для инициирования любой микрооперации достаточно сформировать соответствующий управляющий сигнал на соответствующей линии управления, то есть перевести такую линию в активное состояние.

Это может быть представлено с помощью двоичных цифр 1 (активное состояние - есть управляющий сигнал) и 0 (пассивное состояние - нет сигнала)

Для указания микроопераций, выполняемых в данном такте, можно сформировать управляющее слово, которое будет задавать формирование управляющих сигналов на соответствующих линиях.

Такое управляющее слово называют микрокомандой.

Таким образом, микрокоманда может быть представлена управляющим словом со своей комбинацией нулей и единиц.

Упорядоченная последовательность микрокоманд образует микропрограмму.

42. Структура микропрограммного устройства управления, ее основные блоки их назначение.

В простейшем случае микропрограммное устройство управления состоит из памяти микропрограмм ПМ и схемы формирования адресов микрокоманд. Наиболее распространенная структура микропрограммного устройства управления (МПУ) приведена выше.

Регистр команд служит для хранения исполняемой команды.

Преобразователь начального адреса ПНА из кода операции формирует начальный адрес соответствующей этой команде микропрограммы.

Секвенсор вместе с мультиплексором признаков формирует адреса ПМ.

Значение адреса зависит от типа инструкции на входах I и признака, подключаемого к входу код условия cc (condition code).

В реальных условиях секвенсор – достаточно сложное устройство, в состав которого входят регистры, мультиплексоры, сумматоры, стек на 10 – 20 адресов. Количество инструкций может достигать десятков.

В регистре микрокоманд хранится исполняемая в текущем такте микрокоманда.

43. Типы микропрограмм. Последовательность действий выполнения микропрограммы.

В регистре микрокоманд хранится исполняемая в текущем такте микрокоманда. Хранящиеся в МПП микропрограммы условно можно разделить на два типа:

1. Микропрограммы, управляющие исполнением команд. Очевидно, что количество таких микропрограмм равно количеству команд, составляющих систему команд ЭВМ.

2. Микропрограммы (назовём их микропроцедуры), управляющие выполнением специальных процедур, необходимых для функционирования ЭВМ. Примерами их могут служить процедуры «Чтение команды», «Реакция на прерывание», «Приостановка процессора» и т.п.

Исходя из такого представления, запуск и выполнение программы можно отобразить как следующую последовательность действий.

1. В указатель команд IP заносится адрес первой команды.

2. Запускается процедура «Чтение команды», в результате чего в регистр команд заносится команда.

3. В преобразователе начального адреса ПНА из кода операции формируется начальный адрес соответствующей микропрограммы.

4. Секвенсор транслирует адрес на выход.

5. Выполняется микропрограмма.

6. Последняя микрокоманда этой микропрограммы в поле управления секвенсором содержит микроинструкцию «безусловный переход», а в поле «адрес перехода АП» - адрес начала процедуры «Чтение команды».

7. Возврат на п.2.

Понимание этого процесса является важным для понимания обработки прерываний на уровне команд.

44. Адресация микрокоманд.(принудительная, естественная ).

Структура адресного поля микрокоманды показана на рис.6

В битах «Управление логическими условиями» указывается правило формирования логического условия, подаваемого на вход cc (в простейшем случае – это код, подаваемый на адресные входы мультиплексора признаков); осуществляется управление запоминанием флагов в статусном регистре и т.п.

Биты «Управление секвенсором» служат для задания инструкции на входах I.

В разрядах «Адрес микрокоманды или конс-танта» указывается адрес (АП на рис.4) для инструкций перехода. Кроме этого здесь может указываться, например, количество повторений циклов в микропрограммах.

При выполнении микропрограммы адрес очередной микрокоманды относится к одной из трех категорий:

1. - определяется кодом операции команды;

2. - является следующим по порядку адресом;

3. - является адресом перехода.

Дальнейшая очередность выполнения микрокоманд микропрограммы может быть задана указанием в каждой микрокоманде адреса следующей микрокоманды (