Файл: Лабораторная работа Основы языка vhdl по дисциплине Проектирование цифровых устройств.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 09.11.2023

Просмотров: 37

Скачиваний: 4

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Федеральное государственное автономное

образовательное учреждение

высшего образования

«СИБИРСКИЙ ФЕДЕРАЛЬНЫЙ УНИВЕРСИТЕТ»

Институт космических и информационных технологий

Кафедра «СААУП»

Лабораторная работа № 1. Основы языка VHDL

по дисциплине «Проектирование цифровых устройств»

Преподаватель _________ О. В. Дрозд

подпись, дата инициалы, фамилия

Студент КИ20-05Б Б.У. Койчубаев

номер группы подпись, дата инициалы, фамилия

Красноярск 2023

Цель работы: изучение основ языка описания аппаратуры VHDL, получение практических навыков работы в среде Xilinx ISE WebPack.

Задачи работы:

-

ознакомление с возможностями САПР Xilinx ISE WebPack по проектированию цифровых устройств на базе программируемых логических интегральных схем (ПЛИС); -

составление алгоритмического описания заданной логической функции на языке описания аппаратуры VHDL; -

синтез и реализация заданной логической функции на базе на ПЛИС.

Ход выполнения работы

1)

2)

Таблица истинности для логического элемента 2ИЛИ-НЕ.

| Вход X1 | Вход X2 | Выход Y |

| 0 | 0 | 1 |

| 1 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 1 | 0 |

Изображение на схеме.

На зарубежный лад изображается так. Называют как NOR.

3)

Логическая функция:

4)

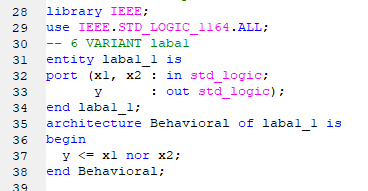

Исходный код реализуемой логической схемы:

l

ibrary IEEE;

ibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;

-- 6 VARIANT laba1

entity laba1_1 is

port (x1, x2 : in std_logic;

y : out std_logic);

end laba1_1;

architecture Behavioral of laba1_1 is

begin

y <= x1 nor x2;

end Behavioral;

5)

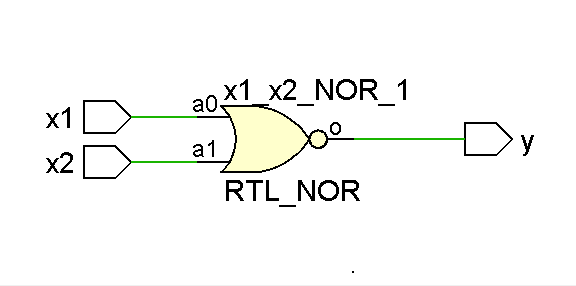

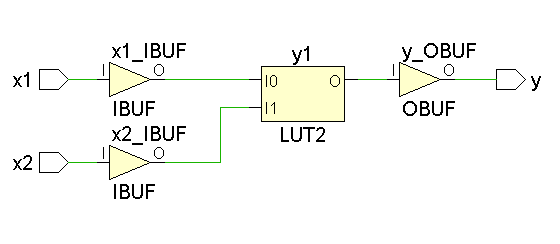

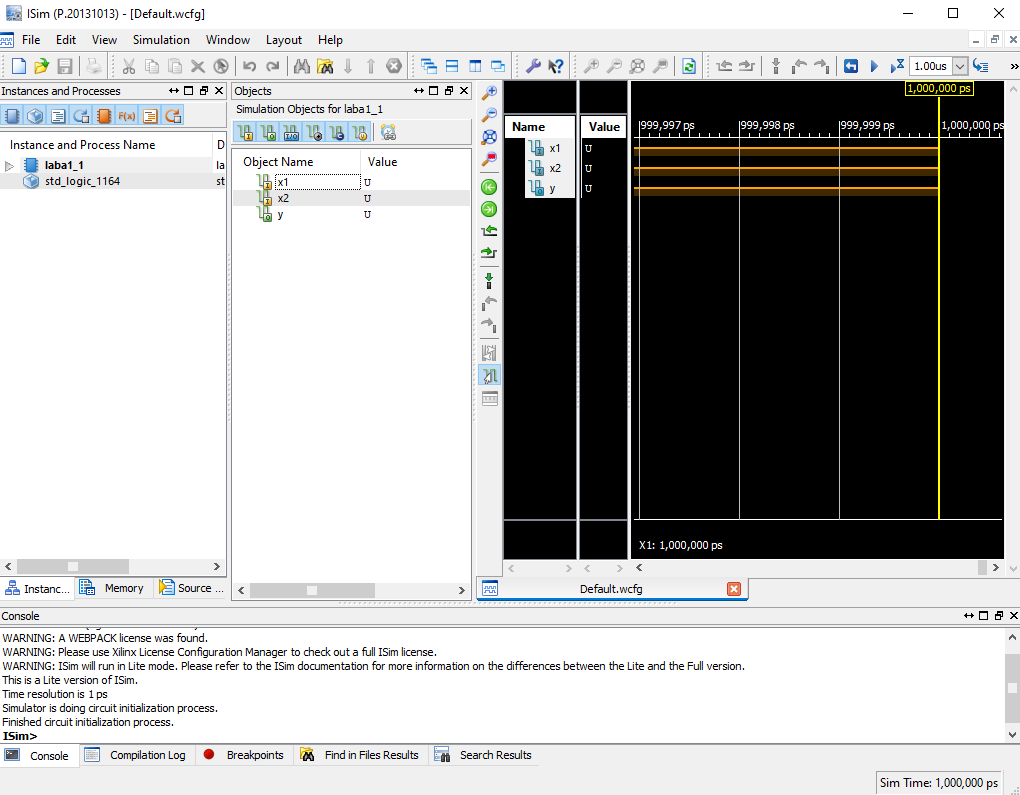

Скриншоты:

Структурная схема реализации устройства до проведения синтеза

Структурная схема реализации устройства после проведения синтеза

Временная диаграмма функционирования реализованного устройства

Выводы: изучены основы языка описания аппаратуры VHDL, получены практические навыки работы в среде Xilinx ISE WebPack.