ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 14.12.2021

Просмотров: 448

Скачиваний: 3

Записана по карті Карно МДНФ з довизначенням заборонених станів «логічними 1» дає характеристичне рівняння RS-тригера

(6.6)

На рис. 6.5, г приведені тимчасові діаграми перемикання станів тригера.

Аналогічно характеристичне рівняння у формі МКНФ для тієї ж карти Карно з довизначенням заборонених станів «логічними 0» має вигляд

(6.7)

Перетворимо тотожно рівняння (6.6), скориставшись правилом подвійного заперечення

(6.8)

Характеристичне рівняння у формі (6.8) показує спосіб реалізації RS-тригера на елементах И—НЕ (рис. 6.6, с). На рис. 6.6, б, приведене його умовне графічне зображення, а, на рис. 6.6, г — тимчасові діаграми роботи.

На

умовному графічному зображенні (рис.

6.6, б)

кружки; на входах R, S показують, що даний

RS-тригер управляється інверсними

сигналами, тобто в режимі зберігання

інформації на входи подаються

= 1 і,

= 1, управління здійснюється подачею на

відповідний вхід рівня «0», а забороненою

є комбінація вхідних сигналів

Рівняння (6.6) — (6.8) і карта Карно описують тільки статичні режими роботи RS-тригерів. Якнайповніше уявлення про їх роботу дають тимчасові діаграми (рис. 6.5, г, і 6.6, г), які описують не тільки значення вихідних

рівнів

Q і

у будь-який момент часу, але і тривалості

фронтів, затримок і послідовність

перемикання логічних елементів. З

тимчасових діаграм видно, що тривалість

перемикання tпер

і мінімальна тривалість вхідного сигналу

tвх

mіn

даних

асинхронних RS-тригерів визначаються

середнім часом затримки сигналу логічними

елементами

tпер = tвх.min = 2tзд.р.ср

Дозволяючий час асинхронного RS-тригера, визначуваний як мінімальний допустиме запізнювання сигналу на вході R щодо входу S(tразS) або сигналу на вході S щодо R(tразR)

tразS = tразR = 3tзд.р.ср

При розгляді тимчасових діаграм (рис. 6.5, г, 6.6, г) слід звернути увагу на те, що моменти перемикання вихідних рівнів визначаються строго зміною логічних станів інформаційних входів, що характерне для асинхронних RS-тригерів.

На

тимчасових діаграмах символом (*) помічені

інтервали дії на входи RS-тригерів

забороненими комбінаціями управляючих

сигналів. При цьому в тригері на елементах.

ИЛИ-НЕ встановлюються вихідні рівні Q

= 0, а в тригері на елементах И—НЕ — Q =

1,

.

Стан, що приймається RS-тригером після

закінчення дії забороненої комбінації,

залежить від того, який з керованих

сигналів

триває довше, а при строго одночасному

перемиканні сигналів на входах R і S —

від випадкового розкиду параметрів

логічних елементів.

Для усунення неоднозначності реакції RS-тpиrepa на одночасну дію сигналами установки на входи R і S необхідно обумовити стан, в який RS-тригер повинен перейти. По реакції на заборонену для RS-тригера комбінацію вхідних сигналів розрізняють S-тригери (перемикаються в одиничний стан), R-тригери (перемикаються в нульовий стан) і Е-тригери (від Exclusive, зберігають попередній стан) [14].

Функціонування R-тригера описується згідно карті Карно рівнянням

Схема, що реалізує рівняння (6.9) в базисі И—НЕ, приведена на рис. 6.7, а, а тимчасові діаграми роботи R-тригера на рис. 6.7, б.

Через

зв'язки входу логічного елементу DD1 з

виходом DD2 при одночасній управляючій

дії S = R = 1 вихід DD2, на якому встановлюється

= 0, блокує решту входів елементу DD1 і

сигналу S = 1 тригер не сприймає. Тому

комбінація S = R = 1 встановлює тригер в

стан «0». Як видно з тимчасових діаграм

(рис. 67, б),

додаткові логічні елементи на вході

збільшують час перемикання R-тригера

і мінімальну тривалість вхідного

сигналу:

tпер = tвх.min = 3tзд.р.ср

Оскільки логічні елементи DD1, DD2 обумовлюють практично однакову затримку управляючих сигналів, дозволяючий час для тригера на елементах DD3 і DD4 практично не міняється:

tдозв = 3tад.р.ср

Функціонування асинхронного S-тригера за визначенням описується картою Карно і рівнянням,

для виходу Q-тригера і відповідно для виходу,

на якому при Rn = Sn = 1 необхідно забезпечити рівень «логічного 0».

На

рис. 6.8, а

показана

схема S-тригера в базисі И—НЕ, яка

реалізовує рівняння (6.10), (6.11). Зв'язок

між виходом елементу DD1 і входом елементу

DD2 забезпечує пріоритет входу S, оскільки

при Sn

= 1 на вхід DD2 поступає рівень

=

0, який для логічного елементу И—НЕ є

домінуючим і виключає вплив інших входів

(у нашому випадку входу R). На рис. 6.8, б

показані

тимчасові діаграми перемикання S-тригера.

Стан

асинхронного Е-тригера описується

картою Карно і одержуваним з неї

характеристичним рівнянням для прямого

Q і інверсного

виходів тригера

Схема,

що реалізовує рівняння (6.12), (6.13) в базисі

логічних елементів И—НЕ, карта Карно

і тимчасові діаграми перемикання

Е-тригера показані на рис. 6.9. Додаткові

інвертування DD5, DD6 при Sn

= Rn

= 1 блокують сигналами Sn

= 0 і Rn

= 0 логічні елементи DD1, DD2, на виходах

яких

при цьому підтримуються рівні «логічної

1», що відповідає режиму зберігання

раніше записаної, інформації.

Внаслідок затримки блокуючих сигналів інвертуваннями DD5, DD6 на виходах вентилів DD1 і DD2 формуються сигнали перешкоди А і У, аналогічно перешкодам в асинхронних тригерах типа R і S, Перешкоди на управляючих входах

за певних умов можуть привести до помилкового спрацьовування даних тригерів. Для усунення помилкових спрацьовувань тригери R-, S- і Е-типу синхронізують серією імпульсів С, затриманих щодо інформаційних сигналів R і S. Для цього в схемах (рис. 6.7, 6.8, 6.9) повинен бути передбачений додатковий вхід С (показаний штриховою лінією). Таким чином, одержуємо варіанти синхронних R-, S- і Е-тригерів,

які володіють вищою надійністю, але і великим дозволяючим часом внаслідок необхідної додаткової затримки синхроімпульсів на час виникнення перешкоди.

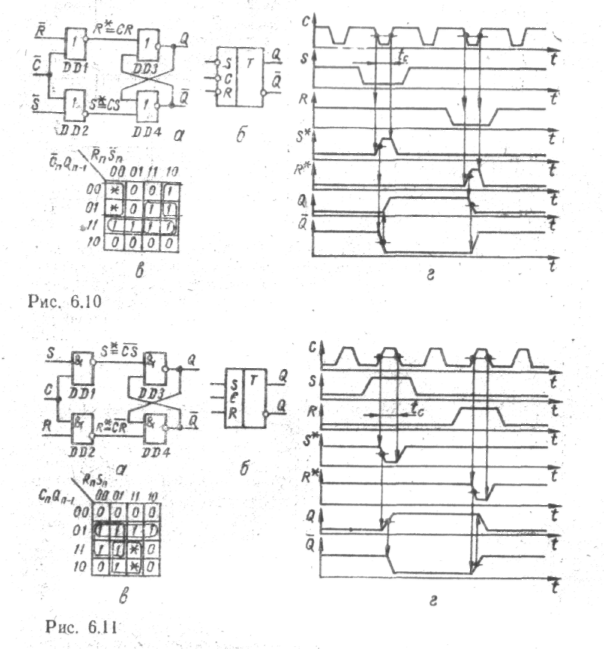

Крім

боротьби з перешкодами, режим синхронізації

RS-тригерів широко використовується

при побудові тактованих цифрових

пристроїв. Для забезпечення режиму

роботи, що синхронізується, асинхронні

RS-тригери повинні бути доповнені схемами

синхронізації. На рис. 6.10, а

і

6.11, а

показані

схеми, на рис, 6.10, б

і

6.11, б

—

умовні графічні зображення, на рис.

6.10, в

і

6.11, в

—

карти Карно і на рис. 6.10, г

і

рис. 6.11, г

—

тимчасові діаграми синхронних RS-тригерів

реалізованих відповідно в базисі

логічних елементів ИЛИ—НЕ і И—НЕ. Схеми

синхронізації побудовані на логічних

елементах DD1, DD2 і формують сигнали R* і

S*, які управляють станом асинхронних

RS-тригерів, на логічних елементах DD3,

DD4. Інформація, що поступає на входи S і

R, як видно з тимчасових діаграм,

сприймається тільки в моменти дії

синхроімпульсів С тривалістю tc.

Всякі зміни рівнів на інформаційних

входах R і S (

)

у інтервалі передаються на вхід

асинхронного тригера і викликають

несинхронізовані перемикання станів,

що характерне для схем синхронізації

рівнів. Для нормальної роботи в тактованому

режимі необхідно запобігти перемиканням

входів R, S в інтервалі синхроімпульса

тривалістю tc.

Забороненими є комбінації вхідних

сигналів Rn

= Sn

= Сn

= 1, обумовлюючі в тригері (рис. 6.10, а)

установку на прямому і інверсному

виходах рівнів Qn

= 0, а в тригері (рис. 6.11,а)

Qn

= 1, що відповідає розриву зв'язків

тригерів.

У

RS-тригерах, що синхронізуються фронтом,

інформаційні сигнали S і R можуть

перемикатися в будь-які моменти часу,

але в тригер записується стан, який

відповідає комбінації вхідних сигналів

S і R безпосередньо перед відповідним

позитивним (або негативним) фронтом

синхроімпульса. Схема синхронізації

фронтом принципово включає елемент, що

запам'ятовує, який протягом часу tc

дії синхроімпульса забезпечує управління

станом асинхронного RS-тригера. У

RS-тригерах (рис. 6.12) схеми синхронізації

тригерів, що синхронізуються фронтом,

побудовані на логічних елементах DD1,

..., DD4 типа ИЛИ—НЕ (а) або И—НЕ (в). RS-тригер

на елементах ИЛИ—НЕ синхронізується

негативним фронтом (на елементах И—НЕ

— позитивним фронтом). У паузі між

синхроімпульсами на вході синхронізації

маємо С = 1

(рис.

6.12, а)

і на виходах елементів DD3, DD4 підтримуються

рівні «логічного 0», що забезпечують

режим зберігання для асинхронного

тригера DD5. Входи S і R на стан DD3, DD4 впливу

не роблять, оскільки рівень С = 1 є

домінуючим. Хай безпосередньо перед

негативним фронтом синхроімпульса

на інформаційних входах встановилася

комбінація вхідних сигналів S = 1, R = 0.

Тоді при перемиканні входу Із

з «1» в «0» на трьох входах елементу DD3

маємо «0», на його виході встановлюється

рівень «1», який подається на входи DD1 і

DD4, блокуючи перемикання їх зовнішніми

сигналами. Тому протягом часу tc

дії рівня С = 0 тригер не реагує на

перемикання управляючих входів S і R.

Аналогічно відбувається установка

тригера в стан «0». При одночасній

установці S = 1 і R = 1 по негативному фронту

синхроімпульса відбувається змагальне

перемикання тригера на елементах DD3,

DD4 в один з двох можливих станів, яке

автоматично переписується в тригер

DD5.

Аналогічно побудований і функціонує синхронізований позитивним фронтом RS-тригер на елементах И-НЕ (ряс. 6.12, в). Полярність синхронізуючого фронту на умовному графічному позначенні (рис. 6.12, б, г) показують косою лінією на вході С.

Тривалість перемикання tпер і мінімальна тривалість вхідного сигналу tвх min для RS-тригерів, що синхронізуються рівнем і фронтом, однаково залежать від тривалості tад.р.ср становлячих елементів: tпер = tвх min = tад.р.ср.

D-тригери. До D-тригерів відносяться послідовністні бістабільні пристрої з одним інформаційним входом D і входом синхронізації С, які в моменти дії синхронізуючого рівня або фронту встановлюються в стан, визначуваний логічним рівнем сигналу на вході D, а в паузі між синхроімпульсами знаходяться в режимі зберігання інформації [24]. Принципово здійснюючі і асинхронні D-тригери, які, проте, не представляють практичного інтересу.

Функціонування синхронного D-тригера в статичних режимах описується картою Карно і характеристичним рівнянням

Реалізації

синхронних D-тригерів, що задовольняють

рівнянню (6.14), показані на рис. 6.13. Якщо

на синхронізуючий вхід D-тригера (рис.

6.13,а) поданий рівень

(або С = 0 для рис. 6.13, г)

є домінуючим для логічних елементів

DD1 і DD2, на їх виходах встановлюються

рівні S* = R* = 0 (

),

які не залежать від стану інформаційного

входу D і забезпечують режим зберігання

асинхронного тригера на логічних

елементах DD3, DD4. При

,

(С

= 1) інформаційний вхід однозначно

визначає

стан виходу елементу DD1, який, у свою

чергу, обумовлює інверсний рівень на

виході елементу DD2. Якщо при цьому D = 1

(

),

тригер встановлюється в одиничний

(нульовий)

стан, тобто в тригер записується

інформація, подана на вхід D до установки

синхронізуючого рівня С

= 1. Отже, інформація на виходах D-тригера

з'являється із затримкою щодо

інформаційного, входу D, обумовленою

затримкою синхронізуючого імпульсу С

відносно інформаційного сигналу D, а

також часом перемикання логічних

елементів DD1, ..., DD4 (рис. 6.13, в,

е).

На рис. 6.13, в,

д

приведені умовні графічні позначення

для D-тригерів на елементах відповідно

ИЛИ—НЕ

і И-НЕ.

Для забезпечення нормального функціонування D-тригерів, що синхронізуються рівнем, необхідно виключити перемикання стану інформаційного входу D на інтервалі синхронізації С. Інакше має місце так зване наскрізне управління, або не синхронізоване управління станом тригера безпосередньо інформаційним входом. Управління, що не синхронізується, виключається у разі синхронізації D-тригера фронтом синхроімпульса.

D-тригер,

що синхронізується фронтом, показаний

на рис. 6.14, а,

б

[89]. Він побудований на трьох елементних

тригерах, з них 2 тригери на елементах

DD1,…, DD4 утворюють схему синхронізації

основного осередку, що запам'ятовує, на

елементах DD5, DD6. З тимчасових діаграм

роботи D-тригера (рис. 6.14, в)

видно, що в паузах між синхроімпульсами

С = 0, і на виходах

*

підтримуються одиничні рівні незалежно

від стану входу D. Це відповідає режиму

зберігання інформації в основному

тригері. Перемикання рівня на вході D

впливає тільки на логічні стани виходів

А і В тригерів схеми синхронізації: якщо

D = 0 то В = 1 і А = 0, а у разі D = 1 маємо В = 0,

А = 1. При цьому один з тригерів схеми

синхронізації знаходиться в стійкому

стані, а інший — в режимі розриву зв'язків

тригерів при рівнях «логічної 1» на обох

виходах. Наприклад, якщо D = 0 то,

на виходах тригера на елементах DD3,

DD4 встановлюються однакові, рівні

.

По

позитивному фронту синхроімпульса, С

= 0

1 (рис. 6.14, в)

тригер, що знаходився до цього в режимі

розриву зв'язків тригерів, переходить

в нормальний стійкий стан і на входах

основного тригера формуються

взаємноінверсні логічні рівні. Якщо D

= 0, то

і тригер встановлюється в стан «0», якщо

D = 1, то

то відбувається установка в стан «1».

З діаграм (рис. 6.14,в) видно, що при С = 1 перемикання стану інформаційного входу D не впливає на стан даного D-тригера. Це пояснюється тим, що при установці основного тригера в стан «0» сигналом одночасно блокується логічний елемент DD4 і на його виході В = 1 незалежно від стану входу D. При установці основного тригера в стан «1» сигналом блокуються логічні елементи DD1 і DD3, тому перемикання станів D і В не впливає на стан основного тригера, тобто наскрізне управління в таких D-тригерах відсутнє.

Стани D-тригера, що синхронізується фронтом, описуються також рівнянням (6.14). Тривалість процесу перемикання і мінімальна тривалість синхроімпульса tвx min залежать від середнього часу затримки розповсюдження сигналу через логічні елементи

.

Застосування тригерів в схемі синхронізації обумовлює регенеративний режим перемикання її в новий стан, тому D-тригер (рис. 6.14) часто називають «защелкой». D-тригер типу «защелка» можна аналогічно реалізувати на елементах ИЛИ—НЕ.

Ще

один спосіб усунення наскрізного

управління в D-тригерах полягає у

використанні двотактних структур

MS-типу (Master — господар, що веде, Slave —

раб, відомий). Двотактний D-тригер

будується на основі двох D-тригерів, що

синхронізуються рівнями протифаз (рис.

6.15, а,

б).

Завдяки синхронізації синхроімпульсами

протифаз С і

запис нової інформації в тригери М і S

ступенів принципово розділений в часі,

що виключає наскрізну передачу інформації

з входу D на виходи QS

і

.

При

С = 0 тригер допоміжного ступеня М

знаходяться в режимі зберігання

інформації, а у вихідний тригер (ступінь

S) рівнем

= 1 дозволений перезапис вмісту тригера

М. Перемикання синхроімпульса С = 0

1 і

(рис. 6.15, в)

змінює режим роботи тригерів М і S: тригер

М переходить в режим запису інформації

з входу D, а тригер S — в режим зберігання

інформації, записаної на попередньому

кроці. У допоміжному тригері М можливий

режим запису, що не синхронізується,

протягом інтервалу синхроімпульса С =

1. Після закінчення синхроімпульса (С =

1

0) інформаційний вхід D блокується і в

основний тригер S переписується остаточно

сталий стан QМ.

Дозволяючий час по входу синхронізації при мінімально допустимій тривалості синхроімпульса tвx min = 3tзд.р.ср.

tроз = 7tзд.р.ср.

Виключення

режиму наскрізного управління дозволяє

використовувати синхронізовані фронтом

і двотактні D-тригери в рахунковому

режимі, для чого з'єднуються інформаційний

вхід D і інверсний вихід тригера (штрихова

лінія на рис 6.15, а).

У табл. 6.1 приведені параметри RS- і D-тригерів основних промислових серій, а на рис. 6.16 показані призначення і нумерація висновків, відповідних ІМС.

Т-тригери — послідовністні регенеративні бістабільні пристрої з одним управляючим входом Т, які -

кожним вхідним сигналом перемикаються в протилежний стан. Робота такого тригера описується рівнянням,

з якого виходить, що Т-тригер реалізує операцію складання по модулю 2. Тому Т-тригери, режим їх роботи і управляючий вхід називають рахунковими.

Асинхронний Т-тригер (рис 6.17, а, б) крім основного елементу RS-тригера, на логічних елементах DD5, DD6 який запам'ятовує, містить схему управління, що включає лінії затримки DD1, DD4 і логічні вентилі DD2, DD3. Ліні затримки забезпечують протягом часу (рис. 6.17, в) підтримку на входах елементів DD2, DD3 логічних рівнів, відповідних попередньому стану Т-тригера. Для забезпечення роботи Т-тригера без збоїв необхідна затримка перемикання логічних рівнів на DD2, DD3 на величину перевищуючу тривалість рахункового імпульсу tT 2tзд.р.ср.

Типономінал |

Функціональне призначення |

Iпот. мА не більш |

tзд.р.вс не більш |

УГО (рис.6.16) |

|

К561 ТР2 |

Чотири RS-тригери |

2,0 |

300 |

а |

|

К155ТМ2 |

Два D-тригери |

30 |

40 |

б |

|

ТМ5 |

Чотири D-тригери |

53 |

25 |

у |

|

ТМ7

|

Чотири D-тригери з прямими і інверсними виходами |

53 |

25 |

г |

|

ТМ8 |

Счетверенний D-тригер |

- |

35 |

д |

|

К531ТМ2п |

Два D-тригери |

50 |

13,5 |

у |

|

КМ8п |

Чотири D-тригери |

96 |

22 |

е |

|

ТМ9п |

Шість D-тригерів |

- |

22 |

же |

|

К561ТМ2 |

Два D-тригери |

0,003 |

150 |

у |

|

К561ТМ3 |

Чотири D-тригери |

0,003 |

700 |

і |

|

К500ТМ130 |

Два D-тригери |

35 |

4,0 |

н |

|

К500ТМ131 |

Два D-тригери |

56 |

4,5 |

п |

|

К500ТМ231 |

Два D-тригери |

65 |

3,3 |

п |

|

К500ТМ133 |

Чотири D-тригери типу «защелка» |

75 |

5,4 |

п |

|

К500ТМ134 |

Два D-тригери |

55 |

5,5 |

п |

|

К500ТМ173 |

Чотири D-тригери з вхідним мультиплексором |

66 |

6,2 |

р |

|

К155ТЛ1 |

Два тригери Шмідта з логічним елементом 4И-НЕ на вході |

32 |

27 |

с |

|

ТЛ2 |

Шість тригерів Шмідта з інверсними виходами |

60 |

22 |

д |

|

ТЛ3 |

Чотири двовходових тригери Шмідта |

40 |

22 |

л |

|

К555ТЛ2 |

Шість тригерів Шмідта з інверсними виходами |

21 |

22 |

м |