ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 14.12.2021

Просмотров: 446

Скачиваний: 3

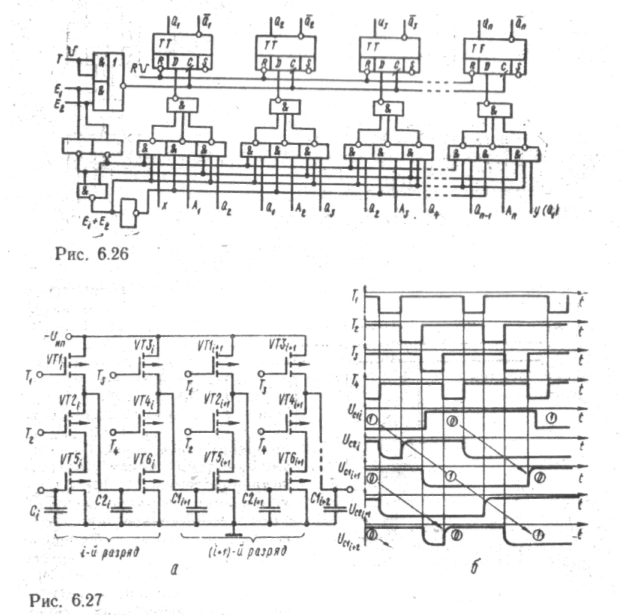

На рис. 6.27,а показана схема 4-тактного динамічного регістра на р-МДП-транзисторах, кожен розряд якого виконаний на шести транзисторах VT1, ..., VT6. Кожен розряд містить два тактовані ключі на транзисторах відповідно VT1, VT2, VT5 і VТ3, VТ4, VТ6 C1 і С2 — еквівалентні вхідні ємності ключів.

Нехай

на вхід i-го розряду поступає від (і—1)-го

розряду логічний сигнал X = 1 якому

відповідає електричний сигнал

і всі інші ємності решти розряджені.

Тактовий імпульс Т1

(рис. 6.27, б)

відкриває транзистори VТ1 всіх розрядів

і конденсатори С2

через них заряджають до напруги

.

Тактовий імпульс Т2

відкривають транзистори VT2

і залежно від стану транзисторів VT5

який визначається напругами на

конденсаторах С1, конденсатори С2 або

розряджаються через транзистори VT2 і

VT5, або зберігають заряд і напругу, якщо

відповідний транзистор VТ5 замкнутий.

У даному прикладі транзистор

VТ5i на, такті Т2 відкритий, а VТ5i+1, закритий, тому С2i розряджається тоді як Сi+1, зберігає заряд. Тактовий імпульс Т відкриває транзистори VT3 розрядів і обумовлює заряд конденсаторів С1. На наступному такті T4 відкриваються транзистори VT4 і залежно від стану транзисторів VT6, який залежить від напруги на конденсаторах С2, відбувається розряд конденсаторів С1 через послідовно сполучені відкриття транзистори VТ4 і VT6, або конденсатор С1 зберігає заряд. На тимчасовій діаграмі (рис. 6.27, б) видно, що С1i+1, зберігає заряд, а С1i+2 розряджається через VT4 і VT6i+1. Таким чином, за 4-тактний цикл «логічні 0 і 1» зсовуються на один розряд (показано стрілками на рис. 6.27, б).

Основна

перевага динамічного регістра на МДПУ

транзисторах — низьке споживання

потужності. Це, обумовлено відсутністю

наскрізних струмів в ключах, комутованих

зсунутими в часі тактовими імпульсами

T1,

Т2

і Т3,

Т4.

Споживання потужності пов'язане тільки

із зарядом паразитних конденсаторів

С1, С2. Завдяки цьому при виготовленні

багаторозрядних динамічних регістрів

можливий вельми високий ступінь

інтеграції елементів.

Недолік динамічних регістрів — обмеження зверху тривалості тактових імпульсів, яке пов'язане з кінцевим часом зберігання заряду на паразитних ємностях МДП-транзисторів. Внаслідок цього робоча частота динамічного регістра обмежена

Інший недолік — складність тактування регістра чотирма зсунутими в часі тактовими послідовностями.

Відмічені достоїнства і недоліки властиві і динамічним регістрам на основі приладів із зарядним зв'язком (ПЗС) [34]. Регістри на основі ПЗС відносяться до елементів функціональної електроніки, у яких немає чітких меж між електронними компонентами. Тому протікаючі в них процеси розглядаються в деякому середовищі з розподіленими параметрами.

Функціонування ПЗС-регістра засноване на тому, що в кожній із складаючих його послідовно розташованих МДП-структур можна створити локальний приповерхневий заряд неосновних носіїв і перемиканням потенціалів затворів відповідними тактовими послідовностями переміщати цей заряд вздовж каналу від деякого вхідного електроду до вихідного. Сукупність МДП-структур ПЗС регістра формується на загальній напівпровідниковій підкладці (рис. 6.28). Зарядний пакет утворюється в області електроду-інжектора і управляючою напругою Uи. Переміщення зарядного пакету вздовж каналу синхронізується тактовими імпульсами на фазових електродах Ф1, Ф2, Ф3. Імпульсний вихідний сигнал формується при досягненні зарядним пакетом вихідного електроду Q. Окрім названих ПЗС-регістр може також містити управляючі електроди V1 (для відключення інжектора від каналу) и/или V2, (для відключення вихідного електроду від каналу).

Процеси формування, зберігання протягом обмеженого часу і направленої передачі зарядних пакетів пов'язані з розподілом потенціалів в напівпровіднику каналу при заданих напругах на зовнішніх електродах і ілюструються зонною діаграмою (рис. 6.29). Приблизно через 1 пс після, того, як напруга на деякому затворі перевищить порогову напругу Uпор основні носії переходять в глиб напівпровідника, утворюючи збіднений шар завглибшки Хо.с поверхневим потенціалом Еn. У поверхні утворюється потенційна яма для неосновних носіїв, куди вони «скочуються» із збідненого шару сусіднього елементу під впливом електричного поля.

Оскільки швидкість термогенерації неосновних носіїв відносно велика, потенційну яму можна використовувати тільки для тимчасового зберігання несучих інформацію зарядних пакетів. Максимальний час зберігання зарядних пакетів обмежено процесами рекомбінації і має порядок десятків наносекунд [56].

Для управління роботою ПЗС-регістра можна використовувати одно- і двоступеневі імпульси. На практиці частіше використовується управління одноступінчатими імпульсами з тимчасовим перекриттям фазових послідовностей (рис. 6.30).

Під дією напруги Uu на інжекторі за час інжекції tu формується зарядний пакет

де Іо.н — зворотний струм інжекторного р-n-переходу; — температурний потенціал.

У

міру переміщення зарядного пакету, що

синхронізується, уздовж каналу

ПЗС-регістра він зменшується за рахунок

інерційності неосновних носіїв,

рекомбінації з термогенерованими

носіями, а також часткової зворотної

передачі. Струм Іq

вихідного електроду Q містить дві

складові струм ІО

і назад-зміщеного р-n-переходу,

до якого прикладено напругу Uq,

і струм Із.п

інформаційного зарядного пакету

Закінчений підсилювач по імпульсу струму IQ формує вихідний імпульс ПЗС-регістра. ПЗС-регістри зберігають працездатність в діапазоні частот фазових імпульсів Iф = 50…2000 Мгц [56].

Динамічні регістри застосовують як цифрові лінії затримки, в пристроях з послідовною обробкою інформації і в послідовних ОЗУ великої ємності.

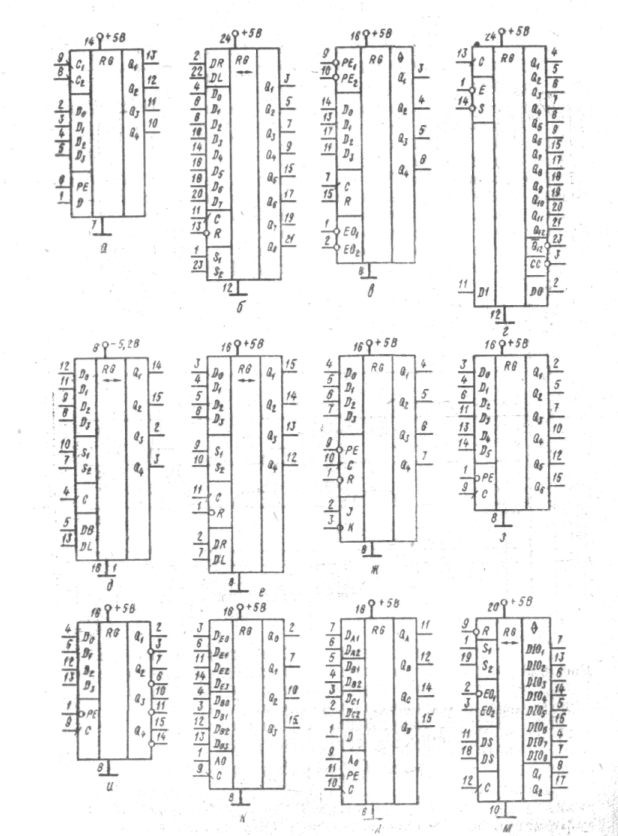

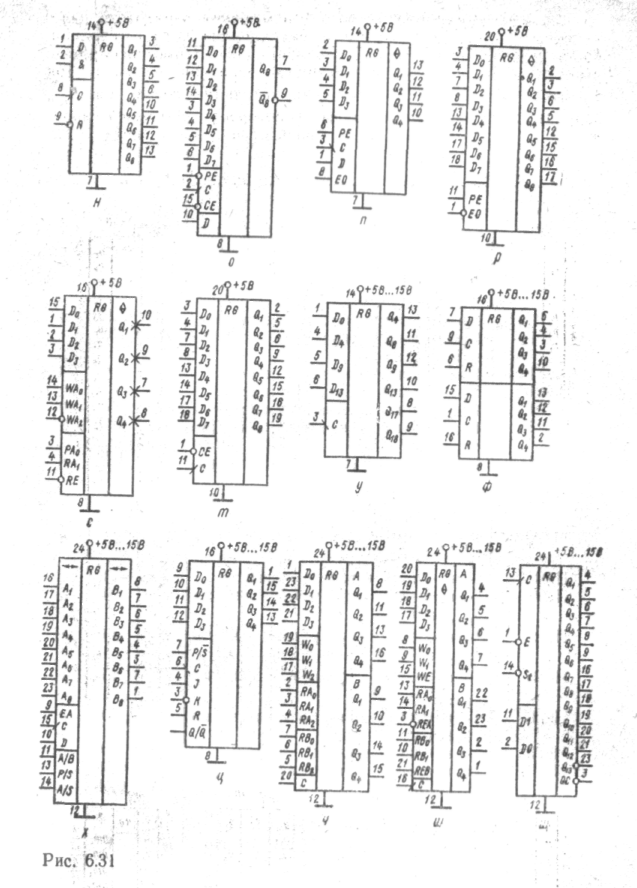

У

табл. 6.5 приведені параметри регістрів

промислових серій цифрових ІМС, а на

рис. 6.31 — їх умовні графічні позначення.

6.3 Лічильники

Лічильниками називають послідовністні цифрові пристрої, призначені для підрахунку і запам'ятовування числа імпульсів, поданих в певному тимчасовому інтервалі на його рахунковий вхід. Крім рахункового лічильники можуть ще мати входи асинхронний або синхронної установки початкових станів. За характером зміни станів лічильника рахунковими імпульсами розрізняють лічильники, що підсумовують, віднімають і реверсивні [61, 83]. За способом організації перенесень між розрядами їх можна розділити на лічильники з послідовним, наскрізним, паралельним і комбінованим перенесенням. Лічильники з послідовним і наскрізним перенесенням називають асинхронними, а з паралельним перенесенням — синхронними. Звичайно лічильник містить один або декілька ідентичних розрядів, побудованих на основі двійкових тригерів. Кількість помітних станів розряду лічильника є його класифікаційною ознакою, згідно якому лічильники називають двійковими, двійково-десятковими і т.д.

Основними технічними параметрами лічильників є коефіцієнт перерахунку Ксч і швидкодія. Коефіцієнт Ксч є числом помітних стійких станів лічильника і якщо кожен рахунковий імпульс переводить лічильник в новий стан, то Ксч дорівнює максимальному числу імпульсів, яке лічильник може прорахувати і запам'ятати без повторення, станів. Швидкодія лічильника визначається максимальною частотою проходження рахункових імпульсів Іmах реєстрованих лічильником без збоїв, максимальною частотою перемикання станів лічильника fсліч.mах і часом установки tуст станів лічильника, визначуване як максимальний часовий інтервал від моменту надходження рахункового імпульсу до моменту переходу всіх розрядів лічильника в новий стійкий стан.

Асинхронні лічильники. У асинхронних лічильниках відсутня загальна для всіх розрядів синхронізація і перехід розрядів в нові стани відбувається послідовно розряд за розрядом, починаючи від вхідного, на який поступають рахункові імпульси. Якщо розглянути послідовність станів наприклад, 4-розрядного підсумовуючого двійкового лічильника, (табл. 6.5), то з неї видно, що ознакою зміни станів будь-якого з розрядів лічильника є перемикання попереднього розряду (або вхідного сигналу) із стану «1» в «0». Саме так поводяться двотактні Т і JK-тригери, розглянуті в розділі 6.1. Таким чином, послідовний лічильник, що працює згідно табл. 6.6, можна виконати у вигляді ланцюжка Т-тригерів, для кожного з яких рахунковий імпульс формується тригером сусіднього молодшого розряду (рис. 6.32,а). Як було показано в розділі 6.1, рахунковий режим JK-тригера, має місце у разі J = К = 1. На рис. 6.32,а входів J і К тригерів вільні, що звичайно еквівалентно подачі на входи J і К рівнів «1». З тимчасової діаграми

Таблиця 6.6.

|

Вага |

Вихід |

Десятковий еквівалент двійкового коду |

||||||||||||||||

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

0 |

||

Вхід |

||||||||||||||||||

|

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 1 |

0 |

||

|

20 |

Q1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

21 |

Q2 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|

22 |

Q3 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

23 |

Q4 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

(рис. 6.32,б) видно, що час встановлення лічильника tуст.ліч. залежить від кількості розрядів, що послідовно перемикаються, і для N-розрядного лічильника воно змінюється в межах

,

де

tвстT

= 0,5

— середній час встановлення тригера.

Максимальна частота проходження

рахункових імпульсів fmах

визначається незалежно від структури

лічильника граничною частотою перемикання

першого тригера. Якщо ж вимагається

розрізняти (дешифрувати) кожен стан

лічильника, то до подачі чергового

рахункового імпульсу всі розряди повинні

встановитися в новий

стан на час t0. В цьому випадку максимально допустима частота зміни станів fліч.maх визначається по якнайгіршому часу встановлення

(6.18)

Основна перевага послідовного лічильника — мінімальні витрати мікросхем і мінімум електричних зв'язків, що спрощує розводку ліній зв'язку і підвищує перешкодозахисну схеми. Головний недолік — низька швидкодія, яка тим нижча, чим більше коефіцієнт рахунку Кліч = 2N і чим більше в лічильнику розрядів N.

Один із способів збільшення швидкодії асинхронних лічильників полягає в організації перенесень між розрядами через додаткові логічні елементи (рис. 6.33). Якщо перший тригер лічильника (рис. 6.33,а, в) знаходиться в стані «l», то наступний рахунковий імпульс Т скидає його в стан «0» негативним фронтом. Як видно з тимчасових діаграм (рис. 6.33,б), ще до перемикання виходу Q1 тригера DD1 рахунковий імпульс Т через вентиль DD2 поступає у вигляді імпульсу перенесення Р1 на вхід другого розряду і вентиль DD4, і якщо Q2 = 1, то рахунковий імпульс проходить далі через вентиль DD4 і т.д. Рахунковий імпульс Т проходить до вентиля, на другий вхід якого поступає Q1 = 0. При цьому тригери з першого до (і - 1)-го встановлюються в «0», а і-й тригер — в стан «1» (рис. 6.33,б). У N-розрядному лічильнику з наскрізним перенесенням час встановлення визначається затримкою рахункового імпульсу Т в колах перенесення і часом встановлення tуст останнього з тригерів, що перемикаються

Тоді максимальна частота рахунку

,

виявляється, вище, ніж частота послідовного лічильника, визначувана формулою (6.18), оскільки — 1 вентиль И перемикаються значно швидше, ніж N — 1 тригер.

З точки зору структури, функціонування і технічних параметрів варіанти асинхронних лічильників (рис. 6.33 а, в) еквівалентні. Залежно від кількості розрядів N вони реалізують коефіцієнт рахунку Кліч = 2N і їх можна використовувати, як дільники частоти.

(6.19)

Часто при проектуванні цифрових пристроїв виникає необхідність в дільниках частоти, для яких Кліч у виразі (6.19) — будь-яке ціле число. Якщо в арсеналі схемотехніка є прості дільники частоти з коефіцієнтами рахунку Кліч = 2, 3, 4, 5, 6, 7, 8, 9, 10, та велика кількість дільників частоти з Кліч, що розкладається на прості множники, будуються на їх основі. Необхідні Кліч одержують введенням в лічильники зворотних зв'язків. На рис. 6.34, а-в показані послідовні лічильники для Кліч заданих однорозрядним