Файл: Лекции внутреннее построение микропроцессора Арифметикологическое устройство (алу).docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 05.12.2023

Просмотров: 21

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Работа АЛУ без регистров временного хранения данных невозможна. Когда в арифметической или логической операций АЛУ участвуют два слова данных, одно из них из аккумулятора. Результат подобной операции помещается в аккумулятор. Буфер аккумулятора позволяет избежать ситуации, при которой вход и выход АЛУ одновременно подсоединены к одной и той же точке схемы. Буферные регистры недоступны для программирования.

10. Регистры общего назначения (РОН)

В некоторых МП РОН служат в качестве запоминающих устройств, это позволяет повысить быстродействие микро-ЭВМ за счет сокращения пересылок кодов между МП и памятью. В некоторых МП функциональные возможности этих регистров не уступают возможностям аккумулятора. Последнее достигается в том случае, если АЛУ может помещать в них данные.

Регистры общего назначения BC, DE, HL могут быть использованы как шесть 8-разрядных или три 16-разрядные пары регистров в зависимости от текущей выполняемой команды. Выборка команд длиной 2 и 3 байт производится с участием регистров W и Z. Первый байт команды заносится в регистр команд, второй - в регистр W, а третий - в регистр Z. Регистры W и Z программно недоступные. Пара HL обычно используется для указания адреса. Остальные РОН являются регистрами хранения данных. В нашем случае АЛУ не помещает данные в РОН, поэтому они не обладают возможностями аккумулятора. РОН представляет собой сверхоперативную память МП.

11. Указатель стека (Stack Pointer - (SP))

Указатель стека (SP) представляет 16-разрядный регистр, который содержит адрес последнего помещенного в стек байта. Указатель стека декрементируется при каждом помещении в стек и инкрементируется при каждом извлечении из него.

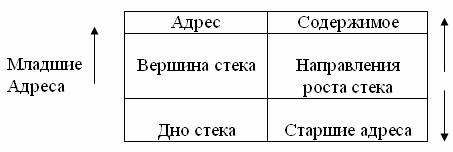

Стек – это область памяти, специально выделяемая для временного хранения данных программы. Отличительной особенностью стека является особая организация обращения к нему со стороны МП. Запись и чтение данных в стеке осуществляется в соответствии с принципом LIFO (Last In First Out) – «последним пришел, первым ушел». Таким образом, информация в стеке размещается в строгой последовательности – ячейка памяти, заполненная последней, считывается первой, а ячейка памяти заполненная первой извлекается последней. В ячейки стека информация заносится последовательно и извлекается в порядке обратном порядку занесения. Таким образом, стек функционирует как память с последовательным доступом. По мере записи данных в стек он растёт в сторону младших адресов. Эта особенность заложена в алгоритм команд работы со стеком. Концептуальная схема организации стека показана на рисунке.

Стек предназначен для обработки прерываний и программ. При записи слова данных в ячейку стека значение адреса в указателе стека уменьшается на единицу, а при считывании данных увеличивается на единицу.

Стек выполняется на некоторой выделенной области ОЗУ. В этом случае стек представляет память с последовательным доступом. Обращение и адресация к стеку производится через регистр указателя стека.

Стек на внутренних регистрах МП более быстродействующий, но из-за малого числа регистров, имеющихся в МП, не обеспечивается большая глубина вложения данных. Поэтому стеки большинства МП размещаются в памяти.

Вершиной стека называется адрес его последней загруженной ячейки памяти. Таким образом, указатель стека всегда содержит адрес его вершины. Начало стека в ОЗУ (его дно) определяется программистом путём записи в регистр SP адреса первой ячейки памяти стека. Вершина стека подвижна и её расположение определяется объёмом данных, загруженных в стек. Стек не имеет ограничений, за исключением тех, которые обусловлены наличием других программ в ОЗУ.

12. Схема управления

Схема управления состоит из дешифратора команд и устройства управления и синхронизации. Одна из главных функций схемы управления – декодирование команды. Для этого служит дешифратор команд. Он декодирует команду, находящуюся в регистре команд и выдаёт сигналы, необходимые для выполнения команды, в устройство управления. Основу устройства управления МП составляют программируемые логические матрицы (ПЛМ). Дешифратор анализирует отдельные биты команды и передаёт код операции в устройство управления. Устройство управления получает сигналы от дешифратора команд для определения природы выполняемой команды. Устройство управления получает также информацию от регистра состояния в случае условного перехода. Сигналы управления и синхронизации передаются во все блоки МП для координации выполнения команд и управления внешними устройствами (ОЗУ, ПЗУ, УВВ).

Устройство управления связано с генератором тактовых импульсов, синхронизирующим во времени работу МП. Принимаемые тактовые сигналы схемой управления преобразуются в многофазные синхросигналы. В качестве ГТИ используют кварцевый генератор – внешний или внутренний, встроенный в МП.