ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 09.01.2024

Просмотров: 14

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

УНИВЕРСИТЕТ ТЕЛЕКОММУНИКАЦИЙ им. проф. М.А. Бонч-Бруевича

ФАКУЛЬТЕТ ВЕЧЕРНЕГО И ЗАОЧНОГО ОБУЧЕНИЯ

Контрольная работа

по дисциплине «Электроника»

Вариант 19

Фамилия: Полещук

Имя: Ольга

Отчество: Павловна

Курс: 2

Студ. билет №2010484

Группа № ОБ-06с

Санкт-Петербург

2022

Задача №1

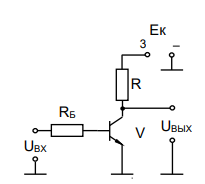

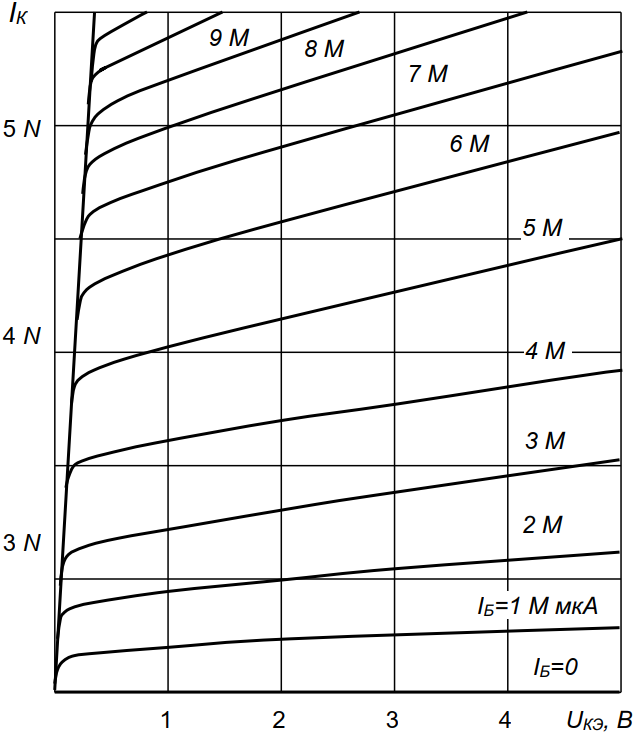

Дано: Схема электронного ключа на биполярном транзисторе приведена на рисунке 1. Значения элементов схемы и масштабные коэффициенты N и M представлены в таблице исходных данных.

Рисунок 1 – Схема электронного ключа на биполярном транзисторе

Требуется:

1. Построить статическую передаточную характеристику ключа.

2. Определить основные параметры ключа: уровни логических нуля U0 и единицы U1, логического перепада UЛ, минимальные уровни отпирающей и запирающей помех U0П и U1П, коэффициент помехоустойчивости КП.

3. Описать принцип работы ключа и указать, в каких базовых логических элементах он используется.

1 Построить статическую передаточную характеристику ключа

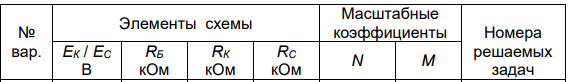

Выходные характеристики биполярного транзистора снимаются при постоянном значении тока базы. Пример семейства выходных характеристик БТ, включенного по схеме с общим эмиттером, приведен на рисунке 2.

Рисунок 1 – Выходные характеристики биполярного транзистора в схеме с ОЭ

Начальные участки характеристик соответствуют режиму насыщения, а участки с малым наклоном – активному режиму биполярного транзистора. Переход от режима насыщения к рабочему режиму биполярного транзистора происходит при значениях |U

кэ|, превышающих |Uбэ|. Режим отсечки биполярного транзистора соответствует токам, меньшим Iб = 0.

Наклон выходных характеристик определяет выходное сопротивление транзистора в схеме с общим эмиттером. Относительно большой наклон этих характеристик (по сравнению со схемой включения транзистора с общей базой) связан с влиянием эффекта модуляции толщины базы (эффект Эрли). При увеличении напряжения Uкэ возрастает напряжение Uкб, что приводит к уменьшению толщины базовой области транзистора, а значит уменьшению тока базы. Для сохранения тока базы на прежнем уровне приходится увеличивать напряжение Uбэ, что приводит к росту Iк.

Найдем Iк, согласно исходным данным:

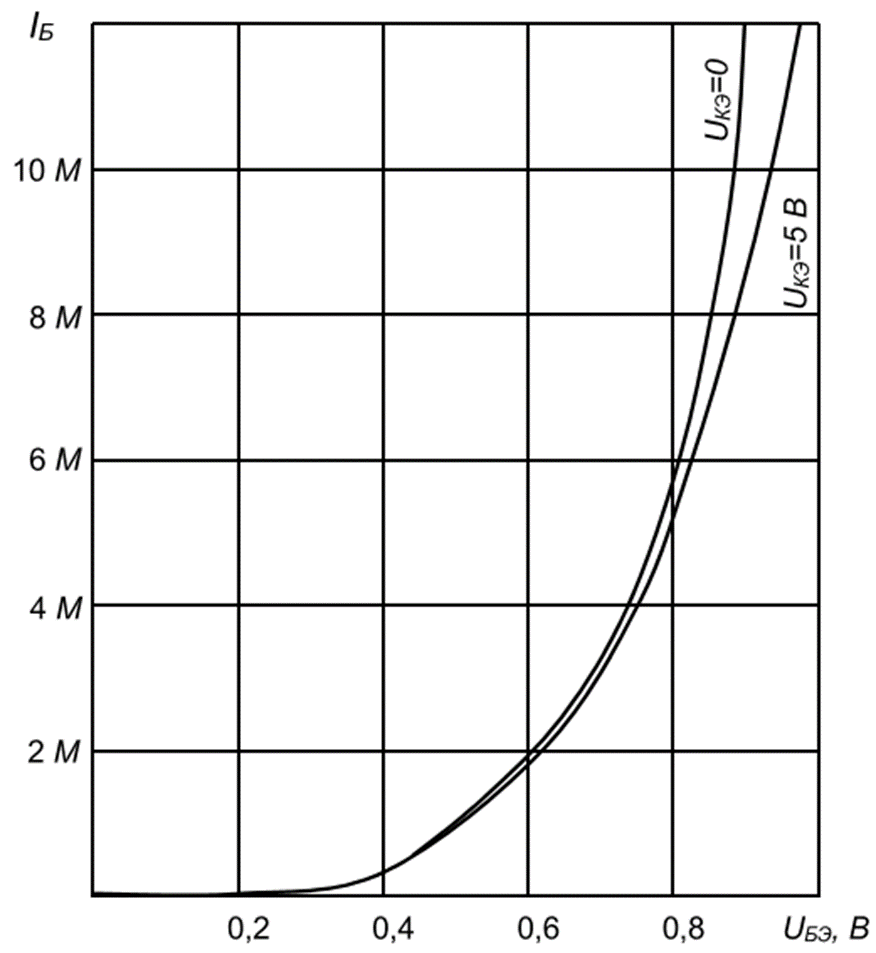

Для снятия входных характеристик биполярного транзистора зафиксируем напряжение на коллекторе. Зависимость тока базы от напряжения на базе и будет входной характеристикой транзистора.

Напряжение на входе ключа можно определяется по входным характеристикам, показанным на рисунке 3.

Рисунок 3 – Входные характеристики биполярного транзистора

Благодаря графикам входных и выходных характеристик заполняем значения таблицы 1.

Таблица 1 – Данные для построения передаточной характеристики

| Iб, мкА | 0 | 40 | 80 | 120 | 160 | 200 | 240 | 280 | 320 |

| Uбэ, В | 0,3 | 0,51 | 0,62 | 0,71 | 0,76 | 0,80 | 0,82 | 0,86 | 0,90 |

| Uвх, В | 0,3 | 0,698 | 0,996 | 1,274 | 1,512 | 1,74 | 1,948 | 2,176 | 2,404 |

| Uвых, В | 5,0 | 4,2 | 3,3 | 2,5 | 1,6 | 0,6 | 0,2 | 0,2 | 0,2 |

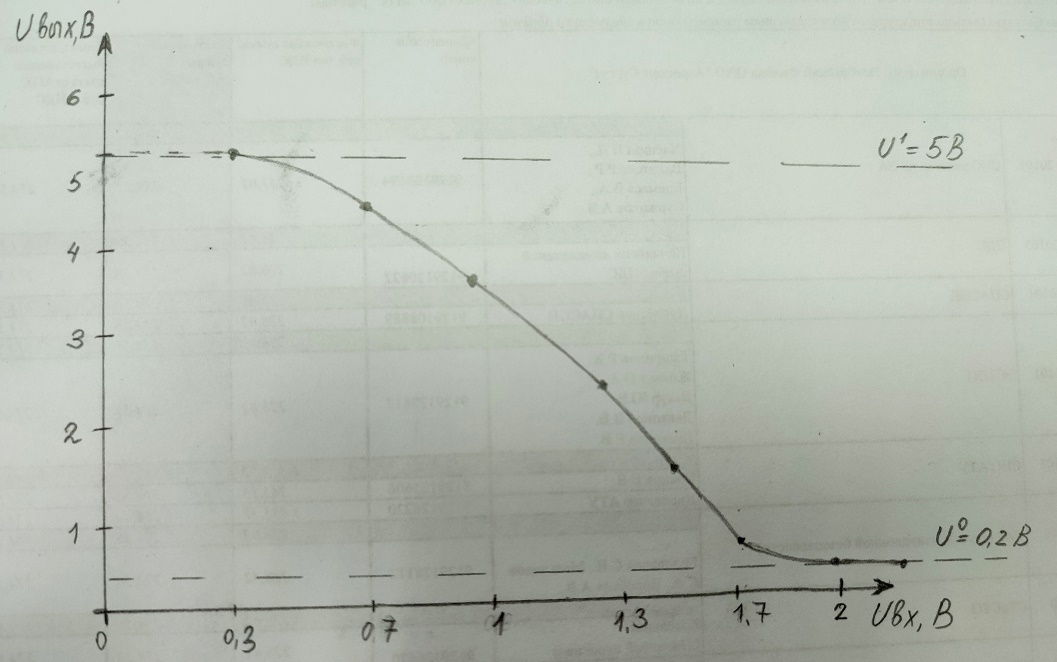

Построим график зависимости Uвых от Uвх, рисунок 4.

Рисунок 4 – график передаточной характеристики

-

Определить параметры ключа.

Значения напряжений на ключе можно определить по графику передаточной характеристики, на которой видно перепад (из 1 в 0). Напряжение логической единицы U1= 5В. Напряжение логического нуля U0= 0,2 В.

Теперь можно рассчитать величины помех, для их нахождения нужно узнать пороговые напряжения – это напряжения в момент, которого транзистор либо начинает пропускать ток (при логической единице) или если приложить напряжение меньше, то транзистор будет закрыт (логический ноль). Как видно из нашего графика:

U1пор = 2В; U0пор = 0,3В.

Отпирающее напряжение находим по формуле:

U0п = U0пор – U0 =0,3В – 0,2В= 0,1В.

Запирающее напряжение находим по формуле:

U1п = U1пор – U1 =5В – 2,0В= 3В.

Коэффициент помехоустойчивости:

КП =

3.Принцип работы транзисторного ключа

Сделанные из кремниевых транзисторов типа п-р-п являются одним из основных элементов интегральных микросхем, они также могут быть реализованы и на дискретных элементах. Переход к транзисторам типа р-п-р сводится лишь к изменению полярности источников питания (в тех случаях, когда такой переход связан со схемными изменениями, они оговариваются дополнительно). Наибольшее распространение получил транзисторный ключ по схеме с общим эмиттером. Транзисторный ключ может находиться в одном из двух состояний: выключено, когда транзистор закрыт и ключ разомкнут, и включено, в этом случае транзистор открыт и ключ замкнут.

Ключем управляют, подавая на его вход управляющее напряжение Uвых. Включенному состоянию соответствует низкий положительный уровень входного сигнала Uвых=U0. Включенное состояние обеспечивается высоким положительным уровнем входного сигнала Uвых=U1. Ключ удерживается в одном из состояний, пока на входе сохраняется соответствующий уровень сигнала. Резистор R ограничивает ток базы, R

к – коллекторная нагрузка, Ек – источник коллекторного напряжения. Транзистор ключа описывается с помощью семейства входных и выходных характеристик.

Особенностью входных характеристик кремниевого транзистора является наличие достаточно большого порога отпирания Uп. При напряжении на базе, меньшем порога отпирания, транзистор всегда закрыт.

Для анализа работы ключа на семейство выходных характеристик наносят нагрузочную прямую, соответствующую определенному сопротивлению резистора Rк и пересекающую координатные оси в точках Ек и Ек/Rк. При изменении базового тока iб рабочая точка перемещается вдоль этой прямой, определяя в каждый момент времени коллекторный ток, напряжение между коллектором и эмиттером и режим работы транзистора.

Задача №2

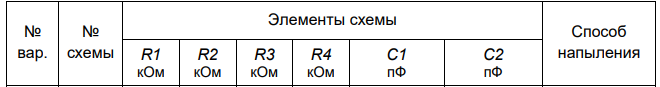

Дано: На рисунке 4 представлена схема аналогового устройства на базе операционного усилителя – Неинвертирующий интегратор.

Рисунок 5 – Неинвертирующий интегратор.

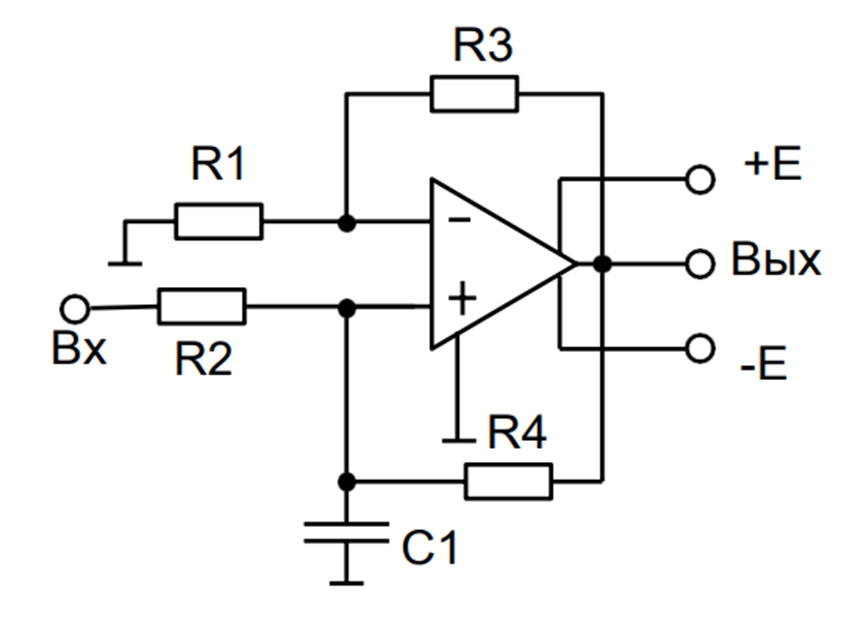

Рисунок 6 - Обозначения выводов и размеры бескорпусного ОУ

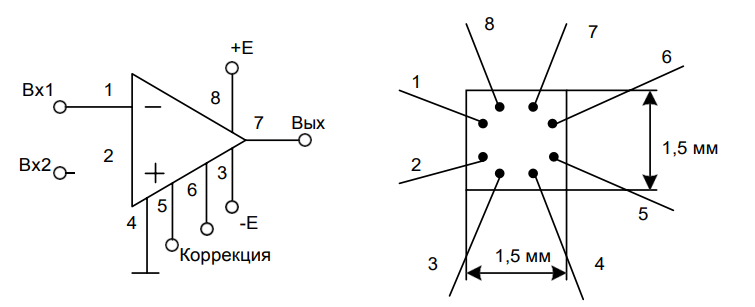

Преобразуем заданную электрическую схему таким образом, чтобы все внешние выводы находились на краю длинных сторон подложки и были исключены пересечения плёночных проводников. Для этого заменим взаимные пересечения плёночных проводников пересечением плёнки и выводов навесного бескорпусного ОУ.

Рисунок 7 – Преобразованная схема неинвертирующего интегратора

Решение

Рассчитаем размеры пассивных элементов. Коэффициент формы Кф всех резисторов находим по формуле:

где Ri – сопротивление резистора,

ps – удельное поверхностное сопротивление материала.

Выберем в качестве материала сплав РС3001, имеющий ps=2000 Ом/квадрат

Кф1 = 10000:2000 = 5;

Кф2 = 20000:2000 = 10;

Кф3 = 20000:2000 = 10;

Кф4 = 100000:2000 = 50.

Так как 1< Кф1, Кф2, Кф3 ≤10, то резисторы R1 – R3 имеют прямоугольную форму, а резистор R4 выполняется в форме меандра. Взяв минимальную ширину резистора bmin = 0,2 мм, находим длину резисторов:

L1 = Кф1 ‧ bmin = 5 ‧ 0,2 = 1 мм;

L2 = Кф2 ‧ bmin = 10 ‧ 0,2 = 2 мм;

L3 = Кф3 ‧ bmin = 10 ‧ 0,2 = 2 мм;

L4 = Кф4 ‧ bmin = 50 ‧ 0,2 = 10 мм.

Площадь, занимаемая резисторами, составляет:

SR = 1‧0,2 + 2‧0,2 + 2‧0,2 + 10‧0,2=3мм2 =0,03см²

Площадь плёночных конденсаторов находим с помощью значений удельной ёмкости С0 для разных типов диэлектрических плёнок, в нашем варианте моноокись кремния (С0 =10000пФ/см2)

Sс = Sс1 =С1 /С0 = 20000/10000= 2 см²

Бескорпусный ОУ занимает площадь:

Sоу =1,5‧1,5=2,25мм²

Общая площадь, занимаемая всеми элементами, составляет:

S ∑ = 0,03 + 2 + 0,0225 = 2,0525см²

Учитывая площадь соединений, промежутки между элементами ИМС и расстояние от края подложки следует увеличить в несколько раз. При выборе подложки необходимо обеспечить условие: 2 ≤ Sп≤ 3.

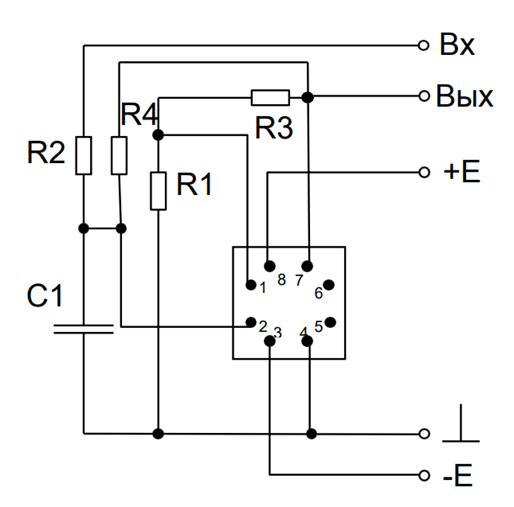

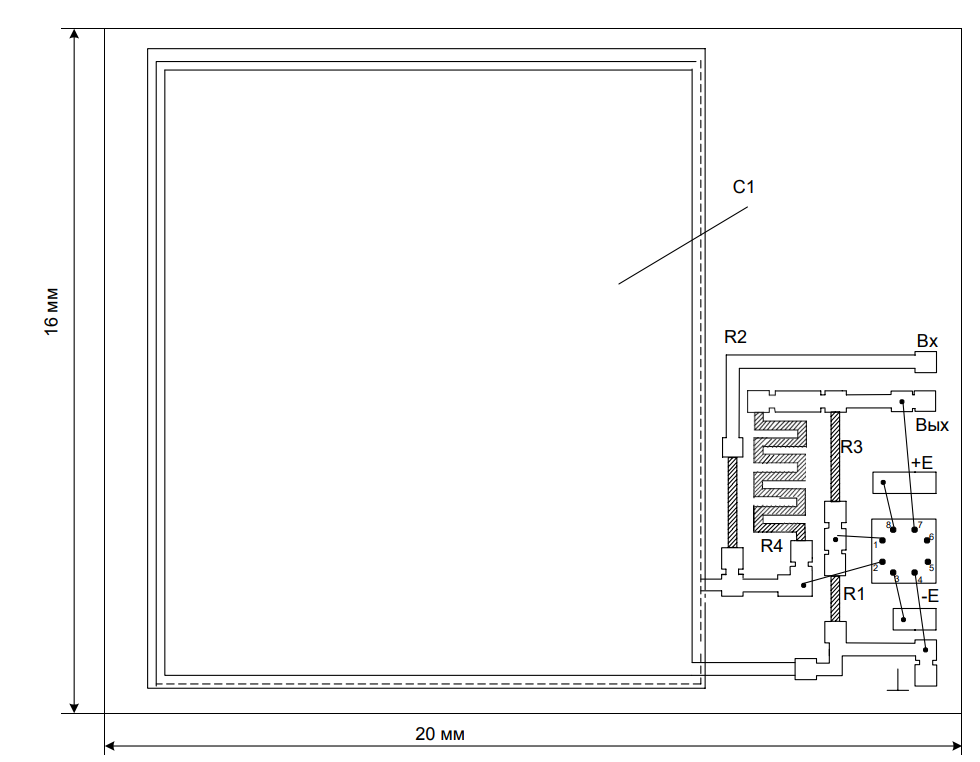

В нашем случае может быть использована подложка минимального размера 20х16мм. Эскиз топологии выполнен в масштабе 10:1 на рис.4. При составлении эскиза учитывались основные правила, накладываемые тонкоплёночной технологией.

Рисунок 8 – Чертёж топологии гибридной ИМС неинвертирующего интегратора