ВУЗ: Томский государственный университет систем управления и радиоэлектроники

Категория: Учебное пособие

Дисциплина: Электроника

Добавлен: 23.10.2018

Просмотров: 6046

Скачиваний: 13

116

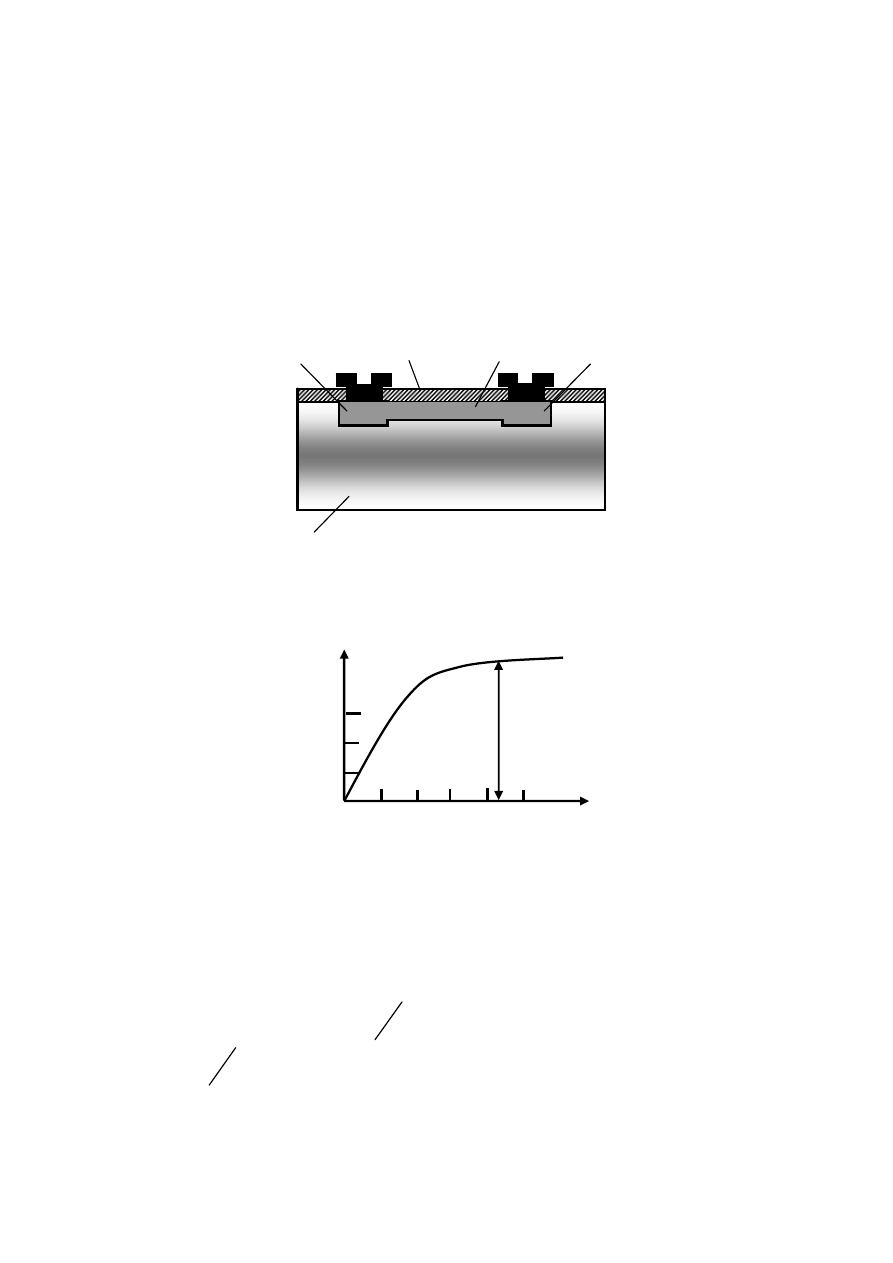

На рис. 12.4 показан ионно-легированный резистор в арсе-

нид-галлиевой микросхеме (1 — резистивный слой, 2 — полуи-

золирующая подложка, 3 — контактные области). Так как под-

ложка является изолятором, паразитная емкость пренебрежимо

мала. Из-за большой подвижности электронов сопротивление

слоя при той же дозе легирования (

ЛД

ЛА

N

N

=

) на порядок мень-

ше, чем в кремниевых микросхемах.

SiO

2

3

1

2

n

+

n

+

3

Рис. 12.4 — Интегральный резистор

при асенид-галевой технологии

0

1

3

5

1

3

I

Э

, мА

U, В

I

НАС

Рис. 12.5 — Вольт-амперная

характеристика резистора

При малой длине резистора его ВАХ нелинейна (рис. 12.5),

что обусловлено эффектом насыщения дрейфовой скорости элек-

тронов. Он проявляется, когда напряженность электрического

поля в слое 1, равная

U

a

, превышает критическое значение

0,3

КР

B

E

мкм

=

.

117

12.2

Пленочные

резисторы

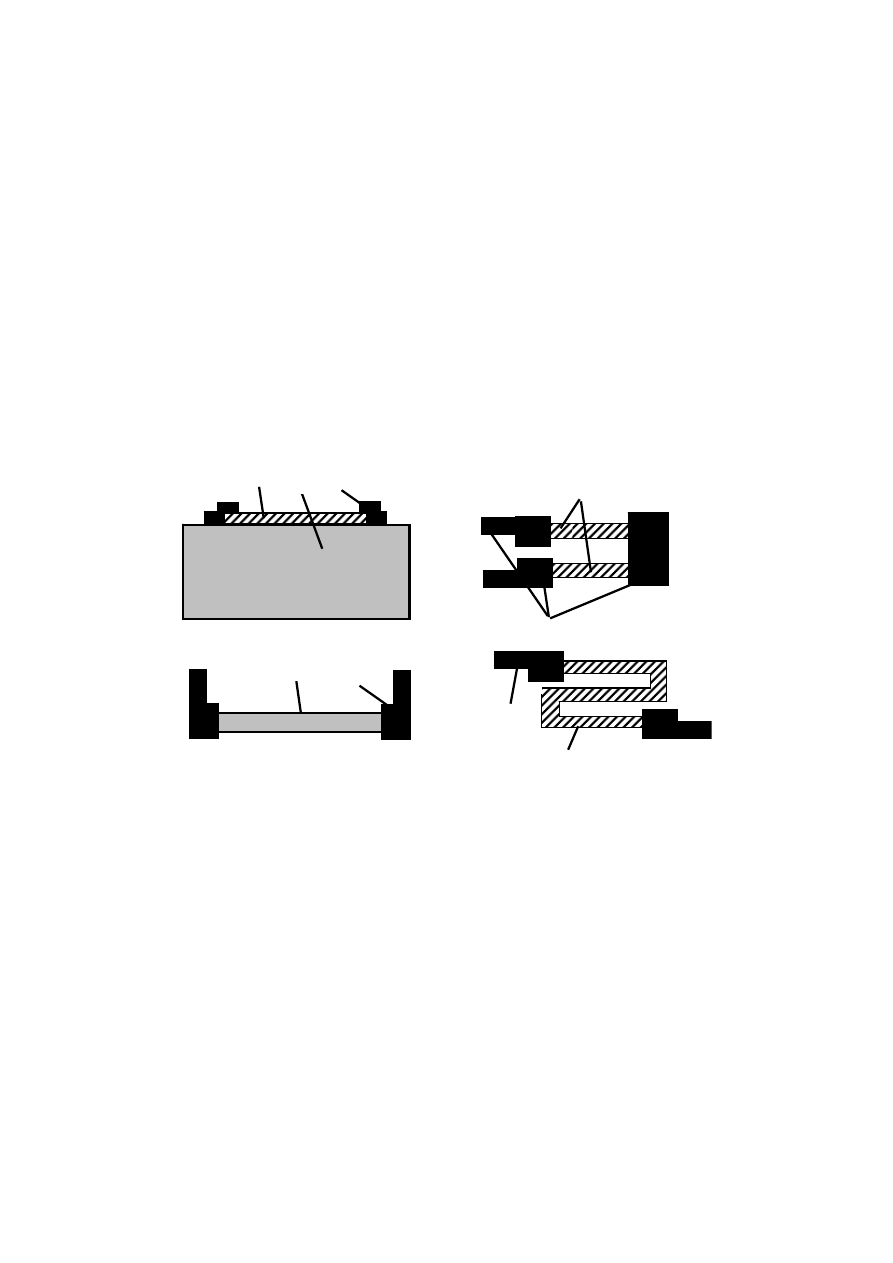

Структура резистора гибридной микросхемы показана

на рис. 12.6,

а

(1 — резистивный слой, 2 — подложка, 3 — ме-

таллические контакты) В зависимости от требуемого сопротивле-

ния резистор может иметь конфигурацию полоски (рис. 12.6,

б

),

параллельных полосок с металлическими перемычками (рис.

12.6,

в

) либо меандра (рис. 12.6,

г

). Большим сопротивлением

(до 10 кОм/

É) обладают тонкие пленки резистивных сплавов,

например кремния и хрома в различных процентных соотноше-

ниях. Тонкопленочные резисторы применяются не только в ги-

бридных, но и в некоторых полупроводниковых микросхемах.

3

1

3

1

3

1

3

1

а

б

в

г

2

Рис. 12.6 — Структура резистора при гибридной технологии

Резистивный слой в них наносят непосредственно на по-

верхность нелегированной подложки.

12.3

Конденсаторы

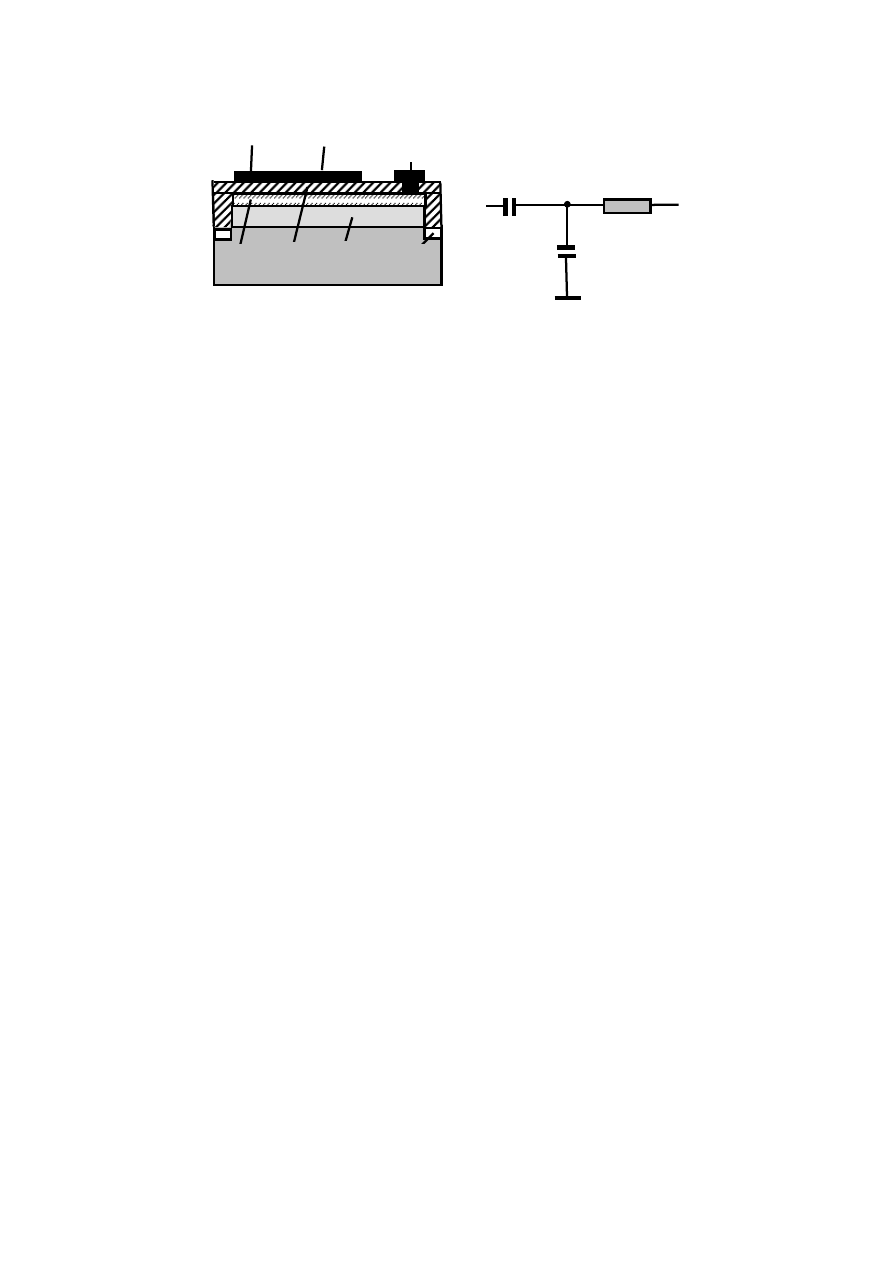

На рис. 12.7,

а

показана структура МДП-конденсатора. Од-

ной из обкладок является

n

+

-слой 1 толщиной 0,3...1 мкм, другой

слой металла (алюминия) — 2, а диэлектриком — слой 3 диокси-

да кремния. Такой конденсатор применяют в полупроводниковых

микросхемах.

118

При незначительном усложнении технологического процес-

са требуются дополнительные операции литографии и окисления

для создания слоя 3. Слой 1 формируется с помощью той же опе-

рации легирования, что и эмиттеры биполярных транзисторов

или истоки и стоки n-канальных МДП-транзисторов. Топологи-

ческая конфигурация конденсатора — квадратная или прямо-

угольная. Для увеличения удельной емкости толщина d слоя 3

выбирается минимально возможной исходя из условия отсут-

ствия пробоя:

ПРОБ

ПРОБ

U

d

E

≥

, где

ПРОБ

E

— электрическая

прочность слоя 3, т. е. напряжённость поля, при котором начина-

ется пробой (около 600 В/мкм). Поэтому максимальная удельная

ёмкость

0 д

0

0 д

/

ПРОБ

ПРОБ

Е

C

d

U

ε ε

= ε ε

=

.

На рис. 12.7 приведена эквивалентная схема конденсатора,

где

r

— сопротивление слоя 1,

C

пар

— паразитная ёмкость между

слоем 1 и подложкой (барьерная ёмкость изолирующего перехо-

да), которая в 4 — 7 раз меньше полезной ёмкости

С

. Если об-

кладка 1 в схеме не соединена с общей шиной микросхемы,

то высокочастотный сигнал, проходящий через конденсатор,

ослабляется емкостным делителем в 1

ПАР

C

С

+

. Добротность по-

лупроводникового конденсатора на частоте 10 МГц не превыша-

ет 750, на частоте 1 ГГц добротность составляет 0,75.

Поэтому полупроводниковые МДП-конденсаторы неприме-

нимы в СВЧ-диапазоне. В СВЧ-диапазоне используют тонкоплё-

ночные конденсаторы.

В отдельных случаях в качестве конденсаторов в интеграль-

ных схемах на биполярных транзисторах используют барьерные

ёмкости

p-n

переходов. Такие конденсаторы могут работать толь-

ко при одной полярности на переходе. Добротность этих конден-

саторов мала как на низких, так и на высоких частотах.

Низкая добротность и большие размеры, которые конденса-

торы занимают на подложке, практически исключают их изго-

товление по интегральной технологии. Это приводит к некото-

рым схемотехническим трудностям при разработке интегральных

схем, особенно БИС.

119

Al

2

SiO

2

p

+

n

3

1

r

C

C

ПАР

а

б

Рис. 12.7 — Структура интегрального конденсатора (а)

и его эквивалентная схема (б)

Вопросы

для

самопроверки

1.

Технология изготовления полупроводниковых резиcторов.

2.

Методы изоляции при изготовлении резисторов.

3.

Ограничения на величину сопротивления полупроводни-

ковых резисторов.

4.

Недостатки полупроводниковых резисторов.

5.

Плёночные резисторы и технология их изготовления.

6.

Технология интегральных конденсаторов.

120

РЕКОМЕНДУЕМАЯ

ЛИТЕРАТУРА

1.

Агаханян Т. М. Основы транзисторной электроники /

Т. М. Агаханян. — М. : Энергия, 1974. — 265 с.

2.

Аваев Н. А. Основы микроэлектроники / Н. А. Аваев,

Ю. Е. Наумов, В. Т. Фролкин. — М. : Радио и связь, 1991. —

288 с.

3.

Зотов В. Д. Полупроводниковые устройства восприятия

оптической информации / В. Д. Зотов. — М. : Энергия, 1976. —

151 с.

4.

Росадо Л. Физическая электроника и микроэлектроника /

Л. Росадо. — М. : Высшая школа, 1991.— 351 с.

5.

Свечников С. В. Элементы оптоэлектроники / С. В. Свеч-

ников. — М. : Сов. радио, 1971. — 269 с.

6.

Степаненко И. П. Основы теории транзисторов и транзи-

сторных схем / И. П. Степаненко. — М. : Энергия, 1977. — 671 с.

7.

Степаненко И. П. Основы микроэлектроники /

И. П. Степаненко. — М. : Сов. радио, 2001. — 423 c.