ВУЗ: Томский государственный университет систем управления и радиоэлектроники

Категория: Учебное пособие

Дисциплина: Электроника

Добавлен: 23.10.2018

Просмотров: 6047

Скачиваний: 13

106

рассеиваемой мощности на транзисторах, включенных по схемам

1 и 2, больше всего на 1—5 мкВт, что даже для интегральной

технологии несущественно.

Значительно меньшее значение обратных токов эмиттерных

переходов является очень важным, т. к. позволяет работать при

существенно меньших прямых токах, а следовательно, умень-

шить общую потребляемую мощность микросхемы.

Схема 1 обладает самым высоким быстродействием. За счет

глубокой отрицательной обратной связи не происходит накопле-

ния избыточных носителей, а, следовательно, время рассасыва-

ния практически равно нулю, что обеспечивает практически

мгновенное время восстановления обратного сопротивления.

Включение транзистора по схеме 5 нецелесообразно,

т. к. она объединяет всё худшее предыдущих схем.

11.6

Модель

интегрального

биполярного

транзистора

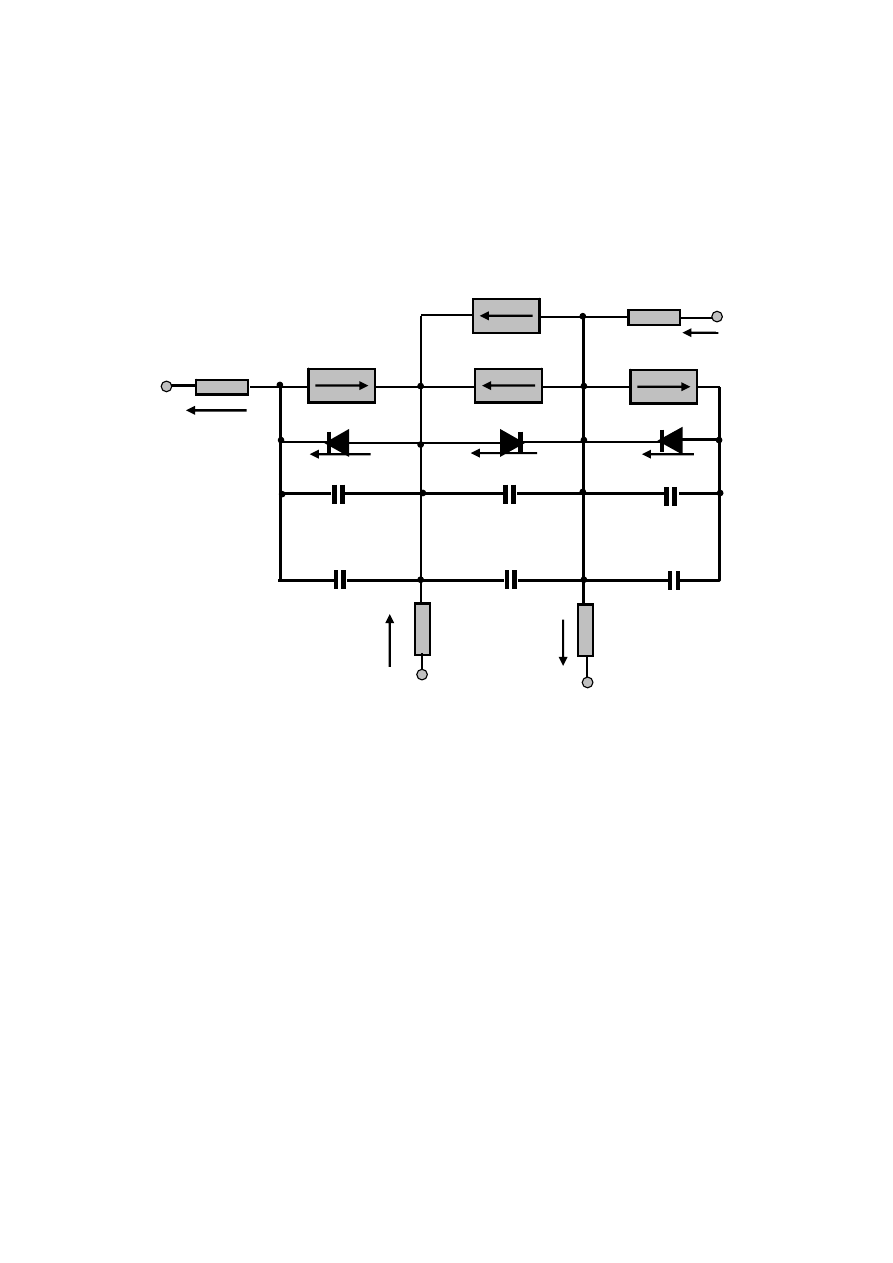

На рис. 11.10 приведена модель интегрального транзистора

типа n-

р

-n, аналогичная модели Эберса — Молла дискретного

транзистора. Она учитывает, что в структуре интегрального тран-

зистора, кроме основного n-

р

-n транзистора, имеется паразитный

р

-n-

р

транзистор. Диоды

1 —

3

VD

VD

— моделируют свойства

эмиттерного, коллекторного и изолирующего

р

-n переходов со-

ответственно.

Вольт-амперные характеристики этих диодов аппроксими-

руются формулами:

1

0

1 ,

БЭ

Т

U

Э

I

I

е

ϕ

⎡

⎤

=

−

⎢

⎥

⎢

⎥

⎣

⎦

2

0

1 ,

кб

Т

U

K

I

I

e

ϕ

⎡

⎤

=

−

⎢

⎥

⎢

⎥

⎣

⎦

3

0

1 ,

КП

T

U

И

I

I

e

ϕ

⎡

⎤

=

−

⎢

⎥

⎢

⎥

⎣

⎦

где

0

Э

I

,

0

K

I

,

0

И

I

— параметры модели, имеющие смысл тепло-

вых обратных токов эмиттерного, коллекторного и изолирующе-

го переходов. Положительными считаются токи I

1

, I

2

, I

3

, соответ-

ствующие прямым включениям переходов. Положительные

направления токов во внешних выводах эмиттера, базы, коллек-

тора и подложки показаны стрелками на рис. 11.10. Эти токи

совпадают с направлениями токов в активном режиме как для ос-

новного, так и для паразитного транзисторов. Напряжения между

107

внешними выводами эмиттер — база

ЭБ

U

, коллектор — база

КБ

U

,

коллектор — подложка

КП

U

и напряжения на

р

-n переходах

1

ЭБ

U

,

1

КБ

U

,

1

КБ

U

считаются положительными, если соответствующий

переход включен в прямом направлении.

ά

1

I

2

ά

П1

I

3

ά

n

I

1

ά

П

I

2

I

К

r

1

Э

r

1

K

r

1

П

r

1

Б

I

Б

I

П

I

1

I

Э2

I

Э3

VD1

VD2

VD3

П

Б

Э

К

I

Э

С

Э бар

С

К бар

С

П бар

С

Э Д

С

К Д

С

П Д

Рис. 11.10 — Модель биполярного интегрального транзистора

Взаимодействие переходов транзистора учитывается че-

тырьмя генераторами тока. Генератор тока

1

n

I

α , включенный па-

раллельно диоду

2

VD

, учитывает передачу тока из эмиттера в

коллектор, а генератор тока

3

Пi

I

α

— из подложки в коллектор.

Здесь

Пi

α — инверсный коэффициент передачи паразитного

р

-n-

р

транзистора, а генератор тока

ПN

α , включенный параллель-

но диоду

3

VD

, из базы в подложку (

ПN

α — нормальный коэффи-

циент передачи паразитного транзистора). Статические парамет-

ры модели — тепловые обратные токи переходов и коэффициен-

ты передачи тока связаны между собой двумя соотношениями:

0

N Э

i

I

I

α

= α ,

0

1

0

П К

П

И

I

I

α

= α

.

108

Таким образом, из семи перечисленных параметров незави-

симыми являются пять. Модель интегрального биполярного

транзистора содержит четыре резистора:

1

э

r

,

1

Б

r

,

1

K

r

,

1

П

r

, учитыва-

ющих влияние сопротивлений полупроводниковых областей

эмиттера, базы, коллектора и подложки соответственно.

Сопротивления перечисленных резисторов являются пара-

метрами модели. Модель включает также барьерные и диффузион-

ные емкости переходов: эмиттерного

ЭБАР

C

,

ЭД

С

, коллекторного

КБАР

С

,

КД

С

и изолирующего

BБАР

C

,

ИД

С

, что позволяет использо-

вать ее для анализа работы транзистора в импульсном режиме.

МДП-транзисторы интегральных микросхем

В микросхемах наиболее широко распространены МДП-

транзисторы с индуцированными каналами n-типа. Транзисторы

со встроенными каналами используют реже, в основном как пас-

сивные элементы (нелинейные резисторы).

11.7

Полевые

транзисторы

с

управляющим

переходом

металл

-

полупроводник

Полевые транзисторы с управляющим переходом металл-

полупроводник являются основными активными элементами ар-

сенид галлиевых микросхем. Главная цель их разработки состоя-

ла в повышении быстродействия. Цифровые арсенид-галлиевые

микросхемы относятся к классу сверхскоростных, которые при-

меняются для работы в диапазоне сверхвысоких частот.

При разработке полевых транзисторов с управляющим пе-

реходом металл-полупроводник и микросхем на их основе ис-

пользуются следующие преимущества арсенида галлия по срав-

нению с кремнием: более высокие подвижность электронов

в слабых электрических полях и скорость насыщения в сильных

полях, большая ширина запрещенной зоны и, как следствие, зна-

чительно более высокое удельное сопротивление нелегированно-

го арсенида галлия, позволяющее создавать полуизолирующие

подложки микросхемы.

109

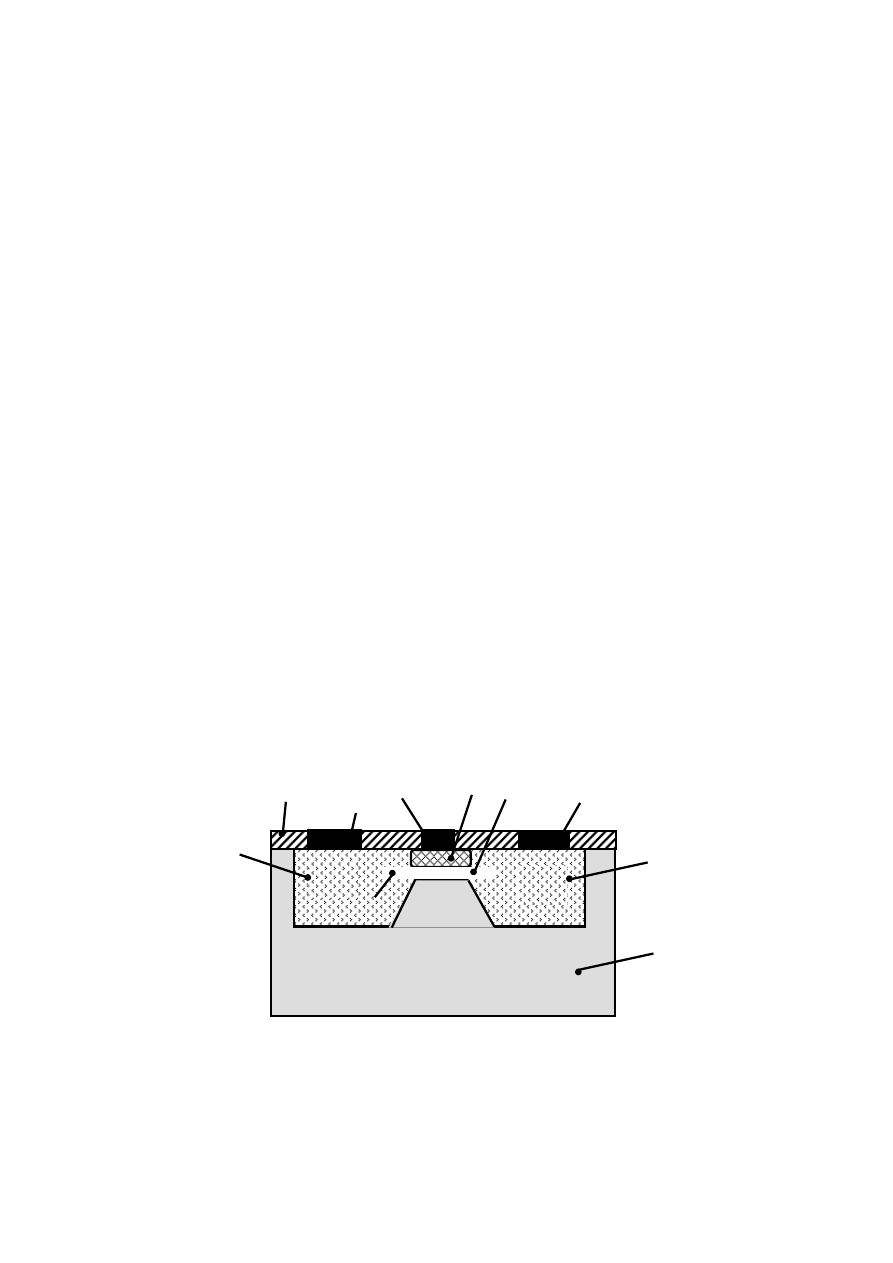

Простейшая структура МЕП-транзистора

Одна из первых структур арсенид-галлиевого МЕП-тран-

зистора (поперечный разрез) показана на рис. 11.11. Транзистор

создают на подложке 1 из нелегированного арсенида галлия.

Нелегированный арсенид галлия имеет слабо выраженную про-

водимость p-типа. Для ее уменьшения при выращивании моно-

кристаллов иногда вводят в небольших количествах атомы хрома,

компенсирующие действие акцепторов. Подложки, изготовлен-

ные из такого материала, обладают повышенным удельным со-

противлением, и их называют полуизолирующими.

У поверхности подложки методом ионного легирования фор-

мируют сильнолегированные области истока и стока

n

+

-типа,

а затем — тонкий слой канала n -типа. На поверхность подложки

над слоем 3 наносят металлический электрод 4 затвора З. Метал-

лические электроды 5, для которых применяют композицию зо-

лото-германий, обеспечивают омические контакты к областям

истокам и стока С. На поверхность подложки, не используемую

для контактов, наносят слой диэлектрика 6, например диоксида

кремния. Металлический электрод затвора образует со слоем 3

выпрямляющий контакт — барьер Шотки, типичная равновесная

высота которого 0,8 В. Проводящий канал между истоком и сто-

ком располагается в слое 3 и ограничен сверху обедненной обла-

стью 7 барьера Шотки, а снизу — подложкой.

И

1

2

2

3

4

5

6

7

Полуизолирующий GaAs

n

+

n

+

З

С

n

5

Рис. 11.11 — Структура МЕП-транзистора

110

U

ПОР1

U

ПОР2

U

ЗИ

U

ЗИ МАКС

I

C МАКС2

I

C МАКС1

I

1

3

2

Рис. 11.12 — Сток-затворные характеристики

МЕП-транзистора

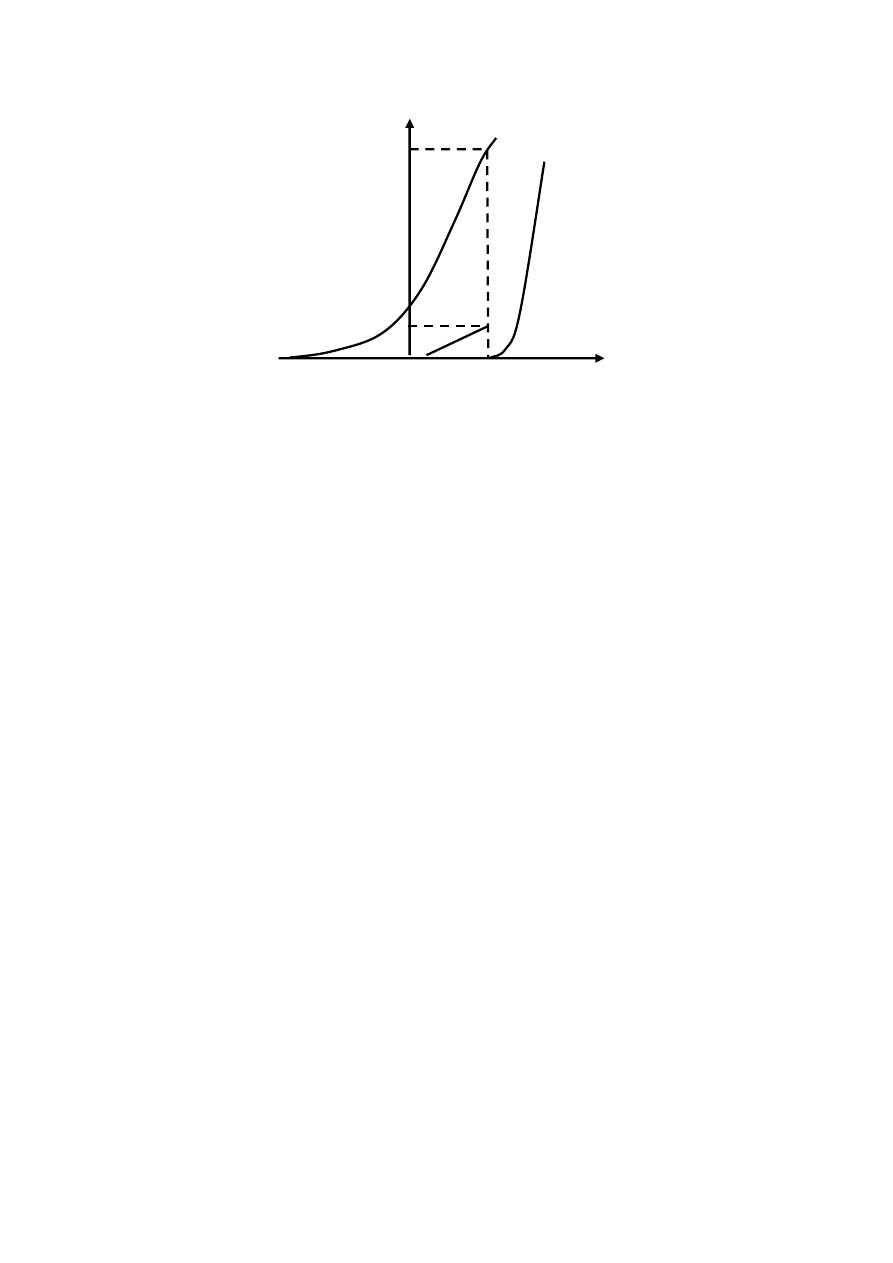

Если напряжение на затворе равно пороговому

1

ПОР

U

, то

граница обедненного слоя 7 достигает полуизолирующей под-

ложки (толщина канала и ток стока равны нулю). Требуемое по-

роговое напряжение обеспечивают выбором концентрации доно-

ров в канале и толщины

0

d

слоя 3.

В арсенид-галлиевых микросхемах применяют МЕП-транзи-

сторы, для которых

2,5 — 0, 2

ПОР

U

B

= −

+

. Если

0

ПОР

U

< , то при

0

ЗИ

U

= канал является проводящим и транзистор называют нор-

мально открытым — он аналогичен МДП-транзистору с встроен-

ным каналом. При

0

ПОР

U

> и

0

ЗИ

U

= канал перекрыт обеднен-

ным слоем 7 и транзистор называют нормально закрытым, он

аналогичен МДП-транзистору с индуцированным каналом. На

рис. 11.12 приведены стоко-затворные характеристики нормально

открытого 1 и нормально закрытого 2 транзисторов, а также их

входная характеристика 3. Для нормально открытых МЕП-

транзисторов управляющее напряжение затвора, при котором

протекает ток стока, может изменяться от отрицательных значе-

ний, превышающих пороговое, до небольших положительных (не

более 0,6

В

). При больших положительных напряжениях на за-

творе в его цепи появляется нежелательный ток

З

I

, так как от-

крывается переход металл-полупроводник (кривая 3). Поэтому

ток стока ограничен величиной

.

1

С макс

I

. Для нормально закрытых

транзисторов напряжение затвора, при котором протекает ток

стока, положительное и может изменяться в пределах 0—0,6.