ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 06.11.2023

Просмотров: 38

Скачиваний: 3

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

СОДЕРЖАНИЕ

СТРУКТУРНАЯ МОДЕЛЬ НЕЧЕТКОГО КОНТРОЛЛЕРА

Операции над нечеткими множествами

МОДЕЛИРОВАНИЕ ЗАДАЧИ РАЗГОНА ОРУДИЯ НА ТРАКТОРЕ «БЕЛАРУС»

СТРУКТУРА НЕЧЕТКОГО КОНТРОЛЛЕРА

- возможность изменения количества входных переменных;

- возможность изменения количества выходных переменных;

- масштабирования входного и выходного сигнала.

Последний фактор обеспечивается внесением в схему блока масштабирования.

Общая структурная схема нечеткого контроллера представлена на рис. 1.

Общая структурная схема нечеткого контроллера.

Наилучшие результаты были получены при использовании пропорционально-интегрального регулятора и нечеткого контроллера с учетом скачка гистерезиса (наименьший выброс момента после разгона орудия).

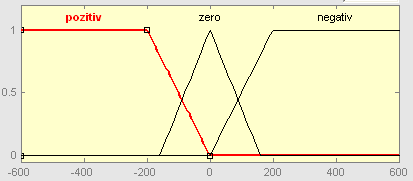

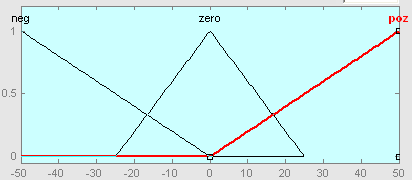

Для построения нечеткого контроллера были выбраны следующие графики функций принадлежности:

Для входной переменной

Для выходной переменной

База правил имеет следующий вид:

Если отклонение реального ускорения буксования от заданного положительная величина, то изменение %ШИМ отрицательное;

Если отклонение реального ускорения буксования от заданного величина близкая к нулю, то изменение %ШИМ близкое к нулю;

Если отклонение реального ускорения буксования от заданного отрицательная величина, то изменение %ШИМ положительное;

СТРУКТУРА НЕЧЕТКОГО КОНТРОЛЛЕРА

При проектировании структурной схемы основное внимание было уделено созданию универсального нечеткого контроллера. Основными факторами универсальности и гибкости контроллера являются:- возможность изменения количества входных переменных;

- возможность изменения количества выходных переменных;

- масштабирования входного и выходного сигнала.

Первые два фактора обеспечиваются наличием отдельного блока для вычисления функций каждой входной переменной и возможность наращивания при необходимости входов и выходов блока активизации правил и блока фаззификации.Последний фактор обеспечивается внесением в схему блока масштабирования.

Общая структурная схема нечеткого контроллера представлена на рис. 1.

рис. 1 Общая структурная схема

Общая структурная схема нечеткого контроллера.

В ее состав входят следующие блоки:

1.MB - Блок масштабирования(позиционирует и уменьшает/увеличивает сигнал). Предназначен для адаптированию входных и выходных сигналов к нужному диапазону значений. Коэффициенты масштабирования задаются для каждого блока масштабирования отдельно. Данный блок делает систему более универсальной.

2.F - Блок вычисления функций принадлежности(вычисляет по входному значению значение функции принадлежности). Данный блок предназначен для вычисления первой фазы нечеткого вывода.

3.RB - Блок реализации правил(активизирует соответствующие выходные правила). Данный блок на основании правил и полученных данных от блока вычисления функций активизирует соответствующие выходные правила.

4.AB - Блок объединения площадей. Данный блок объединяет площади функции принадлежности выходных переменных в соответствии с правилами.

5.FB - Блок генерации выходных сигналов(генерирует результат в зависимости от метода дефаззификации).

X[1..n], Y[1..m] – входной/выходной вектор.

MP[] – вектор коэффициентов масштабирования.

P[] – вектор правил.

F – тип функции, вычисляющей выходной вектор.

sum

sub

mul

div

shift

X

Y

SS

KOEF

MD

KOEF

SHIFT

LR

рис.2 Блок масштабирования

На рис.2 представлена структурная схема блока масштабирования, в ее состав входят блоки математических функций для получения из исходного сигнала сигнал, приемлемый для обработки на последующем шаге.

Блок sum представляет собой сумматор(SS – сигнал выбора сумматора/вычитателя, KOEF – коэффициент сложения/вычиния). Блок sub представляет собой вычитатель. Блок mul представляет собой умножитель. (MD – сигнал выбора умножителя/делителя, KOEF – коэффициент умножения/деления) Блок div представляет собой делитель. Блок shift представляет собой блок сдвига. X, Y – входной/выходной сигнал.

DC

min

max

algp

algs

drastp

drasts

MUX

MUX

MUX

MUX

TYPE

TYPE

A B S/M

S/M

Y

рис.3 Блок реализации правил

Блок реализации правил.

На рис.3 представлен блок реализации правил, который в зависимости от входных параметров вычисляет степень истинности условий по каждому из правил системы нечеткого вывода.

Сигнал S/M выбирает тип операции над подусловиями правила («И» или «ИЛИ»). Блок DC представляет собой декодер реализации выбранной операции, которую необходимо выполнить с подусловиями правила, т.к. в нечетком выводе возможны различные варианты выполнения операций «И», «ИЛИ».С помощью мультиплексоров на выход выводится результат вычисления необходимой функции. Функции в блоках min, max, algp, algps, drastp, drasts реализуют различные виды операций и/или в рамках нечеткой логики.

Следующий код демонстрирует реализацию данного блока на vhdl:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declarations that are

-- provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity ruleblock is

port(

--tup: in std_logic_vector(1 downto 0);

mul: in std_logic;

clk : in std_logic;

code: in std_logic_vector(1 downto 0);

a,b : in integer;

y : out integer

);

end ruleblock;

architecture Behavioral of ruleblock is

component ttrig is

port(

input: in std_logic;

output: out std_logic

);

end component;

component mux21 is

port(

en : in std_logic;

clk: in std_logic;

a,b: in integer;

y: out integer

);

end component;

component algproizv is

port(

clk : in std_logic;

a,b: in integer;

mul, en : in std_logic;

y: out integer

);

end component;

component algsumm is

port(

clk : in std_logic;

a,b: in integer;

mul, en : in std_logic;

y: out integer

);

end component;

component drastproiz is

port(

clk : in std_logic;

a,b: in integer;

mul, en : in std_logic;

y: out integer

);

end component;

component drastsumm is

port(

clk : in std_logic;

a,b: in integer;

mul, en : in std_logic;

y: out integer

);

end component;

component granproiz is

port(

clk : in std_logic;

a,b: in integer;

mul, en : in std_logic;

y: out integer

);

end component;

component gransumm is

port(

clk : in std_logic;

a,b: in integer;

mul, en : in std_logic;

y: out integer

);

end component;

component max is

port(

clk : in std_logic;

a,b: in integer;

mul, en : in std_logic;

y: out integer

);

end component;

component min is

port(

clk : in std_logic;

a,b: in integer;

mul, en : in std_logic;

y: out integer

);

end component;

component mux4 is

port(

clk : in std_logic;

input0,input1,input2,input3 : in integer;

sel : in std_logic_vector(1 downto 0);

output : out integer

);

end component;

component decoder2

port(

code : in std_logic_vector(1 downto 0);

clk : in std_logic;

encode : out std_logic_vector(3 downto 0)

);

end component;

signal encode : std_logic_vector(3 downto 0);

signal y1,y2,y3,y4,y5,y6,y7,y8: integer;

signal yy1,yy2,yy3,yy4: integer;

signal clk2: std_logic;

begin

decoder21 : decoder2

port map(code=>code,clk=>clk,encode=>encode);

clk21 : ttrig

port map(input=>clk, output=>clk2);

min1 : min

port map(clk=>clk,a=>a,b=>b,mul=>mul,en=>encode(0),y=>y1);

max1 : max

port map(clk=>clk,a=>a,b=>b,mul=>mul,en=>encode(0),y=>y2);

algpro : algproizv

port map(clk=>clk,a=>a,b=>b,mul=>mul,en=>encode(1),y=>y3);

algs : algsumm

port map(clk=>clk,a=>a,b=>b,mul=>mul,en=>encode(1),y=>y4);

granp : granproiz

port map(clk=>clk,a=>a,b=>b,mul=>mul,en=>encode(2),y=>y5);

grans : gransumm

port map(clk=>clk,a=>a,b=>b,mul=>mul,en=>encode(2),y=>y6);

drastp : drastproiz

port map(clk=>clk,a=>a,b=>b,mul=>mul,en=>encode(3),y=>y7);

drasts : drastsumm

port map(clk=>clk,a=>a,b=>b,mul=>mul,en=>encode(3),y=>y8);

mux1: mux21

port map(en=>mul,clk=>clk2,a=>y1,b=>y2,y=>yy1);

mux2: mux21

port map(en=>mul,clk=>clk2,a=>y3,b=>y4,y=>yy2);

mux3: mux21

port map(en=>mul,clk=>clk2,a=>y5,b=>y6,y=>yy3);

mux41: mux21

port map(en=>mul,clk=>clk2,a=>y7,b=>y8,y=>yy4);

mux5 : mux4

port map(clk=>clk,input0=>yy1,input1=>yy2,input2=>yy3,input3=>yy4,sel=>code,output=>y );

end Behavioral;

рис.4 Блок вычисления значения функции принадлежности

рис.4 Блок вычисления значения функции принадлежностиБлок вычисления функций принадлежности.

На рис.4 представлен блок вычисления функций принадлежности, который в зависимости от входных параметров вычисляет значение функции принадлежности заданного вида. input, output – входное/выходное значение. type – тип функции принадлежности. P – различные коэффициенты функций принадлежностию. Реализация данного блока возможна в двух вариантах:

-

При использовании для каждой функции своей аппаратной схемы взависимости от типа функции. Недостатком такого подхода является сложность схемы и разное время вычисления для разных типов функции. Преимуществом является малые аппаратные затраты. -

При использовании табличного метода. В этом случае используется ПЗУ, адрес в котором – входной аргумент функции, а значение по этому адресу – выходное значение функции. Преимуществом является простота реализации, скорость выполнения и одинаковое время вычисления для разных типов функции. Недостатком является большие аппаратные затраты.

ЗАКЛЮЧЕНИЕ

В данной работе была разработана структурная схема и реализация на vhdl отдельных фрагментов нечеткого контроллера. Так же было проведено программное моделирование системы средствами matlab. Была сделана попытка создать наиболее универсальную структуру нечеткого контроллера для обеспечения гибкости и расширения круга решаемых задач.

В перспективе планируется полная реализация контроллера на vhdl, тестирование и внедрение.

ЛИТЕРАТУРА

-

Алиев Р.А., Абдикеев Н.М., Шахназаров М.М. Производственные системы с искусственным интеллектом.- М: Радио и связь. 1990. - 264 с. -

Алтунин А.Е., Семухин М.В. Модели и алгоритмы принятия решений в нечетких условиях. Тюмень: Изд-во Тюменского государственного университета, 2000. - 352 с. -

Архангельский В.И., Богаенко И.Н., Грабовский Г.Г., Рюмшин Н.А. Системы фуцци-управления. – К.: Тэхника, 1997. – 208 с. -

Беллман Р., Заде Л. Принятие решений в расплывчатых условиях.- В кн.: Вопросы анализа и процедуры принятия решений.- М.:Мир, 1976. - С. 172-215. -

Берштейн Л.С., Боженюк А.В. Нечеткие модели принятия решений: дедукция, индукция, аналогия. Таганрог: Изд-во ТРТУ, 2001. - 110 с.