Файл: Лабораторная работа 3 (Симулятор ПЛК Omron ZEN-10C1AR-A).pdf

ВУЗ: Пермский национальный исследовательский политехнический университет

Категория: Методичка

Дисциплина: Системы реального времени

Добавлен: 15.11.2018

Просмотров: 3348

Скачиваний: 41

26

иметь значение логического 0 и неактивным – если I0 будет иметь значение логической

1

. В таблице 3 приведены результаты второго теста.

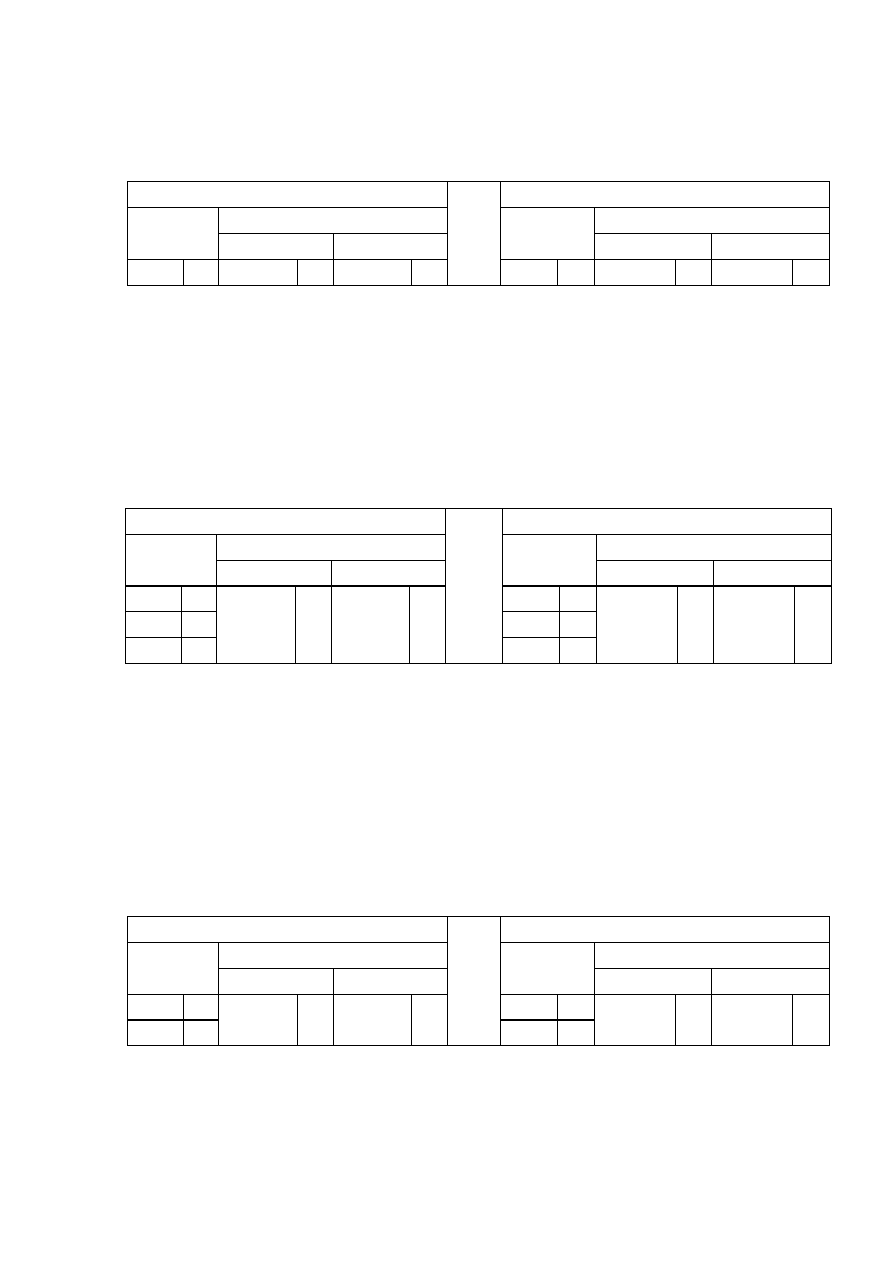

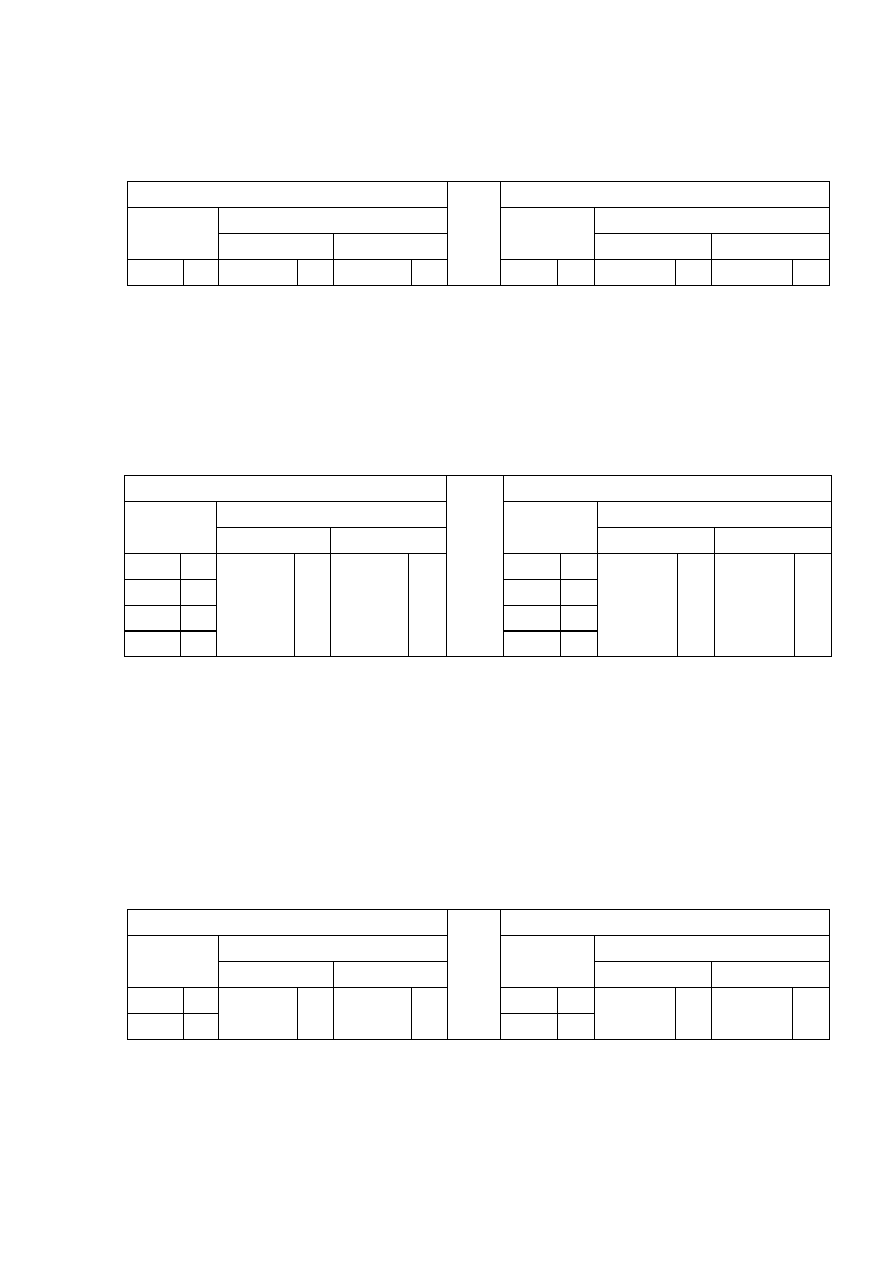

Таблица 3 – Результаты второго теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

0

Q0

1

Q0

1

I0

1

Q0

0

Q0

0

Б) Проверка смешанного подключения. Схема состоит из нормально разомкнутых

входов I0 и I2, подключённых параллельно, нормального замкнутого входа I1,

подключённого последовательно I0 и I2 и выхода Q0. Выход Q0 будет активен в случае

подачи на входы I0 или I2 логической 1 и при отсутствии сигнала на I1. В таблице 4

приведены результаты пятого теста.

Таблица 4 – Результаты пятого теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

0

Q0

0

I0

1

Q0

1

Q0

1

I1

1

I1

0

I2

1

I2

0

7.3 Вариант 3

А) Проверка последовательного подключения. Схема состоит из нормально

разомкнутого входа I0, нормально разомкнутого входа I1, подключённых

последовательно, и выхода Q0. Выход Q0 будет активен, если I1 и I2 будут находиться в

состоянии логической единицы. В таблице 5 приведены результаты третьего теста.

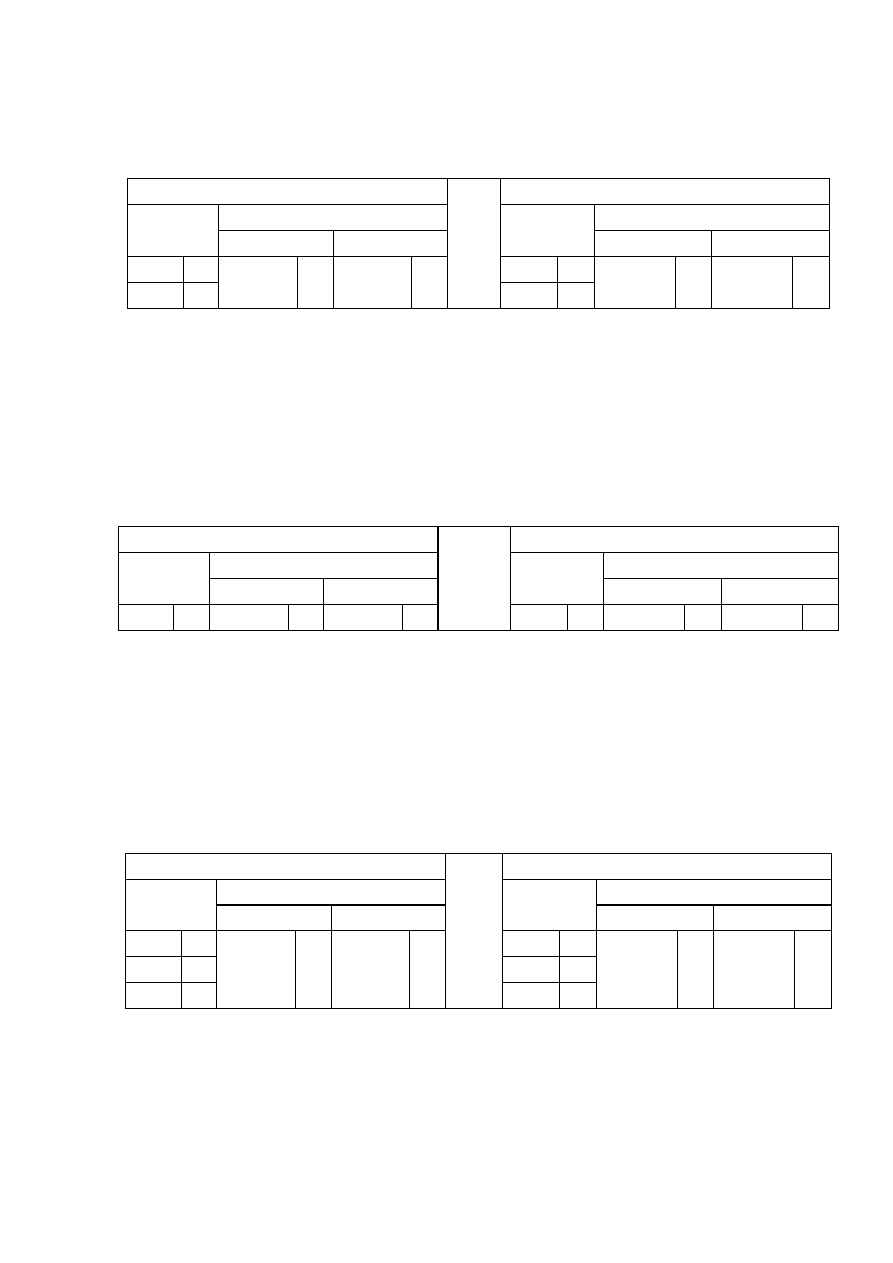

Таблица 5 – Результаты третьего теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

1

Q0

1

I0

1

Q0

0

Q0

0

I1

1

I1

0

Б) Проверка параллельного подключения. Схема состоит из нормально

разомкнутого входа I0, нормально разомкнутого входа I, подключённых параллельно, и

выхода Q0. Выход Q0 будет активен, если I0 или I1 будет находиться в состоянии

27

логической единицы (или оба входа будут активными). В таблице 6 приведены результаты

четвёртого теста.

Таблица 6 – Результаты четвёртого теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

1

Q0

1

I0

1

Q0

1

Q0

1

I1

1

I1

0

7.4 Вариант 4

А) Проверка включения нормально разомкнутого контакта. Схема состоит из

нормально разомкнутого входа I0 и выхода Q0. При подаче сигнала на вход выход

должен становиться активным. В таблице 7 приведены результаты теста.

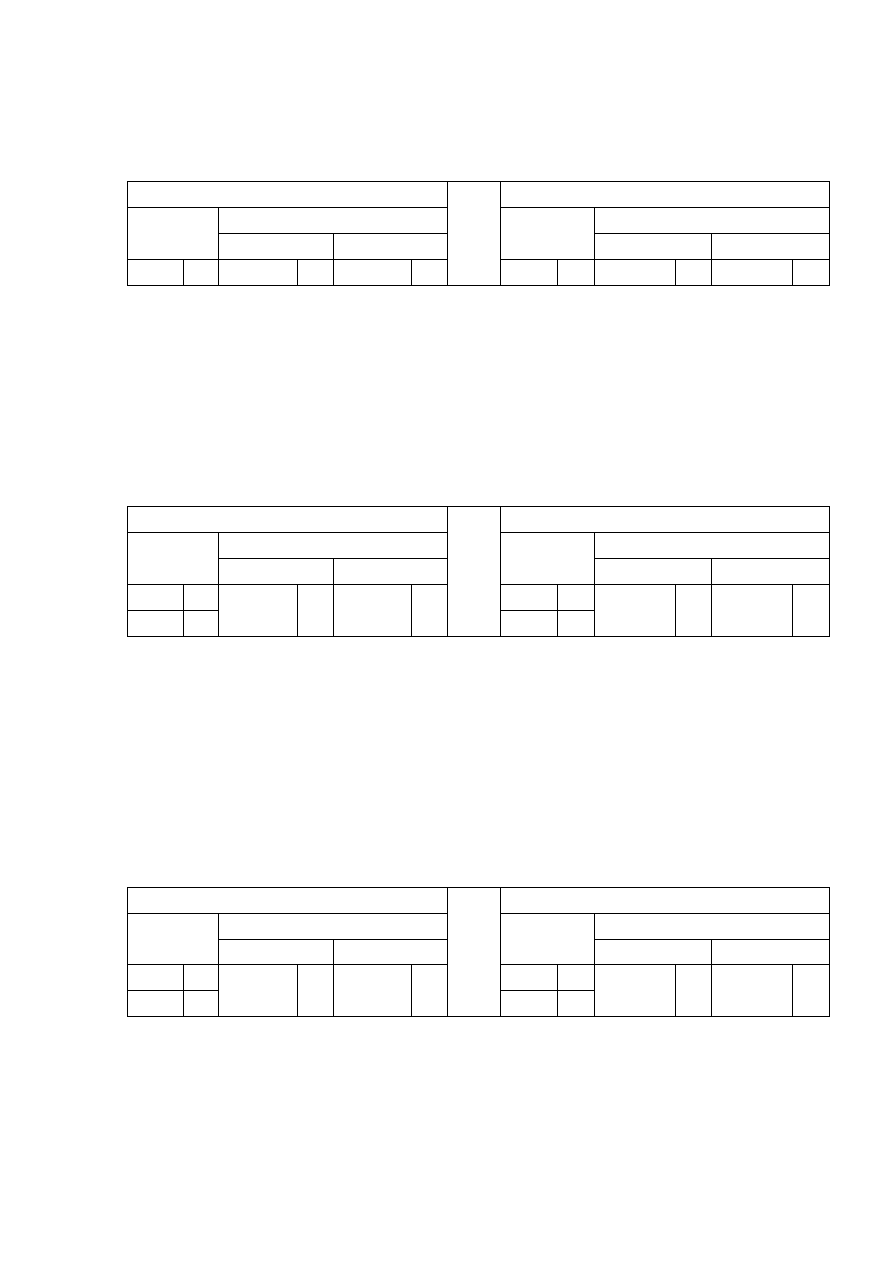

Таблица 7 – Результаты первого теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

1

Q0

1

I0

0

Q0

0

Q0

0

Б) Проверка смешанного подключения. Схема состоит из нормально разомкнутых

входов I0 и I2, подключённых параллельно, нормального замкнутого входа I1,

подключённого последовательно I0 и I2 и выхода Q0. Выход Q0 будет активен в случае

подачи на входы I0 или I2 логической 1 и при отсутствии сигнала на I1. В таблице 8

приведены результаты пятого теста.

Таблица 8 – Результаты пятого теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

0

Q0

0

I0

1

Q0

1

Q0

1

I1

1

I1

0

I2

1

I2

0

7.5 Вариант 5

А) Проверка включения нормально замкнутого контакта. Схема состоит из

нормально замкнутого входа I0 и выхода Q0. Выход Q0 будет активным если I0 будет

28

иметь значение логического 0 и неактивным – если I0 будет иметь значение логической

1

. В таблице 9 приведены результаты второго теста.

Таблица 9 – Результаты второго теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

0

Q0

1

Q0

1

I0

1

Q0

0

Q0

0

Б) Проверка параллельного подключения. Схема состоит из нормально

разомкнутого входа I0, нормально разомкнутого входа I, подключённых параллельно, и

выхода Q0. Выход Q0 будет активен, если I0 или I1 будет находиться в состоянии

логической единицы (или оба входа будут активными). В таблице 10 приведены

результаты четвёртого теста.

Таблица 10 – Результаты четвёртого теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

1

Q0

1

I0

1

Q0

1

Q0

1

I1

1

I1

0

7.6 Вариант 6

А) Проверка последовательного подключения. Схема состоит из нормально

разомкнутого входа I0, нормально разомкнутого входа I1, подключённых

последовательно, и выхода Q0. Выход Q0 будет активен, если I1 и I2 будут находиться в

состоянии логической единицы. В таблице 11 приведены результаты третьего теста.

Таблица 11 – Результаты третьего теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

1

Q0

1

I0

1

Q0

0

Q0

0

I1

1

I1

0

Б) Проверка смешанного подключения. Схема состоит из последовательно

соединенных элементов I1 с параллельно соединенными элементами I2, I3 и далее

последовательно I4. Q3=1, если I1 и I4 является активным и один из входов I2, I3 (или

оба) является неактивным. Результаты обоих тестов представлены в таблице 12.

29

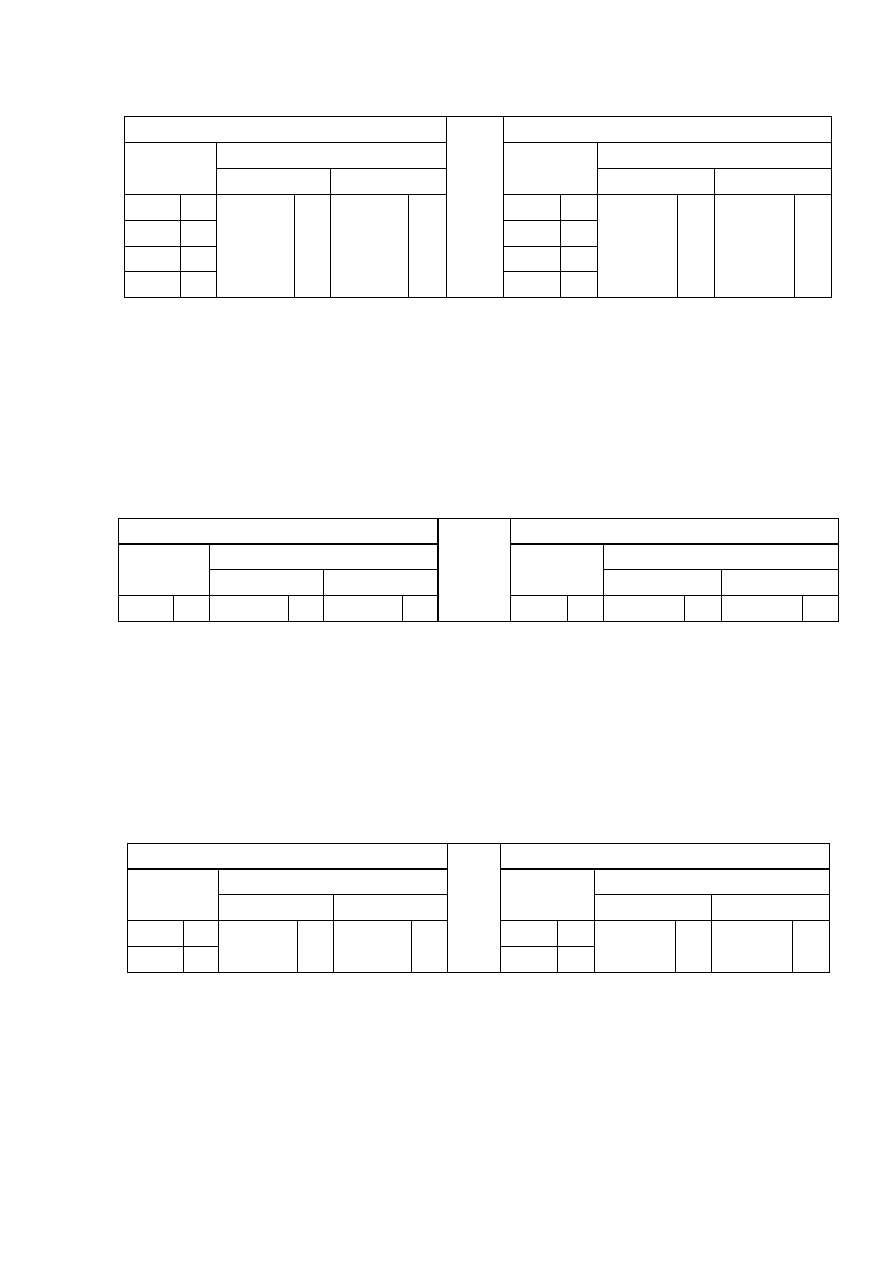

Таблица 12 – Результаты восьмого теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I1

1

Q2

1

Q2

1

I1

1

Q2

0

Q2

0

I2

0

I2

1

I3

1

I3

1

I4

1

I4

1

7.7 Вариант 7

А) Проверка включения нормально разомкнутого контакта. Схема состоит из

нормально разомкнутого входа I0 и выхода Q0. При подаче сигнала на вход выход

должен становиться активным. В таблице 13 приведены результаты теста.

Таблица 13 – Результаты первого теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

1

Q0

1

I0

0

Q0

0

Q0

0

Б) Проверка параллельного подключения. Схема состоит из нормально

разомкнутого входа I0, нормально разомкнутого входа I, подключённых параллельно, и

выхода Q0. Выход Q0 будет активен, если I0 или I1 будет находиться в состоянии

логической единицы (или оба входа будут активными). В таблице 14 приведены

результаты четвёртого теста.

Таблица 14 – Результаты четвёртого теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

1

Q0

1

I0

1

Q0

1

Q0

1

I1

1

I1

0

7.8 Вариант 8

А) Проверка включения нормально замкнутого контакта. Схема состоит из

нормально замкнутого входа I0 и выхода Q0. Выход Q0 будет активным если I0 будет

30

иметь значение логического 0 и неактивным – если I0 будет иметь значение логической

1

. В таблице 15 приведены результаты второго теста.

Таблица 15 – Результаты второго теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

0

Q0

1

Q0

1

I0

1

Q0

0

Q0

0

Б) Проверка смешанного подключения. Схема состоит из последовательно

соединенных элементов I1 с параллельно соединенными элементами I2, I3 и далее

последовательно I4. Q3=1, если I1 и I4 является активным и один из входов I2, I3 (или

оба) является неактивным. Результаты обоих тестов представлены в таблице 16.

Таблица 16 – Результаты восьмого теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I1

1

Q2

1

Q2

1

I1

1

Q2

0

Q2

0

I2

0

I2

1

I3

1

I3

1

I4

1

I4

1

7.9 Вариант 9

А) Проверка последовательного подключения. Схема состоит из нормально

разомкнутого входа I0, нормально разомкнутого входа I1, подключённых

последовательно, и выхода Q0. Выход Q0 будет активен, если I1 и I2 будут находиться в

состоянии логической единицы. В таблице 17 приведены результаты третьего теста.

Таблица 17 – Результаты третьего теста

Входной набор 1

Входной набор 2

Входы

Выходы

Входы

Выходы

Ожидаемое Полученное

Ожидаемое Полученное

I0

1

Q0

1

Q0

1

I0

1

Q0

0

Q0

0

I1

1

I1

0

Б) Проверка смешанного подключения. Схема состоит из нормально разомкнутых

входов I0 и I2, подключённых параллельно, нормального замкнутого входа I1,

подключённого последовательно I0 и I2 и выхода Q0. Выход Q0 будет активен в случае