Файл: Архитектура аппаратных средств. Контрольная работа. Титульный лист Содержание.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 26.10.2023

Просмотров: 34

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Архитектура аппаратных средств. Контрольная работа.

Титульный лист

Содержание

15.Схемные логические элементы: демультиплексор, шифратор 3

16.Устройство управления, арифметико-логическое устройство, микропроцессорная память: назначение, понятие 6

Список используемых источников 11

15.Схемные логические элементы: демультиплексор, шифратор

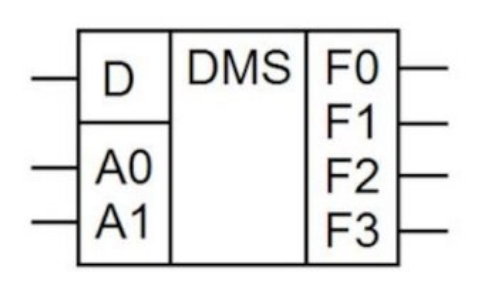

Демультиплексор (Рисунок 1) - устройство, обратное мультиплексору. Т. е., у демультиплексора один вход и много выходов. комбинационное устройство, выполняющие функции, обратные дешифратору. При подаче сигнала на один из его входов (унитарный код) на выходе должен образоваться двоичный код.">Двоичный код определяет, какой выход будет подключен ко входу.

Другими словами, демультиплексор - это устройство, которое осуществляет выборку одного из нескольких своих выходов и подключает его к своему входу или, ещё, это переключатель сигналов, управляемый двоичным кодом и имеющий один вход и несколько выходов.

К входу подключается тот выход, чей номер соответствует состоянию двоичного кода. И частное определение: демультиплексор - это устройство, которое преобразует последовательный код в параллельный.

Обычно в качестве демультиплексора используют дешифраторы двоичного кода в позиционный, в которых вводят дополнительный вход стробирования.

Из-за сходства схем мультиплексора и демультиплексора в КМОП сериях есть микросхемы, которые одновременно являются мультиплексором и демультиплексором, смотря с какой стороны подавать сигналы.

Например, К561КП1, работающая как переключатель 8x1 и переключатель 1x8 (то есть, как мультиплексор и демультиплексор с восемью входами или выходами). Кроме того, в КМОП микросхемах помимо переключения цифровых сигналов (логических 0 или 1) существует возможность переключения аналоговых.

Рисунок 1 – Демультиплексор

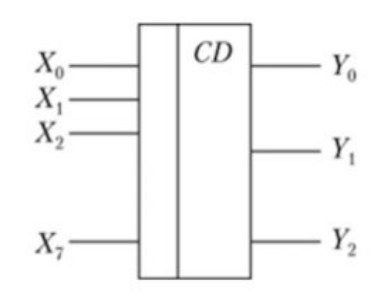

Шифратор (Рисунок 2) — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением п = 2т, где п — число входов, т — число выходов.

Рисунок 2 – Шифратор

16.Устройство управления, арифметико-логическое устройство, микропроцессорная память: назначение, понятие

Устройство управления

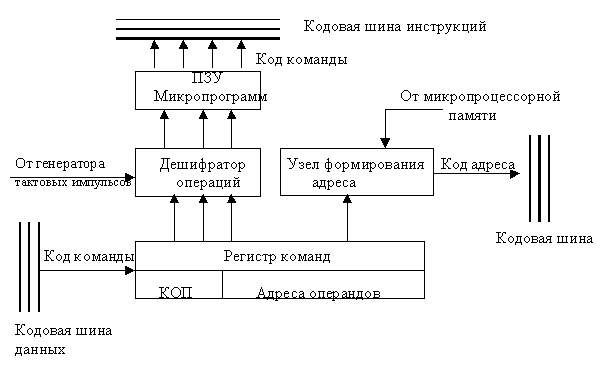

Устройство управления является функционально наиболее сложным устройством ПК. Оно вырабатывает управляющие сигналы, поступающие по кодовым шинам инструкций во все блоки машины.

Упрощенная функциональная схема УУ показана на рис. 3. Здесь представлены:

Регистр команд – запоминающий регистр, в котором хранится код команды: код выполняемой операции и адреса операндов, участвующих в операции. Регистр команд расположен в интерфейсной части МП, в блоке регистров команд.

Дешифратор операций – логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (КОП) один из множества имеющихся у него выходов.

Рисунок 3 – Укрупненная функциональная схема устройства управления

Постоянное запоминающее устройство микропрограмм – хранит в своих ячейках управляющие сигналы (импульсы), необходимые для выполнения в блоках ПК операций обработки информации. Импульс по выбранному дешифратором операций в соответствии с кодом операции считывает из ПЗУ микропрограмм необходимую последовательность управляющих сигналов.

Узел формирования адреса (находится в интерфейсной части МП) – устройство, вычисляющее полный адрес ячейки памяти (регистра) по реквизитам, поступающим из регистра команд и регистров МПП.

Кодовые шины данных, адреса и инструкций – часть внутренней интерфейсной шины микропроцессора. В общем случае УУ формирует управляющие сигналы для выполнения следующих основных процедур:

-

выборки из регистра-счетчика адреса команды МПП адреса ячейки ОЗУ, где хранится очередная команда программы;

-

выборки из ячеек ОЗУ кода очередной команды и приема считанной команды в регистр команд;

-

расшифровки кода операции и признаков выбранной команды;

-

считывания из соответствующих расшифрованному коду операции ячеек ПЗУ микропрограмм управляющих сигналов (импульсов), определяющих во всех блоках машины процедуры выполнения заданной операции, и пересылки управляющих сигналов в эти блоки;

-

считывания из регистра команд и регистров МПП отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирования полных адресов операндов;

-

выборки операндов (по сформированным адресам) и выполнения заданной операции обработки этих операндов;

-

записи результатов операции в память;

-

формирования адреса следующей команды программы.

Арифметико-логическое устройство

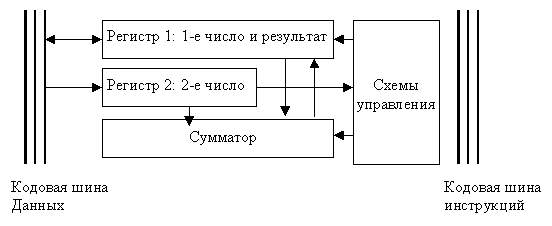

Арифметико-логическое устройство предназначено для выполнения арифметических и логических операций преобразования информации.

Функционально АЛУ (Рисунок 4) состоит обычно из двух регистров, сумматора и схем управления (местного устройства управления).

Рисунок 4 – Функциональная схема АЛУ

Сумматор – вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность двойного машинного слова.

Регистры – быстродействующие ячейки памяти различной длины: регистр 1 (Рг1) имеет разрядность двойного слова, а регистр 2 (Рг2) – разрядность слова.

При выполнении операций в Рг1 помещается первое число, участвующее в операции, а по завершении операции – результат; в Рг2 – второе число, участвующее в операции (по завершении операции информация в нем не изменяется). Регистр 1 может и принимать информацию с кодовых шин данных, н выдавать информацию на них, регистр 2 только получает информацию с этих шин.

Схемы управления принимают по кодовым шинам инструкций управляющие сигналы от устройства управления и преобразуют их в сигналы для управления работой регистров и сумматора АЛУ.

АЛУ выполняет арифметические операции (+, -, ×,:) только над двоичной информацией с запятой, фиксированной после последнего разряда, т.е. только над целыми двоичными числами.

Выполнение операций над двоичными числами с плавающей запятой и над двоично-кодированными десятичными числами осуществляется или с привлечением математического сопроцессора, или по специально составленным программам.

Микропроцессорная память.

Микропроцессорная память – память небольшой емкости, но чрезвычайно высокого быстродействия (время обращения к МПП, т.е. время, необходимое на поиск, запись или считывание информации из этой памяти, измеряется наносекундами – тысячными долями микросекунды).

Она предназначена для кратковременного хранения, записи и выдачи информации, непосредственно в ближайшие такты работы машины участвующей в вычислениях, МПП используется для обеспечения высокого быстродействия машины, ибо основная память не всегда обеспечивает скорость записи, поиска и считывания информации, необходимую для эффективной работы быстродействующего микропроцессора.

Микропроцессорная память состоит из быстродействующих регистров с разрядностью не менее машинного слова. Количество и разрядность регистров в разных микропроцессорах различны: от 14 двухбайтных регистров у МП 8086 до нескольких десятков регистров разной длины у МП Pentium.

Регистры микропроцессора делятся на регистры общего назначения и специальные.

Специальные регистры применяются для хранения различных адресов (адреса команды, например), признаков результатов выполнения операций и режимов работы ПК (регистр флагов, например) и др.

Регистры общего назначения являются универсальными и могут использоваться для хранения любой информации, но некоторые из них тоже должны быть обязательно задействованы при выполнении ряда процедур.

Список используемых источников

1. Аппаратные средства персонального компьютера / С.В. Киселев и др. -М.: Академия, 2017. - 452 с.

2. Архитектура и технологии IBM eServer zSeries / В.А. Варфоломеев и др. - М.: Интернет-университет информационных технологий, 2017. - 640 c.

3. Бройдо, В. Л. Архитектура ЭВМ и систем / В.Л. Бройдо, О.П. Ильина. - М.: Книга по Требованию, 2016. - 720 c.

4. Джон, Л. Хеннесси Компьютерная архитектура. Количественный подход / Джон Л. Хеннесси, Дэвид А. Паттерсон. - Москва: Машиностроение, 2016. - 936 c.