Файл: Перечень ответов на вопросы к промежуточному зачету по дисциплине Организация эвм и вс.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 07.11.2023

Просмотров: 259

Скачиваний: 4

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Символы

ЭВМ способны обрабатывать не только числа, но и текстовую информацию, состоящую из символов.

Под термином символы подразумеваются буквы латинские, греческие, кириллицы, десятичные цифры, знаки препинания, иероглифы, символы математических операций и так далее.

Каждому символу ставится в соответствие определенная двоичная комбинация. Совокупность возможных символов и назначенных им двоичных кодов образует кодовую таблицу.

Наиболее распространенными являются кодовые таблицы, в которых символы кодируются с помощью восьмиразрядных двоичных комбинаций (байтов), позволяющих представить 256 различных символов:

1. Расширенный двоично-кодированный код EBCDIC (Extended Binary Coded Decimal Interchange Code); известный ещё под названием ДКОИ (Двоичный Код для Обработки Информации)

2. Американский стандартный код для обмена информацией ASCII (American Standard Code for Information Interchange).

Стандартный код ASCII – 7-разрядный. В более поздней, европейской модификации ASCII (стандарт ISO 8859-1) используются все 8 разрядов.

Дополнительные комбинации (коды 128-255) в новом варианте отводятся для представления специфических букв алфавитов западноевропейских языков, символов псевдографики, некоторых букв греческого алфавита, а также ряда математических и финансовых символов.

Именно эти кодовые таблицы считаются мировым стандартом де-факто, который в различных модификациях применяется во всех странах.

В зависимости от использования кодов 128-255 различают несколько вариантов стандарта ISO 8859 от ISO 8859-1 до ISO 8859-16.

Логические значения

Элементом логических данных является логическая (булева) переменная, которая принимает значения: «истина» или «ложь».

Единицей кодируют истинное значение, нулем — ложное. Как правило, в ЭВМ оперируют наборами логических переменных длиной в машинное слово.

Обрабатываются такие слова с помощью команд логических операций (И, ИЛИ, НЕ и т. д.), при этом все биты обрабатываются одинаково, но независимо друг от друга, то есть никаких переносов между разрядами не возникает.

30.Основные концепции функционирования ЭВМ. Обобщенная структура процессора

Пересылка данных между памятью и процессором начинается с отправки в устройство памяти адреса слова, к которому требуется получить доступ, и выдачи соответствующих управляющих сигналов. Затем данные пересылаются в память или из памяти.

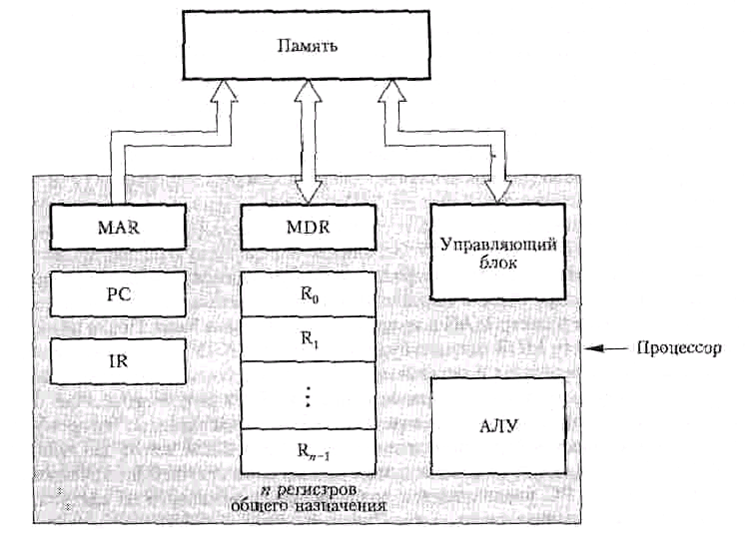

На рис. 3.2 показано, как соединяются между собой память и процессор. Кроме того, рисунок иллюстрирует несколько важных особенностей функционирования процессора, о которых мы с вами еще не говорили. На нем не показана реальная схема соединений этих компонентов, поскольку пока мы обсуждаем только их функциональные характеристики. Более детально соединение компонентов описывается в разделе 8 при рассмотрении конструкции процессора.

Кроме АЛУ и управляющих схем процессор содержит множество регистров, предназначенных для разных целей. В регистре команды (Instruction Register, IR) содержится код выполняемой в данный момент команды. Ее результат доступен управляющим схемам, которые генерируют сигналы для управления различными элементами, участвующими в выполнении команды. Еще один специализированный регистр, называемый счетчиком команд (Program Counter, PC), служит для контроля за ходом выполнения программы. В нем содержится адрес следующей команды, подлежащей выборке и выполнению. Пока выполняется очередная команда, содержимое регистра PC обновляется — в него записывается адрес следующей команды. Говорят, что регистр PC указывает на команду, которая должна быть выбрана из памяти. Кроме регистров IR и PC на рис. 3.2 показано n регистров общего назначения, от R0 до R„-i. Для чего они нужны, объясняется в главе 2.

Наконец, еще два регистра обеспечивают взаимодействие с памятью. Это регистр адреса (Memory Address Register, MAR) и регистр данных (Memory Data Register, MDR). В регистре MAR содержится адрес, по которому производится обращение к памяти, а в регистре MDR — данные, которые должны быть записаны в память или прочитаны из таковой по этому адресу.

Рассмотрим типичный процесс выполнения программы компьютером. Программа располагается в памяти, куда обычно попадает через входное устройство. Ее выполнение начинается с записи в регистр PC адреса первой команды. Содержимое этого регистра пересылается в регистр MAR, а в память направляется управляющий сигнал Read. Когда истекает время, необходимое для доступа к памяти, адресуемое слово (в данном случае — первая команда программы) считывается из памяти и загружается в регистр MDR. Затем содержимое регистра MDR пересылается в регистр IR. Команда готова к декодированию и выполнению.

Если команда требует, чтобы АЛУ выполнило определенную операцию, для нее необходимо получить операнды. Операнд, располагающийся в памяти (он может находиться и в регистре общего назначения), нужно сначала из таковой извлечь, переслав его адрес в регистр MAR и инициализировав цикл Read. После пересылки из памяти в регистр MDR операнд будет направлен в АЛУ. Аналогичным образом туда же будут переданы и остальные необходимые команде операнды, после чего АЛУ сможет выполнить требуемую операцию. Если результат должен быть сохранен в памяти, он будет записан в регистр MDR. Затем адрес, по которому его нужно записать в память, будет помещен в регистр MAR, после чего будет инициирован цикл Write. В какой-то момент в ходе выполнения текущей инструкции содержимое регистра PC увеличивается, и он начинает указывать на следующую подлежащую выполнению инструкцию. Другими словами, как только завершится выполнение текущей инструкции, можно будет приступать к выборке следующей.

Рис. 3.2. Соединения между процессором и памятью

Компьютер не только пересылает данные между памятью и процессором, но и принимает их от входных устройств, а также отсылает выходным устройствам. Поэтому среди машинных команд имеются и команды для выполнения операций ввода-вывода.

Если возникает необходимость срочно обслужить некоторое устройство (например, когда устройство мониторинга в автоматизированном промышленном процессе обнаружит опасную ситуацию), нормальное выполнение программы может быть прервано. Для того чтобы немедленно отреагировать на эту ситуацию, компьютер должен прервать выполнение текущей программы. С этой целью устройство генерирует сигнал прерывания. Прерывание (interrupt) — это запрос, поступающий от устройства ввода-вывода, с требованием предоставить ему процессорное время. Для обслуживания этого устройства процессор выполняет соответствующую программу обработки прерывания. А поскольку ее выполнение может изменить внутреннее состояние процессора, перед обслуживанием прерывания нужно сохранить его состояние в памяти. Обычно в ходе этой операции сохраняется содержимое регистра PC, регистров общего назначения и некоторая управляющая информация. По завершении работы программы обработки прерывания состояние процессора восстанавливается и прерванная программа продолжает свою работу. Процессор со всеми его элементами (рис. 3.2) обычно реализуется в виде одной микросхемы, на которой располагается как минимум одно устройство кэш-памяти. Такие чипы называются VLSI (VLSI — аббревиатура от Very Large Scale Integration, что переводится как очень крупномасштабная интеграция).

31.Цикл процессора (исполнение команды) Последовательность исполнения команды.

(дублирует 5 и 23 вопрос)

32. Процессоры CISC , RISC и их особенности

(Дублирует 2 вопрос, вроде)

Особенности RISC процессоров:

-

Сокращенный набор команд (от 58 до 150 команд); -

Большинство команд выполняется за 1 такт; -

Большое количество регистров общего назначения; -

Наличие жестких многоступенчатых конвейеров; -

Все команды имеют простой формат; -

Наличие вместительной раздельной кэш-памяти; -

Применение оптимизирующих компиляторов, которые анализируют исходный код и частично меняют порядок следования команд.

Особенность CISC процессоров: перенос “центра тяжести” обработки с программного уровня на аппаратный (образно).

33. Процессоры VLIW, MISC и их особенности

Minimum Instruction Set Comand (MISC) – процессор с минимальным набором команд.

Архитектура MISC строится на стековой вычислительной модели с ограниченным числом команд (примерно 20–30 команд).

Принцип простоты, изначальный для RISC - процессоров сохраняется в архитектуре MISC (Minimum Instruction Set Comand), процессор с минимальным набором команд.

Very long instruction word (VLIW) – процессор с очень длинным командным словом — архитектура с несколькими АЛУ.

В одной инструкции процессора задаётся несколько операций, которые должны выполняться параллельно.

Другой ветвью развития архитектуры RISC является архитектура VLIW (Very long instruction word, очень длинная машинная команда) – архитектура процессоров с несколькими вычислительными устройствами или линиями конвейера.

Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно.

Так же, как в RISC, в инструкции VLIW явно указывается, что именно должен делать каж-дый модуль процессора.

Из–за этого длина инструкции может достигать 128 или даже 256 бит.

В ранних моделях суперскалярных процессоров также есть несколько вычислительных модулей, но в ранних моделях таких процессоров задача распределения работы между модулями решалась аппаратно.

Это сильно усложняет структуру процессора, и может быть чревато ошибками.

ИЛИ

MISC-процессоры

Minimum Instruction Set Computer — вычисления с минимальным набором команд. Дальнейшее развитие идей команды Чака Мура, который полагает, что принцип простоты, изначальный для RISC-процессоров, слишком быстро отошёл на задний план. В пылу борьбы за максимальное быстродействие, RISC догнал и перегнал многие CISC процессоры по сложности. Архитектура MISC строится на стековой вычислительной модели с ограниченным числом команд (примерно 20-30 команд).

VLIW-процессоры

VLIW (Very long instruction word) – архитектура процессоров с несколькими вычислительными модулями. Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно. В суперскалярных процессорах также есть несколько вычислительных модулей, но задача распределения между ними работы решается аппаратно. Это сильно усложняет дизайн процессора, и может быть чревато ошибками.

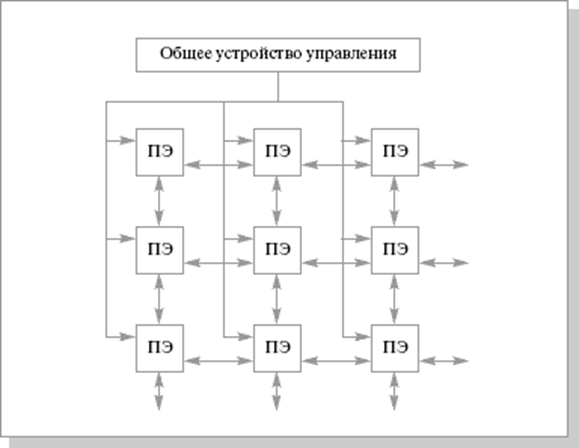

34.Матричные процессоры (на примере системы SOLOMON)

Матричный процессор — процессор ЭВМ,

представляющий собой сеть, состоящую из более простых процессоров, обладающих своей собственной памятью, работающих параллельно и обменивающихся информацией со своими ближайшими соседями.

Система SОLOМОN содержит 1024 процессорных элемента, соединены в виде матрицы: 32х32. Каждый процессорный элемент матрицы включает в себя процессор, обеспечивающий выполнение последовательных поразрядных арифметических и логических операций, а также оперативное ЗУ, емкостью 16 Кбайт. По каналам связи от устройства управления передаются команды и общие константы. В процессорном элементе используется многомодальная логика. В каждый момент все активные процессорные элементы выполняют одну и ту же операцию над данными, хранящимися в собственной памяти и имеющими один и тот же адрес.

35.Идея многомодальности. Многомодальная логика

Идея многомодальности: в каждом процессорном элементе имеется специальный регистр на 4 состояния - регистр моды. Мода заносится в этот регистр от устройства управления. При выполнении последовательности команд модальность передается в коде операции и сравнивается с содержимым регистра моды. Если есть совпадения, то операция выполняется. В зависимости от кода процессорный элемент может пересылать свои операнды соседнему процессорному элементу. Взаимодействуют процессорные элементы с периферийным оборудованием через внешний процессор.

Мультимодальная логика - это модальная логика, которая имеет более одного примитивного модального оператора. Она находит существенное применение в теоретической информатике.

Модальная логика - логика, в которой кроме стандартных логических связок, переменных и предикатов есть модальности (модальные операторы).

Логическая теория является модальной, если

· она содержит хотя бы три модальных оператора;

· из простой истинности или ложности высказывания нельзя заключить, какую именно модальную характеристику должна иметь устанавливаемая этим высказыванием связь;

· из квалификации высказывания с помощью слабого модального понятия не следует ни то, что высказывание истинно, ни то, что оно ложно;

· если высказыванию приписана слабая модальная характеристики, то его отрицанию должна быть приписана она же.

Модальные операторы используются для оценки истинности суждения.