Файл: Задача данной выпускной квалификационной работы (далее вкр) состоит в том, что необходимо настроить совместную работу платы ацпцап data Conversion hsmc и плис cyclone iv e, установленной на отладочную плату de2115.docx

Добавлен: 09.11.2023

Просмотров: 170

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

3.5 Подача тактовых импульсов на микросхему AD9254. Настройка и согласование генератора тактовых импульсов со входами микросхемы

На микросхему AD9254 можно подать самые разнообразные формы тактовых импульсов. На тактирующие входы можно подать импульсы формы CMOS, LVDS, LVPECL или даже обычный синусоидальный сигнал.

Независимо от формы тактирующих импульсов большое внимание нужно уделять их нестабильности.

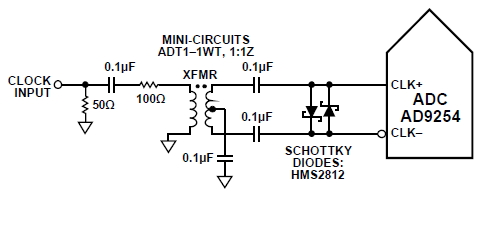

На рисунке 15 представлен один из наиболее предпочитаемых способов для подачи тактовых импульсов на микросхему AD9254 [3].

Источник тактовых импульсов с малой нестабильностью преобразуется из своей первоначальной формы в дифференциальный сигнал с помощью ВЧ-трансформатора. Далее диоды Шоттки задают размах для преобразованного дифференциального сигнала. Размах составляет 0,8 В. Это позволяет избежать подачу тактовых импульсов с избыточным напряжением на микросхему AD9254.

Рисунок 15 – Оптимальная схема для подачи тактовых импульсов на микросхему AD9254

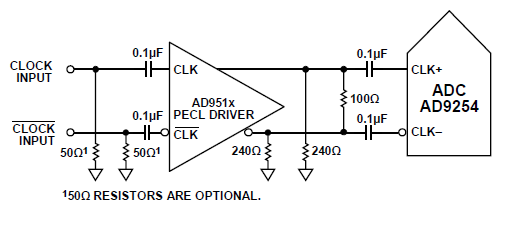

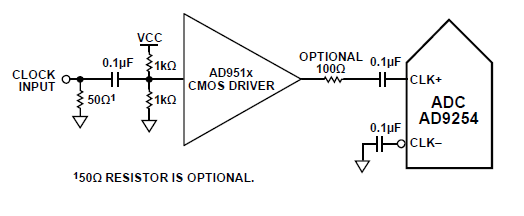

В случае, если параметр нестабильности тактового импульса не является важным, на микросхему AD9254 можно подать тактовые импульсы формы PECL. Для подачи такой формы тактовых импульсов используются драйверы семейства AD951. Схема представлена на рисунке 16 [3].

Рисунок 16 – Схема подачи тактовых импульсов формы PECL на микросхему AD9254

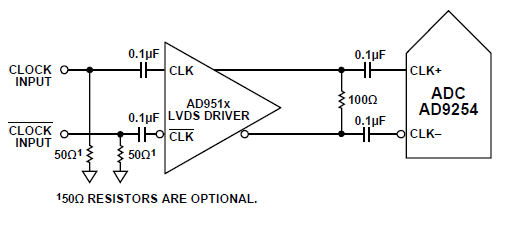

Для подачи тактовых импульсов формы LVDS на микросхему AD9254 также используются драйверы семейства AD951. Схема подачи тактовых импульсов формы LVDS представлена на рисунке 17 [3].

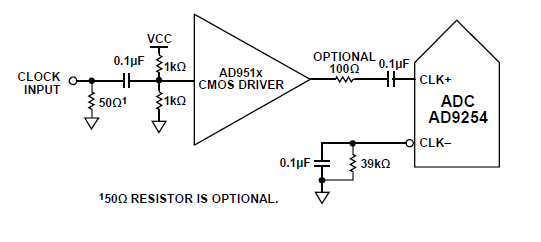

Также на микросхему AD9254 возможно подать тактовые импульсы формы CMOS. На контакт CLK + можно подать напрямую тактовые импульсы из выхода микросхемы серии AD951. Так как вход CLK (+) напрямую управляется микросхемой серии AD951, на него можно подать тактовый импульс напряжением до 3,6 В.

Для подачи тактовых импульсов напряжением до 1,8 В к контакту CLK (-) необходимо подключить RC-контур из конденсатора емкостью 0,1 мкФ и резистора сопротивлением 39 кОм. Схема данного подключения представлена на рисунке 18 [3].

Рисунок 17 – Схема подачи тактовых импульсов формы LVDS на микросхему AD9254

Рисунок 18 – Схема подачи тактовых импульсов напряжением до 1,8 В на микросхему AD9254

Если же требуется подключить к микросхеме тактовые импульсы напряжением до 3,3 В, необходимо к контакту CLK (-) подключить конденсатор емкостью 0,1 мкФ. Схема данного подключения представлена на рисунке 19 [3].

Рисунок 19 – Схема подачи тактовых импульсов напряжением до 3,3 В на микросхему AD9254

3.6 Стабилизация циклов тактовых импульсов

Как и любой другой высокоскоростной АЦП, AD9254 имеет внутренний стабилизатор циклов тактовых импульсов (DCS – Duty Clock Stabilizer). Обычно, стабилизатор восстанавливает тактовые импульсы в пределах допуска 5%.

Синхронизация тактовых импульсов происходит тогда, когда тактовый импульс еще не поступил на входы АЦП, либо на заднем фронте тактового импульса.

Минимальная частота тактовых импульсов, при которой стабилизатор может работать в нормальном режиме, составляет 20 МГц. Ниже этого значения он будет работать некорректно.

Также стоит отметить, что время на стабилизацию тактовых импульсов при изменении их частоты достаточно велико — от 1,5 мкс до 5 мкс. При изменении частоты тактовых импульсов стабилизатор работать не будет.

Есть также возможность отключить или включить стабилизатор тактовых импульсов. Это осуществляется путем настройки микросхемы AD9254 через SPI-интерфейс.

3.7 Влияние частоты аналогового сигнала на параметр SNR

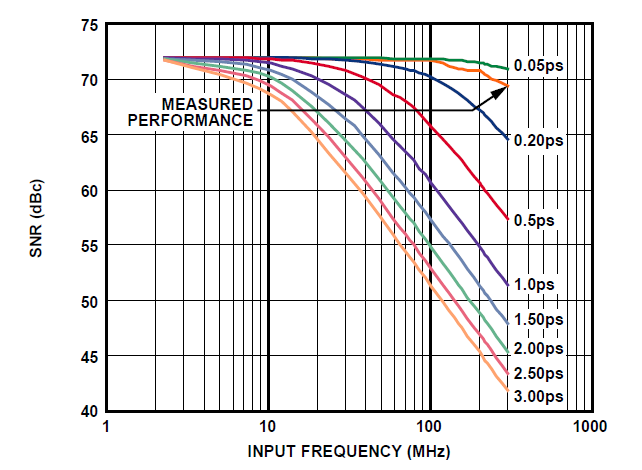

Высокая скорость и высокое разрешение оказывают большое влияние на преобразование сигнала из аналоговой формы в цифровую. Параметр SNR зависит от частоты аналогового сигнала и от времени смещения тактовых импульсов. Параметр SNR у АЦП рассчитывается по следующей формуле:

где

SNR – отношение сигнал/шум;

– частота аналогового сигнала;

– частота аналогового сигнала; – время смещения тактовых импульсов.

– время смещения тактовых импульсов.На рисунке 20 представлен график зависимости отношения сигнал/шум от частоты аналогового сигнала

и от времени смещения тактовых импульсов

и от времени смещения тактовых импульсов  [3].

[3].

Рисунок 20 – График зависимости отношения сигнал/шум от частоты аналогового сигнала и от времени смещения тактовых импульсов

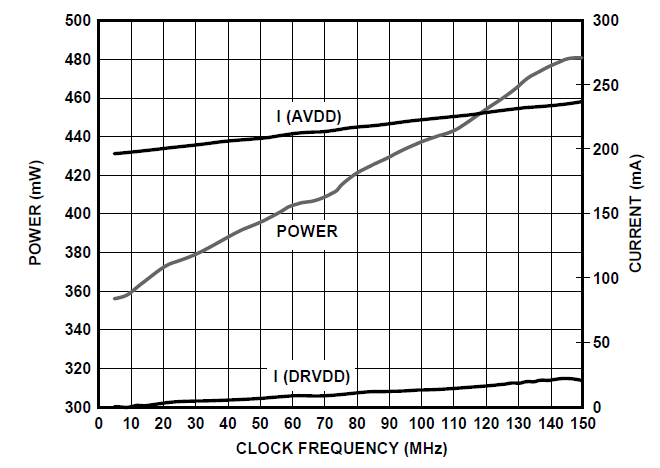

3.8 Рассеиваемая мощность

Немало важным фактором является и рассеиваемая мощность. В процессе преобразования сигнала на микросхеме AD9254 выделяется тепловая энергия. По большей части она выделяется из-за преобразования уже оцифрованных данных драйвером цифрового питания под конкретное значение напряжения VDRVDD. Значение этого напряжения можно настроить на 1,8 В, 2,5 В и 3,3 В. В процессе преобразования оцифрованного сигнала под заданное напряжение величина тока IDRVDD может изменяться по следующей формуле:

где

– величина образующегося тока при преобразовании данных под напряжение драйвера;

– величина образующегося тока при преобразовании данных под напряжение драйвера; – величина напряжения. под которое оцифрованный сигнал преобразуется драйвером;

– величина напряжения. под которое оцифрованный сигнал преобразуется драйвером; – величина емкости на выходе из драйвера цифрового питания;

– величина емкости на выходе из драйвера цифрового питания; – Частота тактового импульса

– Частота тактового импульсаN – номер бита.

Из формулы, приведенной выше, можно сделать вывод о том, что величина тока

зависит от частоты тактовых импульсов и от значения напряжения уже преобразованного бита. Величины

зависит от частоты тактовых импульсов и от значения напряжения уже преобразованного бита. Величины  и

и  остаются неизменными, т. к. их значения настраиваются заранее перед преобразованием сигнала. На рисунке 21 представлен график зависимости величины тока

остаются неизменными, т. к. их значения настраиваются заранее перед преобразованием сигнала. На рисунке 21 представлен график зависимости величины тока  и рассеиваемой мощности в зависимости от частоты тактовых импульсов [3].

и рассеиваемой мощности в зависимости от частоты тактовых импульсов [3].

Рисунок 21 – График зависимости величины тока

и рассеиваемой мощности в зависимости от частоты тактовых импульсов

и рассеиваемой мощности в зависимости от частоты тактовых импульсов3.9 Режим низкого энергопотребления микросхемы AD9254

Микросхему AD9254 можно перевести в режим низкого энергопотребления. В этом режиме микросхема будет потреблять всего 1,8 мВ. В режиме низкого энергопотребления драйверы цифрового питания переходят в состояние высокого импеданса. В рабочем режиме драйверы цифрового питания осуществляют преобразование оцифрованных сигналов под напряжение 1,8 В, 2,5 В и 3,3 В.

Низкое энергопотребление достигается благодаря тому, что внутри микросхемы прекращаются операции по подаче тактовых импульсов, по подаче опорного напряжения на микросхему и по буферизации данных.

Режим низкого энергопотребления можно включить путем настройки микросхемы через SPI-интерфейс.

3.10 Работа и настройка микросхемы AD9254 с помощью

SPI-интерфейса

Настройка микросхемы осуществляется с помощью SPI-интерфейса. У каждого регистра есть свой адрес, а также биты, отвечающие за тот или иной настраиваемый параметр.

Каждый регистр имеет свой 8-битный адрес. Условно, по своему назначению регистры можно разделить на 5 групп:

-

настройка конфигурации регистров: определяется порядок подачи битов со старшего разряда или с младшего; -

просмотр ID-адреса чипа микросхемы: микросхема имеет свой уникальный ID-адрес. Данный регистр предназначен только для чтения; -

оценка частоты дискретизации АЦП; -

синхронизация работы главного регистра (Master) и подчиненного (Slave): осуществляется синхронная работа между главным и подчиненным регистрами. -

настройка АЦП по параметрам: осуществляется настройка АЦП по опорному напряжению; по цифровому напряжению; по поправкам по измерениям; по режиму питания АЦП; по формату данных, выводящихся с АЦП и т. д.

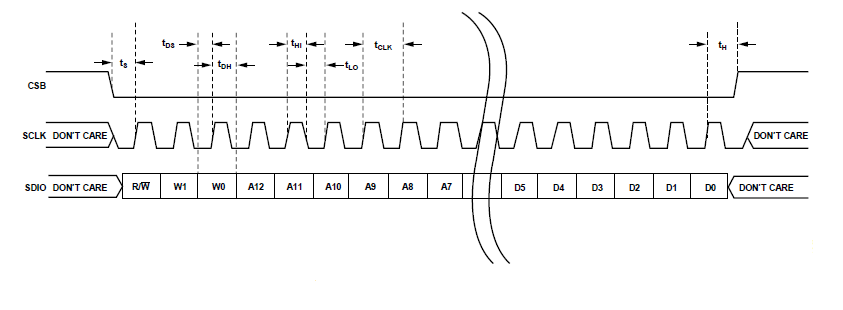

Рассмотрим принцип передачи данных с помощью регистров в SPI-интерфейсе. Структура регистров для работы с SPI-интерфейсом представлена на рисунке 22 [3].

Суть SPI-интерфейса состоит в следующем. У микросхемы AD9254 есть контакт CSB (Cheap Select Bar), который отвечает за разрешение или за запрет передачи данных. Если на вход CSB подать тактовый сигнал, т. е. логическую единицу, то на передачу данных будет наложен запрет. Если же не подавать тактовый импульс на вход CSB, то на микросхему можно будет записать данные.

Рисунок 22 – Структура регистров в SPI-интерфейсе

Вход SCLK (Serial Clock) отвечает за тактирование подчиненных регистров, которые расположены в микросхеме.

Вход/выход SDIO (Serial Data Input/Output) отвечает за ввод/вывод данных. Данные имеют следующую структуру:

-

бит R/W (чтение/запись). Этот бит переводит микросхему в режим чтения или записи. Если подать на него 1, то микросхема перейдет в режим записи. Если же подать 0, то микросхема перейдет в режим чтения. -

биты W1 и W2. Данные биты дают разрешение на чтение определенного количества битов:

-

00 — чтение одного байта информации; -

01 — чтение двух байтов информации; -

10 — чтение трех байтов информации; -

11 — чтение четырех байтов информации.

-

биты A12 – A0 предназначены для передачи информации об адресе регистра в микросхеме AD9254. -

биты D7 – D0 содержат в себе информацию для настройки АЦП.

С помощью SPI-интерфейса возможно устанавливать следующие настройки АЦП:

-

режимы питания АЦП: возможность настроить АЦП в режим отключения питания или в режим нормальной работы; -

тактирование: Стабилизация и синхронизация циклов передачи данных; -

корректировка измерений: корректировка преобразованных битов в зависимости от погрешности результатов; -

тестирование в режиме входа и в режиме выхода; -

выбор формата выходных данных из АЦП: данные из АЦП можно вывести в двоичном коде, дополнительном двоичном коде и в коде Грея; -

инверсия выходных данных из АЦП; -

настройка опорного напряжения.

Однако для того, чтобы работать через SPI-интерфейс с микросхемой AD9254 нужно также знать временные интервалы для правильной подачи данных на АЦП. Временные интервалы бывают следующих видов:

-

– время установки между подачей данных и подачей тактового импульса на входе SCLK;

– время установки между подачей данных и подачей тактового импульса на входе SCLK; -

– время задержки между началом подачи тактового импульса битом данных;

– время задержки между началом подачи тактового импульса битом данных; -

– период тактового импульса;

– период тактового импульса; -

– время задержки между окончанием открытия входа CSB и подачей тактового импульса SCLK;

– время задержки между окончанием открытия входа CSB и подачей тактового импульса SCLK; -

– время между окончанием подачи тактового импульса SCLK и закрытием входа CSB;

– время между окончанием подачи тактового импульса SCLK и закрытием входа CSB; -

– минимальная длительность импульса, при которой он будет восприниматься, как логическая единица;

– минимальная длительность импульса, при которой он будет восприниматься, как логическая единица; -

– минимальное время, за которое тактовый импульс будет восприниматься, как логический ноль.

– минимальное время, за которое тактовый импульс будет восприниматься, как логический ноль.