Файл: Задача данной выпускной квалификационной работы (далее вкр) состоит в том, что необходимо настроить совместную работу платы ацпцап data Conversion hsmc и плис cyclone iv e, установленной на отладочную плату de2115.docx

Добавлен: 09.11.2023

Просмотров: 175

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

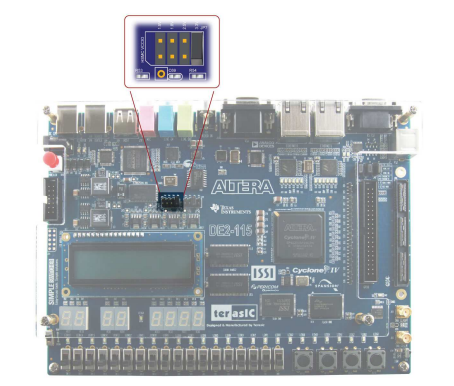

Рисунок 28 – Положение перемычки JP6 на плате DE2-115

В таблице 14 представлено назначение контактов перемычки JP6.

Таблица 14 – Назначение контактов перемычки JP6

| Замкнутые контакты | Режим работы драйвера цифрового питания |

| Контакты 1 и 2 | 1,5 В |

| Контакты 3 и 4 | 1,8 В |

| Контакты 5 и 6 | 2,5 В |

| Контакты 7 и 8 | 3,3 В |

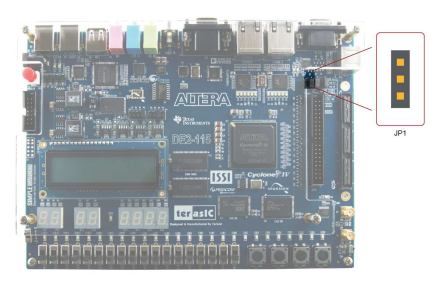

К третьей группе относятся перемычки JP1 и JP2. Они отвечают за выбор режима работы в стандарте Ethernet. Их расположение на плате показано на рисунке 29 [4].

Рисунок 29 – Расположение перемычек JP1 и JP2 на плате DE2-115

Назначение контактов перемычек JP1 и JP2 представлено в таблице 15.

Таблица 15 – Назначение контактов перемычек JP1 и JP2

| Замкнутые контакты | Режим работы в стандарте Ethernet |

| Контакты 1 и 2 | Режим RGMII |

| Контакты 2 и 3 | Режим MII |

4.4 Поставляемое ПО совместно с платой DE2-115

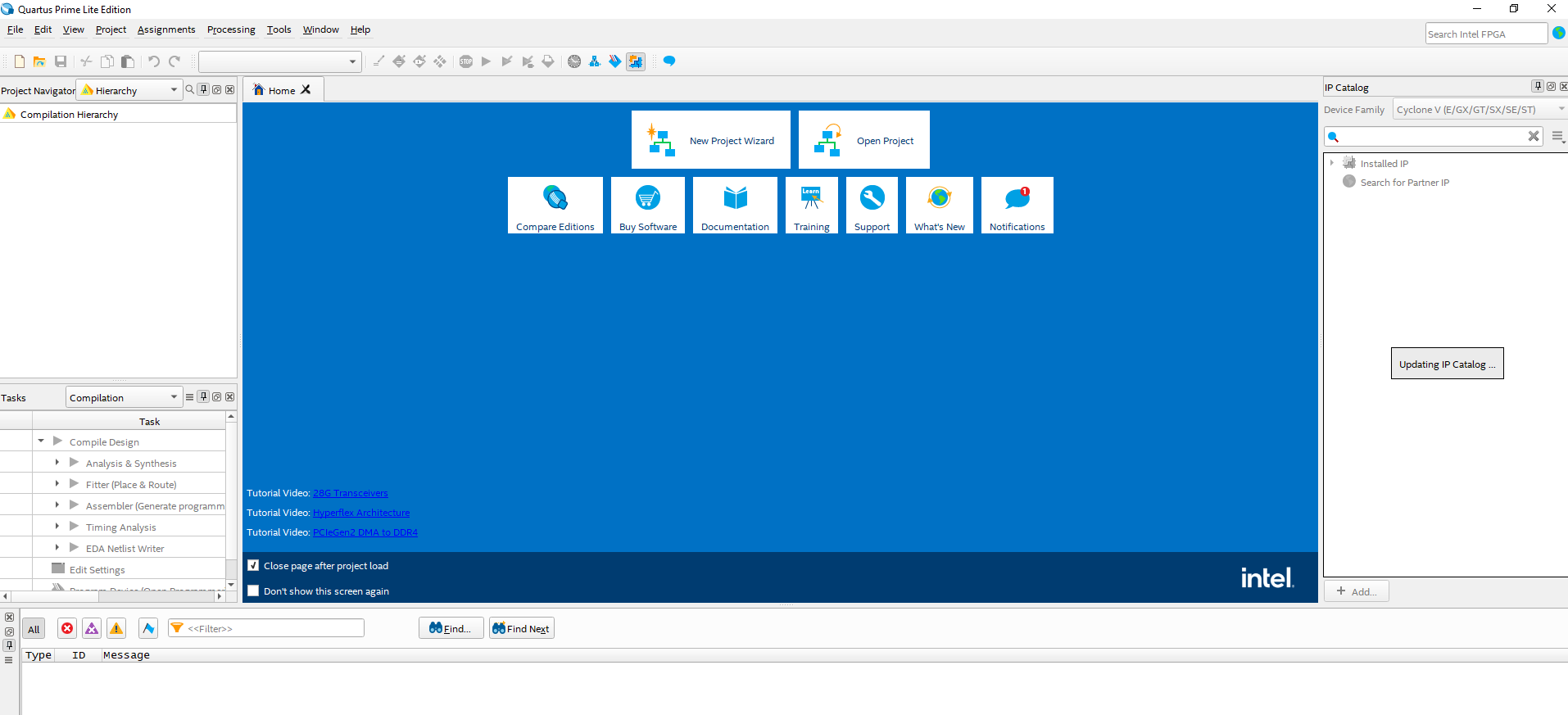

Разработка проектов ПЛИС для платы DE2-115 осуществляется с помощью ПО Quartus Prime, интерфейс которой представлен на рисунке 29.

Рисунок 29 – Рабочая среда Quartus Prime для разработки проектов ПЛИС

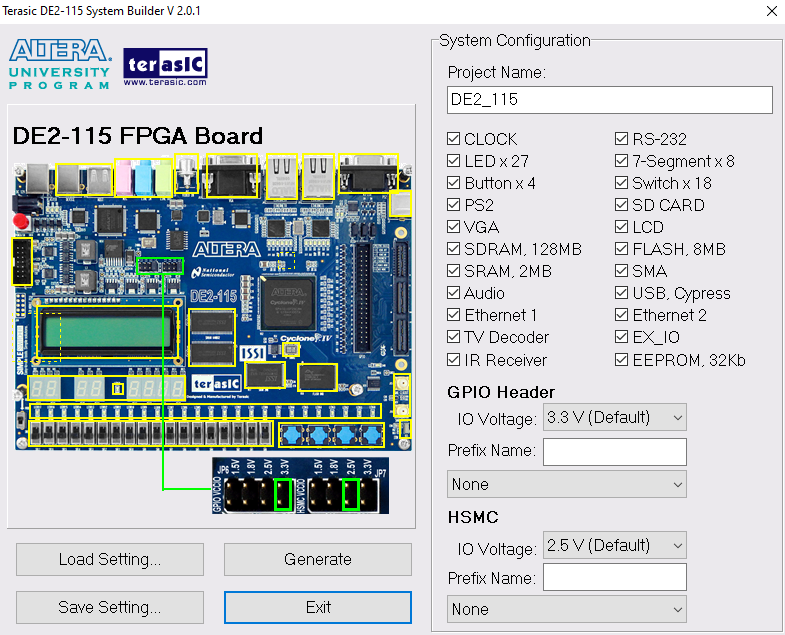

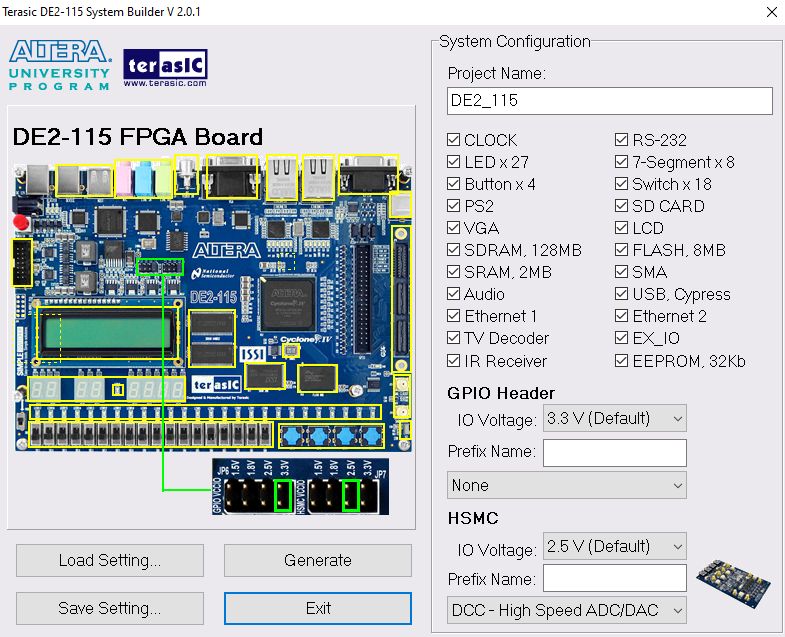

Однако, стоит заметить, что Quartus Prime – это далеко не единственная программа, с помощью которой возможно разрабатывать проекты ПЛИС. В комплекте с платой DE2-115 также поставляется и дополнительное ПО. Одной из таких программ является DE2-115 System Builder. Это ПО можно установить, посетив официальный сайт производителя TerASIC. Данное ПО позволяет в кратчайшие сроки разработать простые проекты ПЛИС. Интерфейс данной рабочей среды представлен на рисунке 30.

Рисунок 30 – Рабочая среда DE2-115 System Builder

В программе DE2-115 System Builder представлен внешний вид платы DE2-115 с обозначенными на ней элементами

, которые уже описывались в одном из предыдущих разделов. В данном ПО есть возможность подключать элементы платы к ПЛИС или отключать их подсоединение от нее.

Также есть возможность регулировать драйвер цифрового питания на GPIO-разъеме и на HSMC-разъеме. Однако, стоит заметить, что без переключения соответствующих перемычек драйверы цифрового питания не смогут переключиться самостоятельно.

Можно также задавать сразу же через эту программу название проекта ПЛИС.

Существует возможность создавать проекты ПЛИС для устройств, подключаемых через HSMC-разъем от компании TerASIC. Для этого нужно нажать на кнопку None во вкладке HSMC и выбрать соответствующее устройство. Исключением не является и плата АЦП-ЦАП Data Conversion HSMC, ее тоже можно выбрать в этой программе для разработки проекта ПЛИС, что и показано на рисунке 31.

Рисунок 31 – Выбор платы АЦП-ЦАП Data Conversion HSMC для разработки проекта ПЛИС в среде DE2-115 System Builder

Как видно из рисунка 31, в этой программе, действительно, можно выбрать интересующую нас плату и создать готовый проект. После этого нужно нажать на кнопку Generate, и программа перенесет проект ПЛИС в среду Quartus Prime на языке программирования Verilog. Несмотря на простоту использования данного ПО, проект все равно нужно будет корректировать.

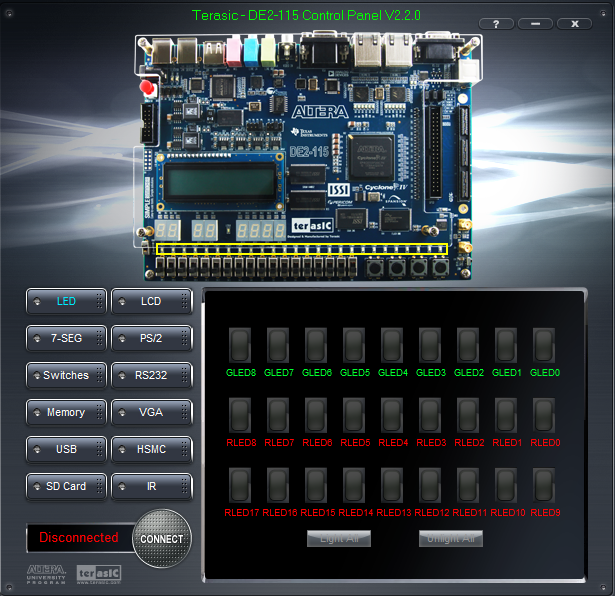

Еще одно программой, поставляемой совместно с платой DE2-115, является ПО DE2-115 Control Panel. Эта программа нужна для контроля процессов, происходящих на элементах платы DE2-115 С ее помощью можно контролировать процессы на светодиодах, LCD-дисплее, семи сегментных индикаторах, на переключателях, на SD-карте и на некоторых разъемах платы.

Интерфейс данной программы представлен на рисунке 32.

Рисунок 32 – Интерфейс программы DE2-115 Control Panel

Для работы с данным ПО необходимо подключить плату DE2-115 к персональному компьютеру через USB-разъем и загрузить проект ПЛИС на плату. Только после этого программа будет выдавать результаты контроля ее элементов.

5. Разработка проекта ПЛИС

5.1 Разработка тестового проекта для оценки возможности вывода данных с АЦП

Проект должен быть разработан таким образом, чтобы ПЛИС могла принимать данные с АЦП через HSMC-разъем. Также необходимо подавать тактовые импульсы с ПЛИС на АЦП.

Проект разрабатывался с помощью среды разработки DEEDS. Это бесплатное ПО. По своей сути это более интуитивно понятная версия Quartus Prime. Проект разрабатывается сначала в среде DEEDS, а затем экспортируется на языке программирования VHDL в среду Quartus Prime.

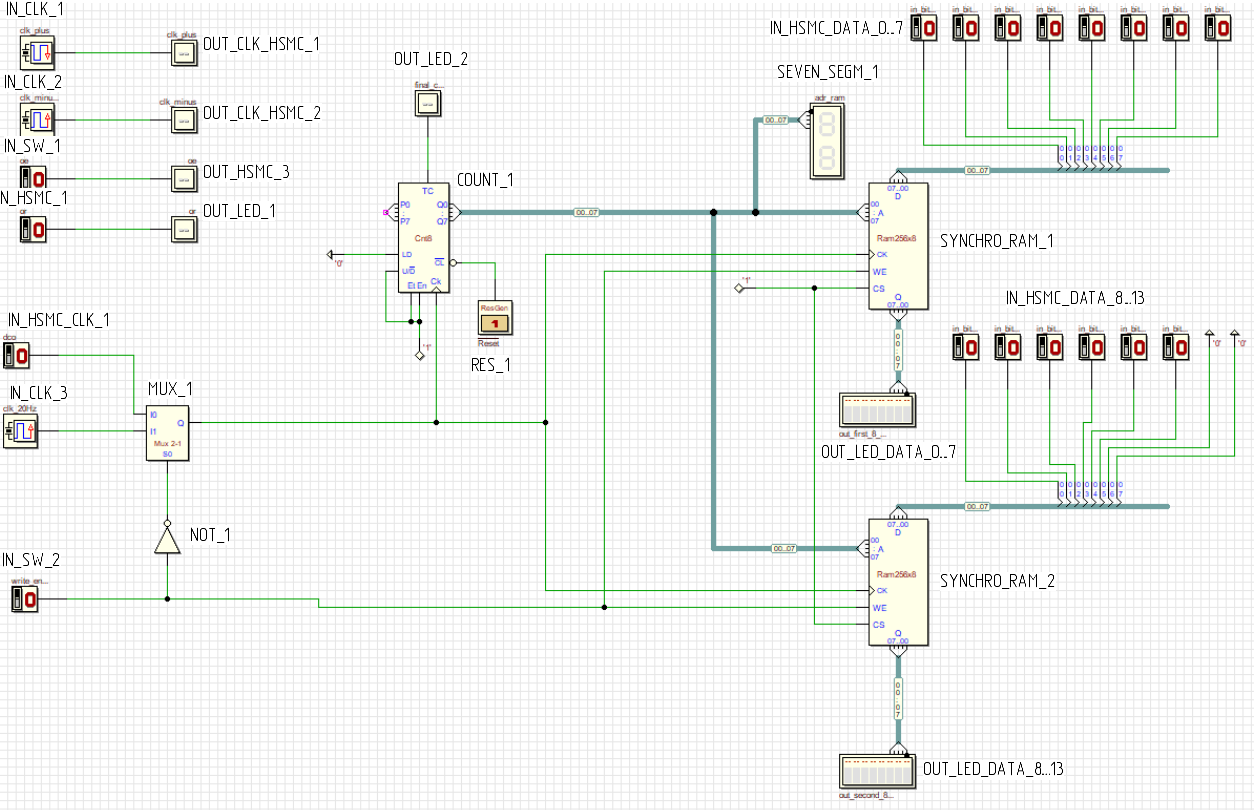

Схема тестового проекта ПЛИС, разработанная в среде DEEDS представлена на рисунке 33.

Рисунок 33 – Тестовый проект ПЛИС

Данная схема проекта работает в двух режимах.

При первом режиме работы переключатель IN_SW_1 подает логическую единицу на входы WE (Write Enable) у синхронизированных ячеек ОЗУ SYNCHRO_RAM_1 и SYNCHRO_RAM_2. Запись данных таким образом разрешается.

Эта же логическая единица также подается на элемент NOT_1, который инвертирует логическую единицу и подает ее на мультиплексор MUX_1. Этот мультиплексор отвечает за переключение генераторов тактовых импульсов для ячеек ОЗУ. Когда инвертированная единица подается с переключателя IN_SW_1 на мультиплексор MUX_1, то мультиплексор подключается к генератору тактовых импульсов IN_HSMC_1. Тактовые импульсы в этом случае подаются из HSMC-разъема из вывода DCO у АЦП. Эти тактовые импульсы подаются на входы CK (Clock) у ячеек оперативной памяти, а также на счетчик COUNT_1, который генерирует адреса в автоматическом режиме для ячеек ОЗУ. Все это в совокупности обеспечивает синхронную работу АЦП и ячеек ОЗУ.

Во втором режиме работы переключатель IN_SW_1 подает логический ноль на входы WE у синхронизированных ячеек ОЗУ SYNCHRO_RAM_1 и SYNCHRO_RAM_2. Запись данных таким образом запрещается, и ОЗУ переходит в режим чтения.

По аналогии с первым режимом работы этот же логический ноль инвертируется элементом NOT_1, и мультиплексор подключает генератор тактовых импульсов с частотой 2 Гц на счетчик COUNT_1 и на входы CK у ячеек оперативной памяти. Частота в 2 Гц выбрана таким образом, чтобы можно было посмотреть

, какие данные приходят с АЦП на ячейки ОЗУ.

Теперь рассмотрим остальные элементы схемы, которые еще не были описаны.

В схеме присутствуют также генераторы тактовых импульсов IN_CLK1 и IN_CLK2, которые подают дифференциальные тактовые импульсы на входы АЦП.

Элемент IN_SW_1 отвечает за разрешение АЦП на выдачу данных. Если подать на вход OE (Output Enable) логическую единицу, то АЦП не будет выводить свои данные с выводов D0 – D13.

Элемент IN_HSMC_1 – это вход с HSMC-разъема на плату ПЛИС. Он содержит в себе данные о выходе за пределы измерений. Если аналоговый сигнал находится на уровне выше или ниже уровня опорного напряжения VREF, то на светодиод OUT_LED_1 будет подаваться логическая единица.

Светодиод OUT_LED_2 загорается в тот момент, когда счетчик подал число 255 на адресные входы ячеек ОЗУ.

Элемент RES_1 является генератором сброса. Он сбрасывает счетчик, когда он уже подал число 255 на адресные входы ячеек ОЗУ.

Элемент SEVEN_SEGM_1 является семи-сегментным индикатором и выводит информацию о том, на какой адрес ячейки ОЗУ записывается информация или выводится из него.

Элементы IN_HSMC_DATA_0…7 и IN_HSMC_DATA_8…13 – это данные, которые приходят с АЦП через HSMC-разъем на плату ПЛИС.

Элементы OUT_LED_DATA_0…7 и OUT_LED_DATA_8…13 являются светодиодами, на которые выводится информация из ячеек ОЗУ.

5.2 Разработка проекта ПЛИС для вывода информации из АЦП на ЦАП

Ранее говорилось о том, что все остальные устройства на плате Data Conversion HSMC, являются вспомогательными, и позволяют оценить работу АЦП. Одним из таких устройств является ЦАП.

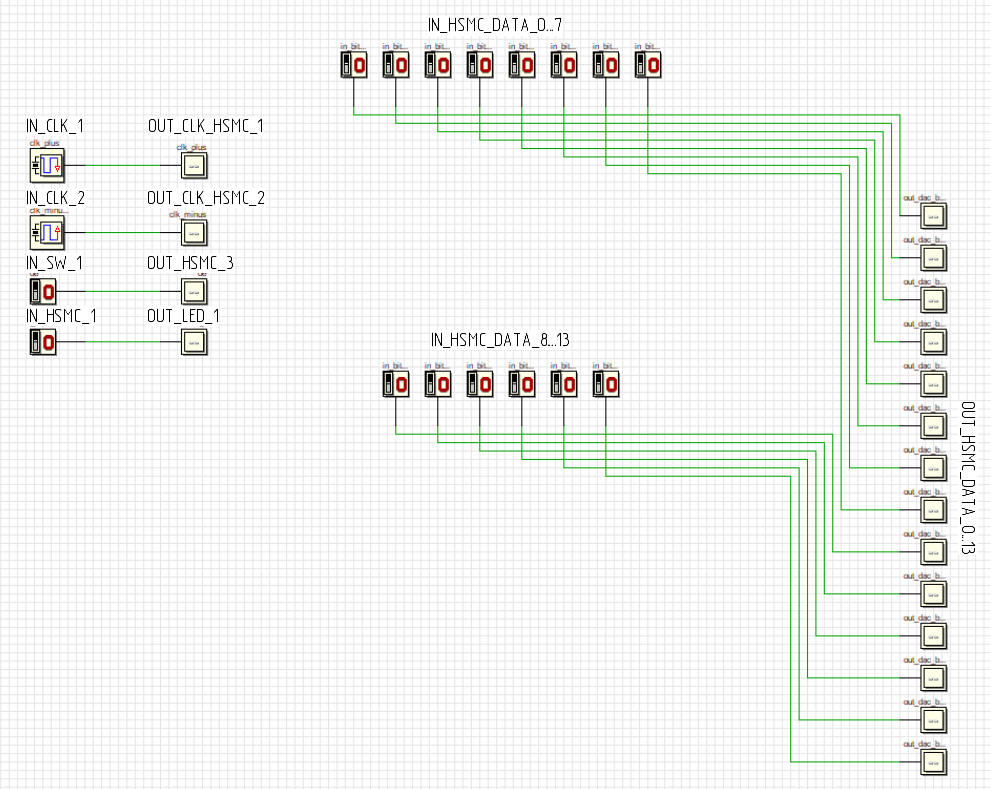

Для объективности оценки работы АЦП необходимо также разработать и проект ПЛИС, который позволяет направить данные от АЦП из HSMC-разъема в плату ПЛИС, а затем вывести эти данные на ЦАП. На рисунке 34 представлена схема проекта ПЛИС для вывода данных от АЦП на ЦАП.

В этом проекте, как и в тестовом, есть два генератора тактовых импульсов IN_CLK1 и IN_CLK2 которые подают импульсы в дифференциальной форме на АЦП.

Переключатель IN_SW_1 выполняет ту же функцию, что и в тестовом проекте.

Вход IN_HSMC_1 – это вход с HSMC-разъема на плату ПЛИС. Он так же, как и в тестовом проекте, будет содержать в себе данные о выходе за пределы измерений.

Элементы IN_HSMC_DATA_0…7 и IN_HSMC_DATA_8…13 – это данные, которые приходят с АЦП через HSMC-разъем на плату ПЛИС.

Выходы OUT_HSMC_DATA_0…13 направляют сигналы от АЦП в ЦАП.

Рисунок 34 – Схема проекта ПЛИС для вывода данных с АЦП на ЦАП